Fターム[5F083ER21]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 電気的に消去するもの(EEPROM) (2,068)

Fターム[5F083ER21]の下位に属するFターム

一括消去(フラッシュメモリ) (1,055)

ブロック消去 (331)

Fターム[5F083ER21]に分類される特許

41 - 60 / 682

半導体記憶装置

【課題】電荷蓄積層及び制御ゲートを有する半導体記憶装置のバックバイアス効果による影響を低減させることにより集積度を向上させ、占有面積を増加させずに浮遊ゲートと制御ゲートとの容量の比をより一層増大させるとともに、製造プロセスに起因するセル特性のばらつきが抑制された半導体記憶装置を提供する。

【解決手段】半導体基板と、少なくとも1つの島状半導体層110、該島状半導体層110の側壁の周囲の全部又は一部に形成された電荷蓄積層513及び制御ゲート523から構成される少なくとも1つのメモリセルとを有する半導体記憶装置であって、前記メモリセルの島状半導体層110が不純物拡散層により前記半導体基板から電気的に絶縁されてなる。

(もっと読む)

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】ワイドギャップ半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも

制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワ

イドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジス

タのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわた

って情報を保持することが可能である。また、信号線の電位変化のタイミングを、書き込

みワード線の電位変化のタイミングより遅らせる。これによって、データの書き込みミス

を防ぐことが可能である。

(もっと読む)

半導体装置

【課題】瞬断もしくは瞬時電圧低下等の極めて短時間の電源停止又は電源電圧低下の場合でさえ、揮発性メモリ内のデータが消失してしまう場合があった。そこで、高速データ処理のために揮発性メモリを用いた場合であっても、データの保持時間を延ばす。

【解決手段】容量素子及び酸化物半導体を用いたトランジスタを有するメモリに揮発性メモリのデータ内容をバックアップしておくことによって、データの保持時間を長くすることができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

半導体装置の駆動方法

【課題】半導体装置の駆動方法を提供する。

【解決手段】ビット線と、選択線と、選択トランジスタと、m(mは2以上の自然数)本の書き込みワード線と、m本の読み出しワード線と、ソース線と、第1乃至mのメモリセルと、を有する半導体装置において、メモリセルは、第1のトランジスタ、容量素子に蓄積された電荷を保持する第2のトランジスタを含み、第2のトランジスタは酸化物半導体層で形成されるチャネルを有する。上記構成の半導体装置の駆動方法において、メモリセルに書き込みを行う場合、第1のトランジスタを導通させて第1のソース端子または第1のドレイン端子を固定電位とし、容量素子に安定した電位の書き込みを行う。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

二重ゲート電極構造を含む半導体装置及びその製造方法

【課題】漏洩電流発生を最小化すると同時にオン電流(On current)を増加させ得る二重ゲート電極構造を含む半導体装置及びその製造方法が提供される。

【解決手段】本発明による半導体装置は、基板に配置されるゲート電極と、前記ゲート電極の両端に各々隣接するように前記基板に配置される第1不純物注入領域及び第2不純物注入領域と、前記第1不純物注入領域と前記第2不純物注入領域との間に配置されるチャンネル領域を含み、前記ゲート電極は前記第1不純物注入領域に隣接する第1サブゲート電極と前記第2不純物注入領域に隣接する第2サブゲート電極と、を含み、前記第1サブゲート電極と前記第2サブゲート電極とは前記チャンネル領域の上に配置される。この半導体装置では1つのチャンネル領域が2つのサブゲートによって独立的に制御されて漏洩電流発生を最小化できる。

(もっと読む)

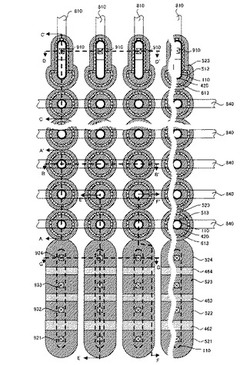

多層接続構造及びその製造方法

【課題】3次元積層ICデバイスにおいて、相互接続領域のコンタクトレベルのスタックへの電気接続形成工程を簡略化する製造方法を提供する。

【解決手段】各コンタクトレベルは導電層と絶縁層とを有する。コンタクト開口を作り出すために、第1のコンタクトレベルを露出させるように上部層の一部が除去される。N個のマスクを用いて、最大2N個のコンタクトレベルまでコンタクト開口がエッチングされる。各マスクは、コンタクト開口のうちの実効的に半数をエッチングするために使用される。Nが3であるとき、第1のマスクにより1つのコンタクトレベルがエッチングされ、第2のマスクにより2つのコンタクトレベルがエッチングされ、第3のマスクにより4つのコンタクトレベルがエッチングされる。コンタクト開口の側壁に誘電体層が形成され得る。コンタクト開口内に導電体が形成され、前記誘電体層が該導電体を前記側壁から電気的に絶縁する。

(もっと読む)

半導体装置

【課題】抵抗素子を有する半導体装置に関し、集積度を低下することなく低消費電力化と高い回路精度とを実現しうる半導体装置を提供する。

【解決手段】半導体材料により形成された複数の抵抗素子と、複数の抵抗素子の近傍に配置された加熱用抵抗素子と、対向する2つの接続ノード間に加熱用抵抗素子が接続され、対向する他の2つの接続ノード間に電源線が接続された抵抗ブリッジ回路とを有する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2

の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上

に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を

有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第

3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のド

ーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】ワードライン間の素子分離を行い、メモリセルの微細化が可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10内に形成されたビットライン14と、ビットライン14上にビットライン14の長手方向に連続して設けられた絶縁膜ライン18と、ビットライン14間の半導体基板10上に設けられたゲート電極16と、ゲート電極16上に接して設けられ、ビットライン14の幅方向に延在したワードライン20と、ビットライン14間でありワードライン20間の半導体基板に形成されたトレンチ部22と、を具備する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】 2層構造のビットライン配線において、製造工程を減少することができる半導体記憶装置及びその製造方法を提供する。

【解決手段】 実施形態に係る半導体記憶装置は、半導体基板を持つ。前記半導体基板上に第1及び第2のコンタクトプラグが設けられる。前記第1のコンタクトプラグに接する第1のビットラインが設けられ、前記第2のコンタクトプラグ上には第2のビットラインが設けられる。前記第1のコンタクトプラグは、前記第1のビットラインの上面と接し、かつ前記第2のビットラインと電気的に絶縁しており、前記第2のビットラインの底面の高さは、前記第1のビットラインの上面よりも高い。

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】電気的特性の安定した酸化物半導体膜を用いることにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供すること。また、結晶性の高い酸化物半導体膜を用いることにより、移動度の向上した半導体装置を提供すること。

【解決手段】表面粗さの低減された絶縁膜上に接して、結晶性を有する酸化物半導体膜を形成することにより、電気的特性の安定した酸化物半導体膜を形成することができる。これにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供することができる。さらに、移動度の向上した半導体装置を提供することができる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、酸化物半導体膜に酸素ドープ処理を行い、その後、酸化物半導体膜及び酸化物半導体膜上に設けられた酸化アルミニウム膜に対して熱処理を行うことで、化学量論的組成比を超える酸素を含む領域を有する酸化物半導体膜を形成する。該酸化物半導体膜を用いたトランジスタは、バイアス−熱ストレス試験(BT試験)前後においてもトランジスタのしきい値電圧の変化量が低減されており、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体装置の製造方法

【課題】実施形態によれば、メモリストリングの下端を連結する構造を少ない工程数で形成することができる半導体装置の製造方法を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、シリコンを含む下地層にマスクを用いて選択的に不純物を注入し、下地層に、ホウ素を含むホウ素添加領域と、ホウ素添加領域よりもホウ素濃度が低い被エッチング領域とを形成する工程を有する。また、複数層の電極層を含む積層体に、被エッチング領域に達する一対のホールを形成する工程を有する。また、エッチング液を用いて被エッチング領域をホールを通じて除去し、下地層に、一対のホールのそれぞれの下端とつながった凹部を形成する工程を有する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】記憶密度を高めた不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1、2積層体、第1、2半導体ピラー、及び分断絶縁層を備えた不揮発性半導体記憶装置が提供される。第1、2積層体は、第1軸に沿って積層された複数の第1、2電極膜と、第1、2電極膜の間の第1、2電極間絶縁膜と、を含み、第1軸に沿う第1、2貫通ホールが設けられる。第2積層体は、第1軸と直交する第2軸に沿って第1積層体と並ぶ。第1、2半導体ピラーは第1、2貫通ホールに埋め込まれる。分断絶縁層は第1、2電極膜を分断する。第1、2貫通ホールの分断絶縁層の側の側面は、第1、2軸に直交する第3軸を含み第1軸を含む平面と平行な部分を有する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

41 - 60 / 682

[ Back to top ]