Fターム[5F083ER21]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 電気的に消去するもの(EEPROM) (2,068)

Fターム[5F083ER21]の下位に属するFターム

一括消去(フラッシュメモリ) (1,055)

ブロック消去 (331)

Fターム[5F083ER21]に分類される特許

81 - 100 / 682

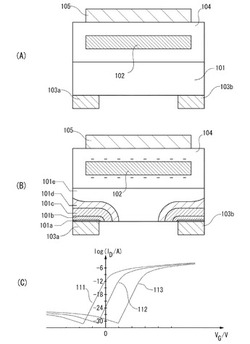

電界効果トランジスタおよび半導体装置の作製方法

【課題】導体半導体接合を用いた電界効果トランジスタのゼロ電流を低減せしめる構造を提供する。

【解決手段】半導体層101とゲート105の間に、絶縁物104により周囲を覆われた導体もしくは半導体よりなり、半導体層101を横切るように形成されたフローティング電極102を形成し、これを帯電させることにより、ソース電極103aやドレイン電極103bからのキャリアの流入を防止する。このため半導体層101中のキャリア濃度を十分に低く維持でき、よって、ゼロ電流を低減できる。

(もっと読む)

半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな駆動方法を提供する。また、新たな駆動方法により、メモリ素子への書き込み電位のばらつきを低減し、信頼性を向上させる。

【解決手段】半導体装置の駆動方法において、書き込み電位を段階的に上昇させて、同時に読み出し電流を確認し、読み出し電流の結果を書き込み電位に利用して書き込みを行う。つまり、正しい電位で書き込みが行われたか確認しながら書き込みを行うことで、信頼性の高い書き込みを行うことが可能である。

(もっと読む)

半導体装置

【課題】小型化が可能な不揮発性メモリを備えた半導体装置を提供する。

【解決手段】基板901上に画素と不揮発性メモリとを備え、不揮発性メモリは、基板901上に形成される半導体活性層と、半導体活性層上に形成される絶縁膜923と、絶縁膜923上に形成されるフローティングゲイト電極907と、フローティングゲイト電極907を酸化して得られる酸化膜908,915,922と、酸化膜908,915,922に接して形成されるコントロールゲイト電極929と、を備え、画素と不揮発性メモリとは、基板901上に一体形成される。

(もっと読む)

スイッチアレイ

【課題】 スイッチアレイの占有面積の縮小を図る。

【解決手段】本実施形態のスイッチアレイは、基板上に設けられる2つのスイッチと、第1の方向に延在する第1及び第2の制御線と、を具備し、スイッチのそれぞれは、メモリセルトランジスタが設けられる第1のアクティブ領域と、パストランジスタが設けられる第2のアクティブ領域と、を含み、アクティブ領域内でトランジスタのチャネル長方向に隣接するメモリセルトランジスタはソース又はドレインを共有し、第1及び第2のアクティブ領域は、トランジスタのチャネル幅方向に互いに隣接している。

(もっと読む)

半導体不揮発性メモリ

【課題】 本発明は、不揮発性メモリ・セルにおける電荷貯蔵層を論理工程において形成する方法を提供する。

【解決手段】 論理工程において不揮発性メモリ・セルにおける電荷貯蔵層を形成する方法は、基板のアクティブ領域の上にセレクト・ゲートを形成するステップ、その基板のアクティブ領域に部分的に重なる長いポリシリコン・ゲートを形成するステップ、及びその長いポリシリコン・ゲートの間に電荷貯蔵層を充填するステップを含む。

(もっと読む)

半導体装置

【課題】メモリセルの保持データが多値化された場合であっても正確なデータを保持することが可能なメモリセルを有する半導体装置を供給すること。

【解決手段】半導体装置に、酸化物半導体によってチャネル領域が形成されるトランジスタのソース及びドレインの一方が電気的に接続されたノードにおいてデータの保持を行うメモリセルを設ける。なお、当該トランジスタのオフ電流(リーク電流)の値は、極めて低い。そのため、当該ノードの電位を所望の値に設定後、当該トランジスタをオフ状態とすることで当該電位を一定又はほぼ一定に維持することが可能である。これにより、当該メモリセルにおいて、正確なデータの保持が可能となる。

(もっと読む)

記憶装置、半導体装置

【課題】長い期間においてデータの保持が可能な記憶装置を提供する。

【解決手段】記憶素子と、上記記憶素子における電荷の供給、保持、放出を制御するためのスイッチング素子として機能するトランジスタとを有する。上記トランジスタは、通常のゲート電極の他に、閾値電圧を制御するための第2のゲート電極が備えられており、また、活性層に酸化物半導体を含むためにオフ電流が極めて低い。上記記憶装置では、絶縁膜に囲まれたフローティングゲートに高電圧で電荷を注入するのではなく、オフ電流の極めて低いトランジスタを介して記憶素子の電荷量を制御することで、データの記憶を行う。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択的に消去動作を実行可能な不揮発性半導体記憶装置を提供する。

【解決手段】制御回路は、選択メモリブロック内の選択セルユニットに対して第1メモリトランジスタに蓄積された電荷を放出する消去動作を実行する一方、選択メモリブロック内の非選択セルユニットに対して消去動作を禁止するように構成されている。制御回路は、消去動作時、選択セルユニットに含まれる第1メモリトランジスタのボディの電圧を第1電圧まで上げ、非選択セルユニットに含まれる第1メモリトランジスタのボディの電圧を第1電圧よりも低い第2電圧に設定すると共に、選択セルユニット及び非選択セルユニットに含まれる第1メモリトランジスタのゲートに第2電圧以下の第3電圧を印加する。

(もっと読む)

不揮発性プログラマブルロジックスイッチおよび半導体集積回路

【課題】回路サイズを減少させることを可能にする。

【解決手段】素子分離領域102によって分離された、隣接する第1導電型の第1半導体領域101aおよび第2導電型の第2半導体領域101cと、第1半導体領域101a上に設けられた不揮発性メモリセルトランジスタ10と、第2半導体領域101c上に設けられ、第1半導体領域101aに設けられた第1ドレイン領域10bと電気的に接続されたゲート電極20C2とを有するパストランジスタ20と、第1半導体領域101aに設けられ第1半導体領域に基板バイアスを印加する第1電極8と、第2半導体領域101cに設けられ第2半導体領域に基板バイアスを印加する第2電極9と、を備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板の結晶性の悪化を招くことなく、素子分離トレンチの幅を小さくできる半導体装置の製造方法を提供する。

【解決手段】マスク用窒化膜51およびパッド酸化膜52からなるハードマスクを用いて、シリコン基板2がエッチングされることにより、素子分離トレンチ21が形成される。素子分離トレンチ21の内面に熱酸化法によりライナー酸化膜22が形成される。続いて、半導体基板2を窒素雰囲気中に配置して、半導体基板2が熱処理される。熱処理後に、エッチングにより、ライナー酸化膜22が薄膜化される。そして、HDP−CVD法により、絶縁物23が素子分離トレンチ21内に埋め込まれる。

(もっと読む)

不揮発性メモリのゲートのパターニング方法

【課題】不揮発性メモリ(NVM)領域及び前記NVM領域と重ならないよう非NVM領域を有する半導体基板の上にNVMのゲートスタックを形成する。

【解決手段】

上記の製造方法は、半導体基板上のNVM領域及び非NVM領域に選択ゲート層を形成する工程と、NVM領域及び非NVM領域における選択ゲート層を同時にエッチングする工程と、NVM領域及び非NVM領域における半導体基板上に電荷蓄積層を形成する工程と、NVM領域及び非NVM領域における電荷蓄積層上に制御ゲート層を形成する工程と、NVM領域及び非NVM領域における電荷蓄積層を同時にエッチングする工程とを備える。NVM領域における選択ゲート層をエッチングする工程は、電荷蓄積層の部分が選択ゲート層の第1部分上にあり、かつ選択ゲート層の第1部分の側壁と重なるように行い、かつ、制御ゲート層の部分を電荷蓄積層の部分上にあるように行う。

(もっと読む)

半導体装置、及び半導体装置の駆動方法

【課題】データの書込みにおいて、電源電位を増やすことなく電圧を低減することで低消費電力化が実現された半導体装置を提供する。さらにデータの書込みにおいて、電源電位を増やすことなく選択トランジスタにおけるしきい値落ちの問題が抑制された半導体装置を提供する。

【解決手段】nチャネル型の選択トランジスタのゲートに電気的に接続するワード線に直列にダイオード電気的に接続されたトランジスタを電気的に接続し、さらに当該選択トランジスタのソース又はドレインの一方に電気的に接続するビット線と、ワード線との間に容量素子を設ける、またはビット線とワード線との線間容量を利用する。さらに書込みにおいて、ワード選択のタイミングをビット選択のタイミングよりも早くする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】第1のトランジスタ160と、第2のトランジスタ162と、第1のトランジスタ160のソース領域またはドレイン領域120と、第2のトランジスタ162のチャネル形成領域144との間に設けられた絶縁層128と、を含むメモリセルを有し、第1のトランジスタ160と、第2のトランジスタ162とは、少なくとも一部が重畳して設けられる半導体装置である。また、絶縁層128と第2のトランジスタのゲート絶縁層146は、式((ta/tb)×(εrb/εra)<0.1)を満たす。(但し、式中、taはゲート絶縁層146の膜厚を示し、tbは絶縁層128の膜厚を示し、εraはゲート絶縁層146の誘電率を示し、εrbは絶縁層128の誘電率を示す。)

(もっと読む)

半導体装置の製造方法

【課題】エッチングレートを上昇でき、生産性を向上できる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に交互に積層されたシリコン層とシリコン酸化膜とを備える多層膜に対して、一括してエッチングを行う工程を含み、前記エッチングの際のエッチングガスは、少なくとも2種類以上の第7族元素と、第3族元素,第4族元素,第5族元素,または第6族元素とを含有し、前記エッチング工程の際の前記半導体基板に入射するイオンのエネルギーは、100eV以上であり、前記第7族元素に対する、前記第3族乃至前記7族元素の添加比率は、0.5以上3.0以下である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】メモリセルアレイを構成する複数のメモリセルが、複数行ごとに複数のブロックに分割され、共通ビット線は、各ブロックにおいて、選択トランジスタを介して分割ビット線と電気的に接続されており、メモリセルの一は、第1のチャネル形成領域を含む第1のトランジスタと、第2のチャネル形成領域を含む第2のトランジスタと、容量素子と、を有し、ソース線は、第1のソース電極と接続され、分割ビット線は、第1のドレイン電極および第2のソース電極と接続され、ワード線は、容量素子の電極の一方と接続され、信号線は、第2のゲート電極と接続され、第1のゲート電極と、第2のドレイン電極と、容量素子の電極の他方とが接続される半導体装置を提供する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、第1の信号線と、第2の信号線と、ワード線と、ソース線とビット線との間に、並列に接続されたメモリセルと、ソース線及びビット線と電気的に接続された第1の駆動回路と、第1の信号線と電気的に接続された第2の駆動回路と、第2の信号線と電気的に接続された第3の駆動回路と、ワード線と電気的に接続された第4の駆動回路と、を有し、メモリセルは、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、容量素子と、を有し、第2のトランジスタは、酸化物半導体材料を含んで構成される。

(もっと読む)

不揮発性半導体メモリトランジスタ、および、不揮発性半導体メモリの製造方法

【課題】浮遊・制御ゲート間の容量を増大できる、島状半導体を用いた不揮発性半導体メモリトランジスタを提供する。

【解決手段】不揮発性半導体メモリトランジスタは、Si基板側からソース領域303、チャネル領域304及びドレイン領域302がこの順に形成された島状半導体301と、前記チャネル領域の外周を囲むように、トンネル絶縁膜305を間に介在させて配置された浮遊ゲート306と、浮遊ゲートの外周を囲むように、インターポリ絶縁膜307を間に介在させて配置された制御ゲート308aと、制御ゲートに接続され、所定方向に延びる制御ゲート線308と、を備える。浮遊ゲートは制御ゲートの下方及び上方領域、並びに、制御ゲート線の下方領域まで夫々延在され、浮遊ゲートと、制御ゲートの上面、下面及び内側面との間、及び、浮遊ゲートの、制御ゲート線の下方領域まで延在した部分と、制御ゲート線との間には、夫々インターポリ絶縁膜が介在配置される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型のトランジスタにおいてゲートからシリサイドの位置を精度よく制御できるようにする。

【解決手段】柱状半導体14の中央部には、その周囲を囲むように、ゲート絶縁膜9が形成され、さらに、ゲート絶縁膜9の周囲を囲むように、ゲート層6が形成されている。この柱状半導体14の中央部、ゲート絶縁膜9、ゲート層6により、MIS構造が形成されている。ゲート層6の上下には、第1絶縁膜4が形成されている。第1絶縁膜4は、柱状半導体14にも接している。柱状半導体14の側面には、シリサイド18及びn型拡散層(不純物領域)19が形成されている。シリサイド18は、第1絶縁膜4によってセルフ・アラインされた位置に形成されている。

(もっと読む)

不揮発性記憶素子

【課題】本発明は、中間絶縁膜、半導体層、及びトンネル絶縁膜のうちの少なくとも1つが酸化ガリウムを含まない場合に比べて、動作安定性の向上した不揮発性記憶素子を提供する。

【解決手段】不揮発性記憶素子10は、基板30上と、ソース電極34S及びドレイン電極34Dと、半導体層36と、トンネル絶縁膜38と、電荷蓄積層40と、中間絶縁膜42と、ゲート電極44Gと、を備えており、半導体層36、トンネル絶縁膜38、及び中間絶縁膜42が、酸化ガリウムを含んでいる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜に酸素ドープ処理を行って、第2の絶縁膜中に酸素原子を供給し、第2の絶縁膜上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

81 - 100 / 682

[ Back to top ]