Fターム[5F083ER21]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 電気的に消去するもの(EEPROM) (2,068)

Fターム[5F083ER21]の下位に属するFターム

一括消去(フラッシュメモリ) (1,055)

ブロック消去 (331)

Fターム[5F083ER21]に分類される特許

161 - 180 / 682

誘電体膜、誘電体膜を用いた半導体装置の製造方法及び半導体製造装置

【課題】高誘電率を有する誘電体膜の製造方法を提供する。

【解決手段】薄いシリコン酸化膜を形成したSi基板上に、HfN/Hf積層膜を形成し、アニール処理によりHf、Si、O、Nの混合物からなる金属酸窒化物とする誘電体膜の製造する。(1)EOTの低減が可能であり、(2)リーク電流がJg=1.0E−1A/cm2以下に低減され、(3)固定電荷の発生によるヒステリシスが抑制され、(4)700℃以上の熱処理を行ってもEOTの増加が無く耐熱性に優れる。

(もっと読む)

半導体デバイスの製造方法及び基板処理装置

【課題】金属製のゲート電極(メタル電極)のダメージを熱酸化により修復する際の高誘電率ゲート絶縁膜の結晶化を抑制する。

【解決手段】エッチングにより側壁が露出した高誘電率ゲート絶縁膜とメタル電極とを有する基板を処理室内に搬入する工程と、処理室内で、基板を高誘電率ゲート絶縁膜が結晶化しない温度に加熱した状態で、基板に対してプラズマで励起した水素含有ガスと酸素含有ガスとを供給して酸化処理を施す工程と、処理後の基板を処理室内から搬出する工程と、を有し、酸化処理を施す工程では、水素含有ガスの活性化時期と酸素含有ガスの活性化時期とが互いに一致するよう、処理室内への水素含有ガスの供給を開始した後、所定時間経過してから処理室内への酸素含有ガスの供給を開始する。

(もっと読む)

不揮発性半導体集積回路装置

【課題】不揮発性半導体集積回路装置のチップサイズを縮小させる。

【解決手段】シリコン基板上に隣り合って配置された第1および第2ゲート電極とそれらの側方下部のシリコン基板に形成された一対のソース・ドレイン領域とを有し、第2ゲート電極とシリコン基板との間に配置された第2ゲート絶縁膜に電荷を蓄えることで情報を記憶するメモリセルにおいて、メモリセルの消去動作時には、消去非選択セルの第1ゲート電極に正電圧を印加する。

(もっと読む)

半導体装置、表示装置および電子機器

【課題】液晶パネルの表示品質を向上させることができると共に、高速動作することができる半導体装置を提供する。

【解決手段】D/Aコンバータの基準電圧発生回路71は、絶縁性基板と、この絶縁基板上に形成された不揮発性メモリ素子131,132,133,…およびTFT素子141,142,143,…,151,152,153,…を有する。D/Aコンバータのアナログバッファ回路は、基準電圧発生回路71から出力された基準電圧V0,V1,V2,V3,…を受ける。不揮発性メモリ素子131,132,133,…の素子特性の変更して、アナログバッファ回路のオフセット電圧を調整することが可能になっている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造において、シリコン窒化膜の含有水素量を低減してメモリ動作の長期信頼性が確保された製造方法を提供する。

【解決手段】半導体装置の製造方法は、表面にシリコン窒化膜103が形成されたシリコン基板101aを収容した処理室内の圧力を大気圧よりも低くした状態で処理室内に酸素含有ガスと水素含有ガスとを供給して、シリコン窒化膜103の一部を酸化する工程と、シリコン窒化膜103の酸化した部分104を除去する工程と、を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】コントロールゲートとフローティングゲートとの間の電極間絶縁膜に発生するリーク電流を低減させ、メモリセルの微細化に伴うリーク耐性の劣化を抑制する半導体不揮発性記憶装置を提供する。

【解決手段】半導体基板1上に複数の不揮発性メモリセルを集積した不揮発性半導体記憶装置であって、メモリセルは、半導体基板1上に形成されたトンネル絶縁膜2aと、トンネル絶縁膜2a上に形成されたフローティングゲート電極3aと、フローティングゲート電極3aの上面に形成された第1の電極間絶縁膜4aと、フローティングゲート電極3aの側面及び第1の電極間絶縁膜4aを覆うように形成された第2の電極間絶縁膜5aと、電極間絶縁膜5a上に形成されたコントロール電極6aとを備えている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】動作信頼性を向上させる不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】基板100上に形成された蓄積層105と蓄積層上に形成された制御ゲート電極107を備えた第1電極MTと、基板100上に形成された第2電極ST2及び第3電極ST2と、ゲート長方向に沿って対向する第2電極と第3電極ST2との側壁及び基板100上に形成された第2絶縁膜112と、第2、第3ゲート電極ST2間に埋設された第1絶縁膜113と、第2電極ST2及び第1電極MT間に埋設された第2絶縁膜109、110と、第1ゲート電極MT、第2ゲート電極ST2、第3ゲート電極ST2、及び第1、第2絶縁膜上113、112にそれぞれ形成され、且つ第1絶縁膜113における水素原子の拡散を防止する第3絶縁膜114とを具備する。

(もっと読む)

欠陥検査方法

【課題】コンタクトホールの導通状態を容易に検査できる欠陥検査方法を提供する。

【解決手段】半導体装置を作製する際に基板上に形成され、2つの筒状のコンタクトホールが底面側で接続されて管状を成すとともに管状の両端が基板上面に設けられた2つの開口部で開口している管状コンタクトホールのU字管6に対し、開口部のうち一方の開口部を覆う可塑性膜4を第1の気圧状態で形成する被膜形成ステップと、可塑性膜4で覆われた基板を第1の気圧とは異なる第2の気圧状態にさらすことによって、U字管6のうちU字管6の管状の一部が塞がっているU字管6上の可塑性膜4を変形させる気圧変更ステップと、可塑性膜4が変形したか否かを観察することによって、U字管6の管状の一部が塞がっているか否かを検査する検査ステップと、を含む。

(もっと読む)

メモリ書込用電源回路

【課題】昇圧の際の消費電流を削減する。

【解決手段】チャージポンプ回路14が、クロックジェネレータ12から出力されたクロック信号CLK、CLKBに同期して動作し、電源電圧Vccを昇圧した昇圧電圧Vppを出力し、昇圧電圧の電圧値がリミッタ回路16に設定された設定電圧値Vtnを超えた場合に、リミッタ回路16が導通して昇圧電圧Vppが設定電圧値Vtnを超えないように制限し、電流検出回路18が、リミッタ回路16を流れる電流Vppiが設定電流値を超えている期間、クロック信号CLK、CLKBの出力を停止するためのローレベルの停止信号CLKENをクロックジェネレータ12へ出力する。

(もっと読む)

不揮発性半導体記憶装置

【課題】デポジッション膜を形成することなく、ゲートとコンタクトのショートを抑制する不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1のコントロールゲート14を、フローティングゲート13側に位置する第1側面と、第1側面の反対に位置する第2側面と、コントロールゲート14の第1側面側の上部に形成されたシリサイド領域22と、コントロールゲート14の第2側面側の上部に形成された突出部8とを含むように構成する。そのサイドウォール絶縁膜21は、シリサイド領域22を覆うことなく突出部8の少なくとも一部を被覆する第1部分と、第1部分から連続的に設けられ、第2側面に接触して第2側面を被覆する第2部分とを含むものとする。

(もっと読む)

半導体装置およびその製造方法

【課題】動作速度が速く、かつ書き換え可能な回数が多くい不揮発性メモリセルと、高い信頼性を有する不揮発性メモリセルとを有する半導体装置を提供する。

【解決手段】メモリゲート電極11a、11bがコントロールゲート電極5a、5bのサイドウォール形状に形成されたスプリットゲート型の不揮発性メモリにおいて、メモリゲート長La、Lbの異なるメモリセルを同一チップ内に混載することにより、動作速度が速く書き換え可能回数の多いメモリと信頼性のあるメモリとを有するメモリチップを安価に製造することができる。

(もっと読む)

半導体装置

【課題】第1導電型の半導体層とトンネルウィンドウが対向する第2導電型の不純物拡散領域との高い接合耐圧を得ることができる、半導体装置を提供する。

【解決手段】各メモリセルにおいて、半導体基板2の表層部には、N型の第1不純物拡散領域3が形成されている。また、半導体基板2の表層部には、第1不純物拡散領域3に対して所定方向の一方側に、第1不純物拡散領域3と間隔を空けて、N型の第2不純物拡散領域4が形成されている。半導体基板2上には、第1絶縁膜6が形成されている。第1絶縁膜6には、第1厚膜部8が形成されており、第2不純物拡散領域4の全周縁は、第1厚膜部8の直下に位置している。

(もっと読む)

不揮発性半導体記憶装置とその駆動方法および電子機器

【課題】周辺回路の増大を極力抑えつつ、データディスターブを改善する不揮発性半導体記憶装置を提供する。

【解決手段】第1ボディ領域100上に不純物拡散層104,124を、第1不純物拡散層104上に第2ボディ領域106を形成する。第1不純物拡散層104はメモリトランジスタMTのドレイン領域と選択トランジスタSTのソース領域、第1不純物拡散層124は選択トランジスタSTのドレイン領域をなす。第2ボディ領域106と第1不純物拡散層104に跨るように第2ボディ領域106上にメモリトランジスタMTのゲート部G_MTをMONOS構造で形成する。第1不純物拡散層104、第1ボディ領域100、第1不純物拡散層124に跨るように選択トランジスタSTのゲート部G_STをMOS型構造で形成する。両トランジスタMT,STは、バックゲートとなるボディ領域が電気的に分離される。

(もっと読む)

半導体装置とその製造方法

【課題】歩留まりと信頼性を高めるフラッシュメモリセルを備えた半導体装置とその製造方法を提供する。

【解決手段】半導体装置の製造方法は、シリコン基板1に素子分離絶縁膜6を形成する工程と、シリコン基板1の表面にトンネル絶縁膜を形成する工程と、素子分離絶縁膜6とトンネル絶縁膜の上に第1導電膜を形成する工程と、第1導電膜をパターニングして導電パターン13aにする工程と、導電パターン13aの表層部分をスパッタエッチングする工程と、導電パターン13aと素子分離絶縁膜6の上に中間絶縁膜16を形成する工程と、中間絶縁膜16の上に第2導電膜17を形成する工程と、導電パターン13a、中間絶縁膜16、及び第2導電膜17をパターニングすることによりフラッシュメモリセルFLを形成する工程とを有する。

(もっと読む)

不揮発性記憶装置の記憶維持

【課題】NAND型の不揮発性記憶装置において、障壁高さが低い絶縁体や誘電率の高い絶縁体や電荷をトラップする絶縁体や強誘電体を記憶素子に使用し、高速化や書込み回数の制約を改善できるが、電荷の漏洩が増えて長期の記憶維持が困難になる。また、微細化や多値化によっても記憶維持が困難になっている。読書き操作時の電荷の漏洩をある程度容認し得る装置を提供する。

【解決手段】漏洩した電荷はリフレッシュ操作で回復して、動作マージンが不足気味の記憶素子でも利用可能にする。記憶ブロック毎の読書き回数をカウンタで集計して、読書き回数が一定の値を超過した記憶ブロックをリフレッシュする。

(もっと読む)

半導体装置

【課題】消去時間の短縮を行なうとともにデータアクセスを効率的に実行することのできる不揮発性メモリ機能を有する半導体装置を提供する。

【解決手段】コマンドレジスタ/制御回路(24)の制御のもとに、メモリセル境界領域に配置される埋込消去ゲート配線(4)に対して消去電圧を印加し、フローティングゲート(FG)と埋込消去ゲートEGの間で電荷を移動させて消去動作を行なうとき、消去電圧印加中にメモリゲート線(MGL)およびアシストゲート線(AGL)に読出選択電圧を印加してデータの読出を実行する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】MONOS型半導体記憶装置の電荷蓄積用のトラップ膜及びビット線拡散層を有する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板101に形成され、それぞれ行方向に延伸する複数のビット線拡散層104と、半導体基板101上における互いに隣接する各ビット線拡散層104同士の間に形成され、それぞれが電荷トラップ膜102bを含む複数のONO膜102と、複数のビット線拡散層104の上にそれぞれ形成された複数のビット線絶縁膜105と、半導体基板101の上にそれぞれ複数のONO膜102及び複数のビット線絶縁膜105を覆うように形成され、各ビット線拡散層104と交差して列方向に延伸する複数のワード線106とを有している。ビット線絶縁膜105の膜厚はONO膜102の膜厚よりも小さく、且つビット線絶縁膜105の上面はONO膜102の上面と平行である。

(もっと読む)

集積装置

【課題】

形状に限定されることなく、柔軟性ないし可撓性を有し、任意の形状の各種装置を作成することが可能な素子を用いた集積装置を提供すること。

【解決手段】

回路素子が長手方向に連続的又は間欠的に形成されている素子、回路を形成する複数の領域を有する断面が長手方向に連続的又は間欠的に形成されている素子を複数複数束ね、撚り合せ、織り込み又は編み込み、接合し、組み合わせて成形加工し又は不織状に成形したことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】コントロールゲート電極とメモリゲート電極間に発生する電界強度を緩和してリーク電流を低減できる、コントロールゲート電極とメモリゲート電極が近接するスプリットゲート型不揮発性メモリを提供する。

【解決手段】半導体基板1S上にゲート絶縁膜GOXが形成され、このゲート絶縁膜GOX上にコントロールゲート電極CGが形成されている。そして、コントロールゲート電極CGの右側の側壁には、積層絶縁膜を介してメモリゲート電極MGが形成されている。このとき、コントロールゲート電極CGの上端部にバーズビークBVが形成されている。この結果、コントロールゲート電極CGの上端部と、メモリゲート電極MGの上端部が、バーズビークBV分だけ離れるので電界強度の緩和を図ることができ、コントロールゲート電極CGとメモリゲート電極MG間を流れるリーク電流を低減できる。

(もっと読む)

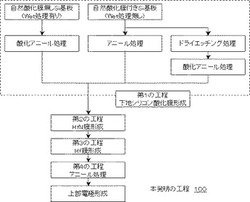

不揮発性半導体記憶装置及びその製造方法

【課題】周辺回路領域の電界効果トランジスタのゲート電極の角部の形状を改善する。

【解決手段】本発明の例に係わる不揮発性半導体記憶装置は、メモリセルアレイ領域と、メモリセルアレイ領域の周辺に形成される周辺回路領域とを具備し、周辺回路領域は、素子領域AAと、素子領域AAを取り囲む素子分離領域10と、素子領域AA上に形成され、チャネル幅方向のゲート電極13の端部及び角部が素子分離領域10上に形成される電界効果トランジスタとを有し、ゲート電極13の角部の曲率半径rは、チャネル幅方向の素子領域AAの端部からチャネル幅方向のゲート電極13の端部までの幅よりも小さく、かつ、85nmよりも小さい。

(もっと読む)

161 - 180 / 682

[ Back to top ]