Fターム[5F083ER21]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 電気的に消去するもの(EEPROM) (2,068)

Fターム[5F083ER21]の下位に属するFターム

一括消去(フラッシュメモリ) (1,055)

ブロック消去 (331)

Fターム[5F083ER21]に分類される特許

201 - 220 / 682

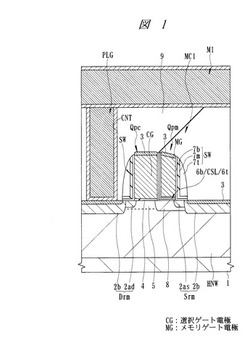

半導体装置およびその製造方法

【課題】不揮発性メモリセルを有する半導体装置において、駆動力の低下を抑えて、信頼度を向上させることのできる技術を提供する。

【解決手段】メモリセルMC1をp型の導電性を示す導電膜からなる選択ゲート電極CGを有する選択用pMIS(Qpc)とp型の導電性を示す導電膜からなるメモリゲート電極MGを有するメモリ用pMIS(Qpm)とから構成し、書込み時には半導体基板1側からホットエレクトロンを電荷蓄積層CSLへ注入し、消去時にはメモリゲート電極MGからホットホールを電荷蓄積層CSLへ注入する。

(もっと読む)

不揮発性半導体メモリ

【課題】メモリセルを可及的に小さくできるとともにセル単位で書き込み消去が可能な不揮発性半導体メモリを提供する。

【解決手段】NAND列であって、絶縁膜11上の半導体領域と、ソース/ドレイン領域14a、14bと、チャネル領域12と、電荷をトラップできる電荷トラップ膜20と、磁化の向きが固定された第1のハーフメタル強磁性金属からなるソース/ドレイン電極401とを有し、各電荷トラップ膜上に設けられ、第2のハーフメタル強磁性金属からなるゲート電極30a1、30a2であって、前記ゲート電極は、磁化の向きが前記ソース/ドレイン電極の磁化の向きに略平行な第1の領域と、磁化の向きが略反平行な第2領域から構成され、前記第1の領域が、前記ゲート電極に電流を印加することにより、前記電荷トラップ膜上から前記絶縁膜上へ、及び前記絶縁膜上から前記電荷トラップ膜上へと、可逆的に移動可能となっているゲート電極と、を備える。

(もっと読む)

不揮発性記憶装置、集積回路装置及び電子機器

【課題】加工精度の向上等が可能な不揮発性記憶装置、集積回路装置及び電子機器を提供すること。

【解決手段】不揮発性記憶装置は、電気的に書き換え可能な不揮発性の複数のメモリーセル及び複数のビット線が配置される主記憶回路10と、電気的に書き換え可能な不揮発性の複数の情報メモリーセル及び複数のビット線が配置され、少なくとも主記憶回路10の不良メモリーセルのアドレス情報を記憶する情報記憶回路20と、主記憶回路10の複数のビット線のうちの対応ビット線と情報記憶回路20の複数のビット線のうちの対応ビット線との電気的接続をオン状態又はオフ状態にするための選択トランジスターが配置される選択回路30とを含み、情報記憶回路20は主記憶回路10と選択回路30との間に配置される。

(もっと読む)

半導体デバイス上に共形酸化物層を形成するための方法

半導体基板上に酸化物層を形成するための方法及び装置を開示する。1つ又は複数の実施形態では、半導体基板の温度を約100℃未満に制御することによって、プラズマ酸化を使用して、共形酸化物層を形成することができる。1つ又は複数の実施形態による半導体基板の温度を制御するための方法は、静電チャックならびに冷却剤及びガス対流を利用することを含む。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】消去速度が速く、メモリセル間の干渉が少ない不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置1において、それぞれ複数の層間絶縁膜ILD及び制御ゲート電極CGを交互に積層させて積層体MLを形成する。そして、積層体MLに積層方向に延びる貫通ホールHを形成し、貫通ホールHを介して層間絶縁膜ILDにおける貫通ホールHに面した部分をエッチングして除去し、除去部分Aを形成する。次に、貫通ホールH及び除去部分Aの内面上に絶縁膜IPDを形成し、除去部分Aの内部にシリコンからなる浮遊ゲート電極FGを形成し、浮遊ゲート電極FGにおける貫通ホールHに面した部分を覆うように絶縁膜TOxを形成する。そして、貫通ホールHの内部に半導体ピラーSPを埋設する。

(もっと読む)

不揮発性半導体メモリセル及び不揮発性半導体メモリ装置

【課題】レイアウト面積の増大を抑えつつ信頼性を向上させることができる1層ポリシリコンプロセスで製造可能な不揮発性半導体メモリセルを提供する。

【解決手段】共通のコントロールゲートCGで制御されるとともに、互いに並列接続された複数のフローティングゲート型トランジスタT2、T3を有し、複数のフローティングゲート型トランジスタT2、T3と選択トランジスタT1とが半導体基板上で直線状に配列されたものであって、複数のフローティングゲート型トランジスタT2、T3の各ドレインが直線状のメタル配線22で接続される。

(もっと読む)

メモリ回路とその導電層の配線

【課題】メモリ回路のビットライン、電圧ライン、ワードラインの配線を提供する。

【解決手段】メモリ回路100のメモリアレイ100aは、データを記憶する少なくとも一つのメモリセル101aを含む。メモリセル101aは、ワードラインWL、ビットラインBL、ビットラインバー、第一電圧ライン、及び第二電圧ラインに結合される。メモリ回路100は、第一導電層、第一導電層に結合される第二導電層、及び、第二導電層に結合される第三導電層を備える。第三導電層は、ワードラインWLに対して配線され、メモリセル101a内で、ビットラインBL、ビットラインバー、第一電圧ライン、及び第二電圧ラインがない。

(もっと読む)

不揮発性半導体メモリセル及び不揮発性半導体メモリ装置

【課題】従来に比べ信頼性を向上させることができる不揮発性半導体メモリセル及び不揮発性半導体メモリ装置を提供する。

【解決手段】本発明の不揮発性半導体メモリセルは、半導体基板上に形成される複数のMOSトランジスタからなり、当該メモリセルを選択するためのセレクトゲートと、記憶内容を制御するためのコントロールゲートとを有する不揮発性半導体メモリセルであって、 互いに並列接続されるとともに、独立の複数のコントロールゲートでそれぞれ制御される複数のフローティングゲート型トランジスタと、複数のフローティングゲート型トランジスタと直列に接続され、セレクトゲートに接続される選択トランジスタとを有し、複数のフローティングゲート型トランジスタと選択トランジスタとが半導体基板上で直線状に配列されたものであって、複数のフローティングゲート型トランジスタの各ドレインが直線状のメタル配線で接続されたものである

(もっと読む)

半導体装置及びその製造方法

【課題】柱状構造体の形成の際のリソグラフィの合わせずれの許容度を拡大し、デバイス特性の劣化を抑制する半導体装置及びその製造方法を提供する。

【解決手段】第1層と、前記第1層の主面の上に設けられた第2層と、前記主面を貫通し、前記第1層と前記第2層とに延在する導電性の柱状構造体と、前記主面の前記第2層の側において前記柱状構造体の側壁に付設された側部と、を備えたことを特徴とする半導体装置を提供する。

(もっと読む)

メモリデバイス及びメモリデバイスの形成方法

【課題】プログラマブルMOSFET(105)とロジックMOSFET(110)とを含むメモリデバイスを同一チップ上に形成する。

【解決手段】半導体基板を被う層状ゲート積層体の成形から始まり、層状ゲート積層体の高kゲート電極層上で停止するよう金属ゲート電極層にパターンを形成して、半導体基板上に第1、第2ゲート金属ゲート電極(16、21)を形成するメモリデバイスの製法が提供される。次のプロセスで、高kゲート誘電体層の一部を被う少なくとも1つのスペーサ(55)を第1ゲート電極(16)に形成する。高kゲート誘電体層の露出された残存部分をエッチングし、第1金属ゲート電極のサイドウォールを越えて延びる部分を有する第1高kゲート誘電体(17)及び第2金属ゲート電極(21)のサイドウォールに整合されたエッジを有する第2高kゲート誘電体(22)を形成する。

(もっと読む)

半導体メモリセル及び半導体メモリセルの製造方法、半導体メモリセルの動作方法

【課題】単一ポリEEPROMセルをスタックゲートポリEEPROMセルの水準にスケーリングできる半導体メモリセルを提供する。

【解決手段】単一ポリEEPROMセルは、フローティングゲートFG上にカップリングのためのコンタクトを形成させ、コンタクトはコントロールゲートCGラインによりワードライン用ポリシリコンWLの方向に連結される。このコンタクトとフローティングゲート用ポリシリコンFGとの間にカップリングのための誘電膜102を形成してフローティングゲート用ポリシリコンFGとコンタクトを通じてカップリングを実施する。また、この半導体メモリセルで、プログラム、消去、読み出しが可能なように動作させる。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】ISSG酸化法によるメモリ特性の劣化が生じにくい不揮発性半導体記憶装置を実現できるようにする。

【解決手段】不揮発性半導体記憶装置の製造方法は、以下の工程を備えている。メモリ領域101及び周辺トランジスタ領域102の上に、第1のゲート絶縁膜106及び第1の導電膜107を順次形成する工程(a)。第1の導電膜107及び第1のゲート絶縁膜106における周辺トランジスタ領域102の上に形成された部分を除去する工程(b)。メモリ領域101の上に第1の導電膜107が残存した状態においてISSG(in-situ steam generation)酸化を行い、周辺トランジスタ領域102の上に第2のゲート絶縁膜109を形成する共にメモリ領域101の上に残存する第1の導電膜107の上部に導電膜上酸化膜110を形成する工程(c)。

(もっと読む)

不揮発性メモリ素子及びその駆動方法

【課題】プログラム及び消去動作部分と読み出し動作部分とを分離させることによって、耐久性またはサイクル特性を画期的に改善させる不揮発性メモリ素子及びその駆動方法を提供する。

【解決手段】単一ポリEEPROMの不揮発性メモリ素子は、第1タイプウェル10上に形成されるフローティングゲート50と、第2タイプウェル20上に形成されるとともにフローティングゲート50と直列連結される複数のトランジスタ30,40と、を備え、これらのトランジスタ30,40のうち、いずれかひとつはプログラム及び消去のための第1トランジスタ30であり、他のひとつは読み出し(reading)のための第2トランジスタ40である。

(もっと読む)

NAND型不揮発性半導体メモリ

【課題】書き込み動作時、メモリセルのチャネルを確実にカットオフさせる。

【解決手段】本発明の例に係わるNAND型不揮発性半導体メモリは、電荷蓄積層及び制御ゲート電極を有し、互いに直列接続される複数のメモリセルと、複数のメモリセルの一端とソース線との間に接続される第1のセレクトゲートトランジスタと、複数のメモリセルの他端とビット線との間に接続される第2のセレクトゲートトランジスタと、複数のメモリセルの制御ゲート電極それぞれに与える電圧を制御するドライバとを具備し、書き込み動作時、ドライバは、複数のメモリセルから選択された第1のメモリセルの制御ゲート電極に第1の電圧を印加し、第1のメモリセルからソース線側に複数個離れて並んだ3つ以上の第2のメモリセルの制御ゲート電極それぞれにメモリセルのチャネルをカットオフさせるカットオフ電圧を印加する。

(もっと読む)

半導体装置

【課題】メモリセル間の干渉効果の抑制とセルの信頼性の維持の両方を実現する不揮発性メモリを備える半導体装置を提供する。

【解決手段】素子分離絶縁層STIと制御ゲート電極CGとの間でワード方向に隣り合う電流遮断層BLに実質的に挟まれるように、電流遮断層BLよりも誘電率が高い高誘電体層31を、その下面が電荷トラップ層24の頂面と同一または上方に位置するように設ける。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極上にシリサイド層を安定して形成すること。

【解決手段】メモリセル100は、シリコン基板10と、シリコン基板10上に互いに隣り合って配置されたゲート電極12、13と、シリコン基板10とゲート電極12間に形成された絶縁層30と、シリコン基板10とゲート電極12間に形成された電荷蓄積層26と、を備え、ゲート電極12は、シリコン基板10から離間するに従って少なくとも部分的に幅広になる。シリコン基板10から離間するに従って少なくとも部分的に幅広となるようにゲート電極12を形付けることで、シリサイド層45を安定して形成することが実現可能になる。

(もっと読む)

半導体素子及び半導体素子のパターン形成方法

【課題】多様な幅を有するパターンを同時に形成しつつ、一部領域ではダブルパターニング技術によりパターン密度を倍加させる半導体素子のパターン形成工程及び該工程を容易に適用可能な構造の半導体素子を提供する。

【解決手段】半導体素子は、第1方向に相互平行に延びている複数のラインパターンを含む。複数のラインパターンのうちから選択される複数の第1ラインパターンは、第2方向に沿って交互に選択されて両側で各々隣接している2つのラインパターンの両端部のうち、素子領域の第1端部にさらに近い各端部に比べて、第1端部からさらに遠く位置する第1端部を有する。複数のラインパターンのうちから選択される複数の第2ラインパターンは、第2方向に沿って交互に選択され、両側で各々隣接している2つのラインパターンの両端部のうち、第1端部にさらに近い各端部より、第1端部からさらに近く位置する第2端部を有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】層間絶縁膜を表面研磨する工程を経て形成される半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1の主面s1上に、高耐圧ゲート絶縁膜IG1および高耐圧ゲート電極EG1からなる高耐圧ゲートG1を形成した後、サリサイドブロック膜SAB、層間絶縁膜ILを順に形成し、その層間絶縁膜ILをCMPにより研磨する。サリサイドブロック膜SABは、下層から順に酸化シリコンを主体とする絶縁膜である保護酸化膜t1と、窒化シリコンを主体とする絶縁膜である保護窒化膜t2とによって形成する。また、層間絶縁膜ILの研磨は、高耐圧ゲートG1上面のサリサイドブロック膜SABに達するまで研磨する。

(もっと読む)

電気光学装置、電気光学装置の製造方法、電子機器

【課題】不揮発性メモリと画素TFTとを同一基板上に形成でき、且つ両者を良好に動作させることが可能な電気光学装置を提供する。

【解決手段】画素TFTのゲート絶縁膜18を不揮発性メモリのトンネル絶縁膜(第1の絶縁膜)35と、トンネル絶縁膜35よりも膜厚の大きい第2の絶縁膜37によって構成する。また、フローティングゲート電極36のコントロールゲート電極60側の面を凹凸とし、該凹凸によってフローティングゲート電極36の表面積を拡げる。これにより、フローティングゲート電極36とコントロールゲート電極60との間の容量を、フローティングゲート電極36と半導体層33との間の容量よりも大きくする。

(もっと読む)

半導体装置及びその製造方法

【課題】電荷消去特性及び電荷保持特性に優れた半導体装置を提供する。

【解決手段】半導体領域101と、半導体領域の表面に形成されたトンネル絶縁膜102と、トンネル絶縁膜の表面に形成された電荷蓄積絶縁膜103と、電荷蓄積絶縁膜の表面に形成されたブロック絶縁膜104と、ブロック絶縁膜の表面に形成された制御ゲート電極105と、を具備する半導体装置であって、トンネル絶縁膜は、半導体領域の表面に形成され、シリコン及び酸素を含有する第1の領域102aと、第1の領域の表面に形成され、シリコン及び窒素を含有する第2の領域102bと、電荷蓄積絶縁膜の裏面に形成され、シリコン及び酸素を含有する第3の領域102dと、第2の領域と第3の領域との間に形成され、シリコン、窒素及び酸素を含有し、第2の領域の窒素濃度よりも低い窒素濃度を有し、第3の領域の酸素濃度よりも低い酸素濃度を有する第4の領域102cと、を含む。

(もっと読む)

201 - 220 / 682

[ Back to top ]