Fターム[5F083ER21]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 電気的に消去するもの(EEPROM) (2,068)

Fターム[5F083ER21]の下位に属するFターム

一括消去(フラッシュメモリ) (1,055)

ブロック消去 (331)

Fターム[5F083ER21]に分類される特許

61 - 80 / 682

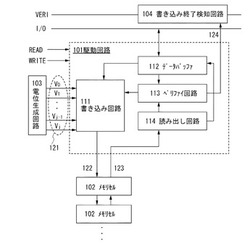

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】高品質な半導体装置を提供する。

【解決手段】P型の半導体基板10と、半導体基板10内に形成されるNウェル11、半導体基板10内かつNウェル11上に形成されるPウェル12、及びPウェル12上に形成されるメモリセルトランジスタMTを含むCell領域と、半導体基板10内に形成されるNウェル14、及びNウェル上14に形成されるトランジスタHVP−Trを含むHVP−Tr領域と、半導体基板10上に形成されるトランジスタHVN―Trを含むHVN―Tr領域と、半導体基板10内に形成されるNウェル22、半導体基板10内かつNウェル22上に形成されるPウェル23、およびPウェル23上に形成されるトランジスタLVNE−Trを含むLVNE−Tr領域と、を具備し、Nウェル11及びNウェル22の底面の位置はNウェル14の底面の位置よりも低く、Nウェル14の底面の位置はPウェル12及びPウェル23の底面の位置よりも低い。

(もっと読む)

半導体装置及びその製造方法

【課題】実施形態によれば、十分な消去速度が得られる半導体装置及びその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、第1の積層体と、メモリ膜と、第1のチャネルボディと、第2の積層体と、ゲート絶縁膜と、第2のチャネルボディとを備えている。前記選択ゲートの側面と前記第2の絶縁層との間に段差部が形成されている。前記段差部を被覆する部分の前記第2のチャネルボディの膜厚は、前記第2の絶縁層間に設けられた部分の膜厚よりも厚い。

(もっと読む)

欠陥フラッシュメモリダイの動作不能化

【課題】複数のフラッシュメモリダイを含むデバイス内の欠陥フラッシュメモリダイを動作不能化する製品ならびに関連する方法およびシステムを提供する。

【解決手段】動作不能化されていないフラッシュメモリダイに基づくフラッシュメモリのデータ記憶容量を示すラベルを、複数のフラッシュメモリダイを含むパッケージに付すことができる。ダイレベル、パッケージレベル、および/またはボードレベルにおいて、様々な動作不能化方法を適用することができる。

(もっと読む)

記憶素子および記憶装置

【課題】低電圧および低電流動作時における繰り返し特性が向上した記憶素子および記憶装置を提供する。

【解決手段】下部電極10、記憶層20および上部電極30をこの順に積層した記憶素子1において、記憶層20は、2.8mΩcm以上1Ωcm未満の抵抗率を有するイオン源層21と、抵抗変化層22とを有する。これにより、低電圧または低電流パルスを印加した際の記録状態から消去状態への抵抗変化層の抵抗値の回復が改善され、繰り返し特性が向上する。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】ドレイン領域の一部に半球状の窪みを設けトンネル領域を形成し、フローティングゲート電極はトンネル領域の半球状の窪みに沿って入り込む形状となるように形成する。

(もっと読む)

半導体装置の作製方法

【課題】オフ電流の極めて小さい酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを適用することで、消費電力の極めて小さい半導体装置を提供する。

【解決手段】基板上に加熱処理により酸素を放出する下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、基板を加熱処理する。次に、第1の酸化物半導体膜上に導電膜を形成し、該導電膜を加工してソース電極およびドレイン電極を形成する。次に、第1の酸化物半導体膜を加工して第2の酸化物半導体膜を形成した直後にソース電極、ドレイン電極および第2の酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極を形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層の側面からの酸素の脱離を防ぎ、酸化物半導体層中の欠陥(酸素欠損)が十分に少なく、ソースとドレインの間のリーク電流が抑制された半導体装置を提供する。

【解決手段】酸化物半導体膜に対して第1の加熱処理を施した後に該酸化物半導体膜を加工して酸化物半導体層を形成し、その直後に該酸化物半導体層の側壁を絶縁性酸化物で覆い、第2の加熱処理を施すことで、酸化物半導体層の側面が真空に曝されることを防ぎ、酸化物半導体層中の欠陥(酸素欠損)を少なくして半導体装置を作製する。該半導体装置はTGBC(Top Gate Bottom Contact)構造とする。

(もっと読む)

不揮発性半導体記憶装置

【課題】面積の縮小を図る。

【解決手段】不揮発性半導体記憶装置は、複数のメモリストリング200を具備し、各メモリストリングは、一対の柱状部A、および一対の柱状部の下端を連結させるように形成された連結部Bを有する半導体層SPと、柱状部に直交したコントロールゲートCGと、一対の柱状部の一方と直交し、コントロールゲートの上方に形成された第1選択ゲートSGSと、一対の柱状部の他方と直交し、コントロールゲートの上方に形成され、第1選択ゲートと同一レベルでかつ一体である第2選択ゲートSGDと、柱状部とコントロールゲートとの各交差部に形成されたメモリセルトランジスタMTrと、柱状部と第1選択ゲートとの交差部に形成された第1選択トランジスタSSTrと、柱状部と第2選択ゲートとの交差部に形成された第2選択トランジスタSDTrと、を含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリブロック内で選択的に消去動作を実行することが可能な積層型の不揮発性半導体記憶装置を提供する。

【解決手段】メモリブロック中の少なくとも1つのサブブロックを選択的に消去する消去動作を実行する際、選択された第1のサブブロックにおいては、ビット線及びソース線に第1電圧を印加する一方、ワード線には第1電圧よりも小さい第2電圧を印加する。ドレイン側選択ゲート線、及びソース側選択ゲート線には、第1電圧よりも所定の値だけ低い第3電圧を印加する。非選択とされた第2のサブブロックにおいては、ドレイン側選択ゲート線、及びソース側選択ゲート線には、第1電圧と略同一の第4電圧を印加する。

(もっと読む)

半導体基板の作製方法

【課題】半導体基板の欠陥を低減する。また、歩留まり高く欠陥の少ない半導体基板を作製する。また、歩留まり高く半導体装置を作製する。

【解決手段】支持基板に酸化絶縁層を介して半導体層を設け、該半導体層の端部における、支持基板及び酸化絶縁層の密着性を高めた後、半導体層の表面の絶縁層を除去し、半導体層にレーザ光を照射して、平坦化された半導体層を得る。半導体層の端部において、支持基板及び酸化絶縁層の密着性を高めるために、半導体層の表面から、レーザ光を照射する。

(もっと読む)

不揮発性半導体記憶装置

【課題】微細化した場合でもメモリセルの絶縁耐圧を確保し精密なしきい値分布を制御可能なセル構造を実現する。

【解決手段】半導体基板Sの表面層に形成された複数の素子分離絶縁膜DIと、素子分離絶縁膜DIに画定された複数の素子領域AAと、トンネル酸化膜10を介して半導体基板S上に形成された電荷蓄積層FGとゲート絶縁膜20を介して電荷蓄積層FG上に形成された制御ゲートCGとをそれぞれ含む複数のゲート構造と、前記ゲート構造直下の半導体基板Sの表面層を間に挟むように素子領域AAに形成された複数の不純物拡散層IDLと、前記ゲート構造の間を埋め込むように酸化シリコンで形成された絶縁膜60と、前記ゲート構造の側壁に接するように窒化シリコンで形成された絶縁膜40と、を備える不揮発性半導体記憶装置において、ゲート絶縁膜40の底面を、電荷蓄積層FGの高さの少なくとも半分以上半導体基板Sの表面から離隔させる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】特性を向上させる不揮発性メモリを有する半導体装置を提供する。

【解決手段】半導体装置を、制御ゲート電極CGと、制御ゲート電極CGと隣合うように配置されたメモリゲート電極MGと、絶縁膜3と、その内部に電荷蓄積部を有する絶縁膜5と、を有するよう構成する。このうち、メモリゲート電極MGは、絶縁膜5上に位置する第1シリコン領域6aと、第1シリコン領域6aの上方に位置する第2シリコン領域6bと、を有するシリコン膜よりなり、第2シリコン領域6bは、p型不純物を含有し、第1シリコン領域6aのp型不純物の濃度は、第2シリコン領域6bのp型不純物の濃度よりも低く構成する。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】データの保持期間を長くする半導体装置又は半導体記憶装置を提供する。

【解決手段】一対の不純物領域を有する第1の半導体層152aと、第1の半導体層と同じ材料であり、第1の半導体層と離間する第2の半導体層152bと、第1、第2の半導体層の上に設けられた第1の絶縁層153と、第1の絶縁層153を介して第1の半導体層に重畳する第1の導電層154と、第1の絶縁層153を介して第1の導電層に重畳し、第1の半導体層と異なる材料である第3の半導体層156と、第1の導電層及び第3の半導体層に電気的に接続される第2の導電層157bと、第3の半導体層156に電気的に接続され、第2の導電層と同じ材料である第3の導電層157aと、第3の半導体層、第2の導電層、及び第3の導電層の上に設けられた第2の絶縁層158と、第2の絶縁層を介して第3の半導体層に重畳する第4の導電層159と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】フローティングゲートへの帯電電荷を、別途工程を追加することなく除去できる半導体装置の製造方法を提供する。

【解決手段】半導体基板10の一主面11に少なくともフローティングゲート25を含む電極層22を形成し、電極層22上に層間絶縁膜40を形成し、層間絶縁膜に電極層22を露出するビアホール42と、半導体基板の一主面を露出するビアホール48を形成し、ビアホール42を介して電極層22と電気的に接続され、ビアホール48を介して半導体基板10と電気的に接続される配線層60を形成し、配線層60をパターニングして少なくとも電極層22のみに接続されている配線62を形成する。

(もっと読む)

半導体素子およびその製造方法

【課題】二酸化シリコンとシリコンとの良好な界面特性を有し、絶縁基板上に作製された半導体素子を提供する。

【解決手段】半導体素子10は、多結晶シリコン膜4と、絶縁膜5,9と、金属量子ドット8とを備える。多結晶シリコン膜4は、絶縁基板1上に配置され、アモルファスシリコン膜を熱プラズマジェットによってアニールして作製される。絶縁膜5は、SiO2からなり、多結晶シリコン膜4に接して多結晶シリコン膜4上に形成される。金属量子ドット8は、Ptからなり、Pt薄膜を熱プラズマジェットによってアニールして絶縁膜5上に形成される。絶縁膜9は、SiO2からなり、金属量子ドット8を覆うように絶縁膜5上に形成される。

(もっと読む)

半導体装置

【課題】半導体装置を小型化することを課題の一とする。また、記憶素子を有する半導体装置の駆動回路の面積を縮小することを課題の一とする。

【解決手段】入力端子と出力端子の位置が固定された複数のセルを第1の方向に配置し、各セルの入力端子および出力端子とそれぞれ電気的に接続される配線を複数のセル上に積層させ、且つ、その配線の延在方向をセルが並べられた第1の方向と同方向とすることで、駆動回路の小型化を図った半導体装置を提供する。

(もっと読む)

半導体装置の駆動方法

【課題】信頼性の高い書き込み動作を高速に行うことのできる半導体装置の駆動方法を提供する。

【解決手段】多値書き込みを行う半導体装置の駆動方法において、酸化物半導体層を含むトランジスタを用いたメモリセルに、書き込みを行う書き込みトランジスタのオンオフを制御する信号線を、ビット線に沿うように配置し、読み出し動作時に容量素子に与える電圧を書き込み時にも利用して、多値書き込みを行う。書き込みを行いながらビット線の電位を検知することによって、書き込みベリファイ動作を行うことなく、書き込みデータに対応した電位がフローティングゲートに正常に与えられたかを確認することができる。

(もっと読む)

半導体不揮発性メモリ装置

【課題】トンネル絶縁膜にエッジ部があることによるトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】トンネル絶縁膜の上部であって、トンネル領域のエッジ部から離間した位置に、電荷受け渡し用電極を配置し、電荷受け渡し用電極とフローティングゲート電極とが、電気的に接続されるようにした。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな半導体装置を提供する。また、回路規模を縮小し、書き込み、読み出しに対する信頼性を向上させる。

【解決手段】酸化物半導体層を含むトランジスタを用いたメモリセルに対して、ベリファイ動作と、読み出しを行う際に、異なるしきい値電圧を示すデュアルゲート駆動のトランジスタを抵抗素子として用いることで、一系統の基準電位回路のみで安定したベリファイ動作、及び読み出し動作が可能となる。

(もっと読む)

61 - 80 / 682

[ Back to top ]