Fターム[5F083GA05]の内容

Fターム[5F083GA05]の下位に属するFターム

リーク電流の低下 (1,514)

Fターム[5F083GA05]に分類される特許

61 - 80 / 1,011

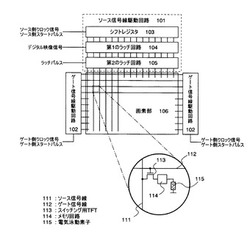

表示装置

【課題】電気泳動表示装置で、書き込み回数のさらに少ないアクティブマトリクス型の電

気泳動表示装置を提供することを課題とする。

【解決手段】複数の画素電極上に、複数の帯電粒子を内蔵したマイクロカプセルを配置し

、前記画素電極の電位により前記帯電粒子を制御することによって明暗を表示することを

特徴とした表示装置において、前記画素電極への映像信号の再書き込み動作を、画素に表

示する映像が変化する場合に行うことにより、書き込み回数を低減する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子埋設用凹部上端部の肩落ちによるキャパシタ特性のバラツキが低減された半導体装置を提供する。

【解決手段】半導体装置は、保護層80は、凹部(孔23)の上端部の周囲に設けられている。この保護層80は、保護層80と同一層に位置しており、論理回路領域に位置している多層配線層を構成する絶縁層よりも誘電率が高い材料で構成されており、機械強度に優れた部材となる。これにより、凹部(孔23)上端部の肩落ちを抑制し、キャパシタ高さのバラツキを抑制する。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

半導体装置

【課題】高速動作が可能であり、且つ消費電力の低減が可能な半導体装置を提供する。

【解決手段】酸化物半導体を有するトランジスタを備える半導体装置において、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜において、酸素濃度が異なる。代表的には、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と比較して、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜の酸素濃度が低い。

(もっと読む)

不揮発性メモリ要素及びこれを含むメモリ素子

【課題】不揮発性メモリ要素及びこれを含むメモリ素子を提供する。

【解決手段】両電極の間にメモリ層を含み、該メモリ層は複数層構造を持つ不揮発性メモリ要素である。メモリ層は、ベース層及びイオン種交換層を含み、これらの間のイオン種の移動による抵抗変化特性を持つ。イオン種交換層は、少なくとも2つの層を含む複数層構造を持つ。不揮発性メモリ要素は、複数層構造のイオン種交換層によりマルチビットメモリ特性を持つ。ベース層は酸素供給層であり、イオン種交換層は酸素交換層である。

(もっと読む)

不揮発性半導体記憶装置

【課題】相変化メモリの書き換え電流および書き換え電圧を低減する。

【解決手段】相変化膜を記憶素子として用いた相変化メモリにおいて、相変化膜2a、2bとして、温度低下に対して結晶化領域の抵抗変化が減少する温度領域を持つ材料を用い、かつ相変化膜2a、2bの間に、相変化膜2a、2bよりも大きい熱伝導率と、相変化膜2a、2bよりも小さい抵抗率を有する中間金属膜1を挿入する。そして、書き換え時に発生する相変化膜2a、2b内の熱を中間金属膜1を通じて放熱することにより、相変化膜2a、2b内の熱分布を均一にすると共に、中間金属膜1近傍の相変化膜2a、2bを局所冷却し、高抵抗状態にすることにより、書き換え電流の過剰な増加を抑制する。

(もっと読む)

半導体集積回路装置

【課題】過電圧がLSIの電源端子に印加されたことを確認できるようにする。

【解決手段】半導体集積回路装置(10)は、内部回路(11)と、上記内部回路に電源電圧を供給するための電源端子(15,16)とを含む。このとき、上記内部回路の電源電圧として想定されるレベルを越える電圧(過電圧)が上記電源端子に印加された事実を記録するための過電圧印加情報記録回路(12)を設ける。過電圧印加情報記録回路には、過電圧が上記電源端子に印加された事実が記録されているため、それに基づいて、過電圧がLSIの電源端子に印加されたことを確認することができる。

(もっと読む)

半導体記憶装置、および、ビット線の充電方法

【課題】低消費電力モードから通常動作モードへの復帰時におけるビット線の充電時間を適切に設定することで、復帰動作で消費される電力を低減する。

【解決手段】半導体記憶装置10は、複数のビット線2a,2b…のそれぞれを充電する充電回路4と、帰還経路5aの配線にダミービット線3が用いられているリングオシレータ5と、リングオシレータ5の発振回数が、複数のビット線2a,2b…の数に基づいて設定された所定の回数に達すると、検出信号を出力するカウンタ6と、低消費電力モードから通常動作モードへの復帰を指示する復帰信号に応じて、充電回路4による複数のビット線2a,2b…の充電を開始させるとともにリングオシレータ5の発振を開始させ、カウンタ6から出力された検出信号に応じて、充電回路4による複数のビット線2a,2b…の充電を終了させる制御回路7と、を有する。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

半導体装置

【課題】消費電力の低減と干渉の抑制を実現できる半導体装置を提供する。

【解決手段】半導体装置は、直列に多段接続された第1及び第2のチップと制御チップとを備える。第1及び第2のチップのそれぞれの転送制御部は、識別信号が制御チップから供給されると当該識別信号後段のチップへ伝送し、制御チップが供給するクロック信号のn番目のパルスに基づいて、識別信号が表す識別情報を第2の記憶領域に書き込み、書き込みが終了するまでクロック信号の後段のチップへの伝送を阻止する。制御チップは、コマンドによって第1及び第2のチップを排他的にアクセスし、第1及び第2のチップのスイッチ制御回路は、コマンド及び識別情報に応じてそれぞれ対応する第1のスイッチ回路を互いに排他的に制御する。

(もっと読む)

半導体集積回路装置

【課題】低電源電圧でもSNMと書き込みマージンを両立させたSRAMを備える。

【解決手段】SRAMは、複数列に対応して設けられた複数のセル電源線、電源電圧を供給する電源線、及び前記複数のセル電源線にそれぞれ対応して設けられ、各々はその対応するメモリセル電源線と前記電源線との間を電気的に接続する複数の電源回路を含む。メモリセルの各々は、第1及び第2のPチャネル型トランジスタと、第1ないし第4のNチャネル型トランジスタと第1及び第2の記憶ノードとを有するCMOSラッチ回路で構成される。電源回路は、第1の状態時にはその接続するセル電源線に第1の電圧を供給し、第2の状態時にはその接続するセル電源線に前記第1の電圧よりも低い第2の電圧を供給する、

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】重畳する第1のトランジスタおよび第2のトランジスタからなる第1のインバータと、重畳する第3のトランジスタおよび第4のトランジスタからなる第2のインバータと、第1の選択トランジスタと、第2の選択トランジスタと、を有し、第1のインバータの出力端子、第2のインバータの入力端子および第1の選択トランジスタのソースおよびドレインの一方が接続され、第2のインバータの出力端子、第1のインバータの入力端子および第2の選択トランジスタのソースおよびドレインの一方が接続されることによって、微細化したSRAM回路を形成する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてエネルギーギャップの異なる少なくとも2層の酸化物半導体層を含み、かつ積層された酸化物半導体層の間に混合領域を有する酸化物半導体積層を用いる。

(もっと読む)

半導体装置およびその駆動方法

【課題】2Tr1C型半導体メモリ装置の消費電力を削減する。

【解決手段】読み出しトランジスタのしきい値の絶対値をビット線のデータ電位の変動幅よりも大きくする(あるいはビット線のデータ電位の変動幅を読み出しトランジスタのしきい値の絶対値よりも小さくする)ことで、ソース線の電位を固定し、また、書き込みワード線の電位変動を小さくでき、読み出しワード線の電位は、読み出しの際にのみ変動させる。また、そのようなしきい値の絶対値の大きなトランジスタは、ゲートの材料を仕事関数の高い窒化インジウム等を用いて形成する。仕事関数の高い材料を用いることで、ゲート絶縁物のポテンシャル障壁が高まり、リーク電流が抑制できるので、電荷保持特性も向上する。

(もっと読む)

半導体装置

【課題】トランジスタのしきい値電圧のばらつきの影響を緩和し、複数の状態(例えば3以上の状態)の区別を正確、かつ容易にした半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、ワード線と、ビット線とワード線に接続されたメモリセルと、入力されたアドレス信号によって指定されたメモリセルを選択するように、複数の第2信号線及び複数のワード線を駆動する、第2信号線およびワード線の駆動回路と、書き込み電位を第1信号線に出力する、書き込み回路と、指定されたメモリセルに接続されたビット線から入力されるビット線の電位と、複数の読み出し電位とを比較する読み出し回路と、ビット線の電位と複数の読み出し電位の比較結果に基づいて複数の補正電圧のいずれかを選択する制御回路と、書き込み電位及び複数の読み出し電位を生成して、書き込み回路及び読み出し回路に供給する、電位生成回路と、を有する半導体装置。

(もっと読む)

電解質メモリ素子

【課題】 低電圧駆動可能で低消費電力型の不揮発性メモリ素子およびその製造方法を提供する。

【解決手段】 本発明のある態様においては、対向配置された第1基体10Aおよび第2基体20Aと、第1基体および第2基体に挟まれる電解質層30とを備えるメモリ素子1000が提供される。第1基体の基板12の一の面12Sの上には、二酸化バナジウムを主成分とするメモリ層100Aが形成され、メモリ層に接している第1電極部110Aと第2電極部120Aとを有している。第2基体の対向基板22は、第1基体に対向する面の上に第3電極部230Aを有している。そして電解質層30は、第1電極部と第2電極部との間においてメモリ層に近接している。本発明のある態様においては、一方の基体に第1〜第3電極部とメモリ層とが形成された別の典型的なメモリ素子2000も提供される。

(もっと読む)

半導体装置

【課題】SRAMメモリセルを有する半導体装置において、その特性の向上を図る。

【解決手段】SRAMを構成するドライバトランジスタ(Dr1)が配置される活性領域(Ac)の下部に、絶縁層(BOX)を介して、素子分離領域(STI)により囲まれたn型のバックゲート領域(nBG)を設け、ドライバトランジスタ(Dr1)のゲート電極(G)と接続する。また、n型のバックゲート領域(nBG)の下部に配置され、少なくともその一部が、素子分離領域(STI)より深い位置に延在するp型ウエル領域(Pwell)を設け、接地電位(VSS)に固定する。かかる構成によれば、トランジスタの閾値電位(Vth)をトランジスタがオン状態の時には高く、逆に、オフ状態の時には低くなるように制御し、また、p型ウエル領域(Pwell)とn型のバックゲート領域(nBG)との間のPN接合も順バイアスさせないよう制御することができる。

(もっと読む)

電気化学素子および電気化学素子を用いた相補型回路

【課題】従来の電気化学素子とは逆極性でオンオフ動作を行うイオン移動型電気化学素子を提供する。この素子を従来型の電気化学素子とを組合せれば、低消費電力の相補型回路を構成できる。

【解決手段】イオン拡散材料として使用する酸化タンタルを挟んで一方にゲート電極を配置し、もう一方に絶縁物材料によって隔てられたソース電極とドレイン電極を配置する。このとき、ソース・ドレイン電極間の電気的接続を実現するゲート電圧(オン電圧)がオフ状態を実現するゲート電圧(オフ電圧)よりも低い電気化学素子が得られる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】実際の強誘電体メモリセルについて疲労特性を直接に測定する試験方法を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に形成された強誘電体キャパシタの疲労特性の面内分布を取得する第1の工程と、前記面内分布に基づいて、半導体装置を製造する第2の工程と、を含み、前記第2の工程は、前記半導体装置が形成される基板上に複数の強誘電体キャパシタを形成し、前記第1の工程で取得された疲労特性の面内分布から、前記半導体装置が形成される基板上の特定領域を指定し、前記特定領域に形成された前記強誘電体キャパシタについて疲労特性を測定し、前記特定領域の強誘電体キャパシタについて測定した前記疲労特性に基づき、前記特定領域の強誘電体キャパシタについて良否判定を行い、前記良否判定の結果が良であれば、前記複数の強誘電体キャパシタの全てについて良と判定する。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】第1の金属元素および第2の金属元素を含む金属酸化膜を形成する際に、金属酸化膜中の第1の金属元素及び第2の金属元素の組成比の制御性を向上させる。

【解決手段】基板を収容した処理室内に、第1の金属元素を含む第1原料と酸化剤とを供給することで、基板上に第1の金属元素を含む第1の金属酸化膜を形成する工程と、処理室内に、第1原料と第2の金属元素を含む第2原料とを混合した混合原料と酸化剤とを供給することで、基板上に第1の金属元素および第2の金属元素を含む第2の金属酸化膜を形成する工程と、を交互に繰り返すことで、基板上に、第1の金属酸化膜と第2の金属酸化膜とを交互に積層して、第1の金属元素および第2の金属元素を含む第3の金属酸化膜を形成する工程を有する。

(もっと読む)

61 - 80 / 1,011

[ Back to top ]