Fターム[5F083GA05]の内容

Fターム[5F083GA05]の下位に属するFターム

リーク電流の低下 (1,514)

Fターム[5F083GA05]に分類される特許

41 - 60 / 1,011

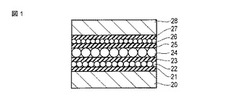

メモリ装置

【課題】配線電極間の双方向の電流値、書き込み及び消去の電圧値、および記憶保持時間が制御容易なメモリ装置を提供する。

【解決手段】微結晶である第1の導電性微粒子を含む微結晶層22と、微結晶層22を挟むトンネル絶縁膜21、23とを有する第1の二重トンネル接合構造と、微結晶である第2の導電性微粒子を含む微結晶層26と、微結晶層26を挟むトンネル絶縁膜25、27とを有する第2の二重トンネル接合構造と、第1の二重トンネル接合構造と第2の二重トンネル接合構造との間に配置され、情報電荷を蓄積する電荷蓄積層と、第1の二重トンネル接合構造、電荷蓄積層、及び第2の二重トンネル接合構造を挟む第1、第2の導電層とを備える。第1の導電性微粒子の平均粒径は、第2の導電性微粒子の平均粒径と異なっている。

(もっと読む)

半導体装置およびその製造方法

【課題】電流―電圧特性の向上およびオン電流を増大することが可能で、高速動作に優れた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板12の主面に形成され、第1の方向に延在する複数の活性領域と、活性領域を区画する素子分離領域と、半導体基板12の主面に形成されたものであって、平面視して複数の活性領域に交差する方向に延在する複数のゲート溝と、ゲート溝のそれぞれに埋め込まれた複数のゲート電極22と、を備えた半導体装置であって、ゲート溝のそれぞれの底面には、第1の方向に延在すると共に、上面71aが半導体基板12の主面よりも低い位置に配置する一対の突起部71が形成されており、ゲート電極22は、ゲート絶縁膜21を介して突起部71の上面71aと内側面71bと外側面71cとを覆ってなる、ことを特徴とする。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法とデータ書き換え方法

【課題】データ保持時間を、マスクROMと同様の無限大とすることができる、長期にわたりデータを保持できる信頼性の高いEEPROMを提供する。

【解決手段】不揮発性半導体記憶装置は、所定のセンスレベルに対して熱平衡状態しきい値電圧が正方向である第1の不揮発性半導体記憶素子100に正のデータを記憶し、熱平衡状態しきい値電圧が負方向である第2の不揮発性半導体記憶素子200に負のデータを記憶することでデータ保持時間を無限大にする。

(もっと読む)

半導体装置

【課題】頻繁なリフレッシュ動作が不要で、正常な読み出しを行うことのできる2トランジスタ型のDRAMを備えた半導体装置を提供する。

【解決手段】本実施形態の半導体装置は、ゲートが第1配線に接続され、第1ソース/ドレインの一方が第2配線に接続された第1トランジスタと、ゲート絶縁膜、ゲート電極、および前記ゲート絶縁膜と前記ゲート電極との間に設けられしきい値を変調するしきい値変調膜を有するゲート構造と、第2ソース/ドレインとを備え、前記ゲート電極が前記第1トランジスタの前記第1ソース/ドレインの他方に接続され、前記第2ソース/ドレインの一方が第3配線に接続され、前記第2ソース/ドレインの他方が第4配線に接続された第2トランジスタと、を備えている。

(もっと読む)

不揮発性半導体記憶装置

【課題】非選択メモリセルに流れる逆方向電流を低減させた不揮発性半導体記憶装置を提供することを目的とする。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、複数のメモリセルを有するメモリセルアレイと、選択第1配線に選択第1配線電圧を供給し、非選択第1配線に非選択第1配線電圧を供給する第1配線制御回路と、アクセス対象となるメモリセルに接続された第2配線である選択第2配線に選択第2配線電圧を供給し、その他の第2配線である非選択第2配線に非選択第2配線電圧を供給する第2配線制御回路とを備え、メモリセルは、第1ダイオードのアノード側に第2配線が接続され、第1ダイオードのカソード側に第1配線が接続され、メモリセルアレイは、第2配線制御回路及びメモリセル間の第2配線に挿入され、第2配線制御回路側をアノード、メモリセル側をカソードとする第2ダイオードを有することを特徴とする。

(もっと読む)

抵抗変化メモリ

【課題】低電流動作が可能で、一方向整流性および良好なデータ保持特性を有する抵抗変化メモリを提供することを可能にする。

【解決手段】本実施形態の抵抗変化メモリは、金属イオン源を含むイオン源電極と、対向電極と、前記イオン源電極と前記対向電極との間に設けられたアモルファスシリコン膜と、前記アモルファスシリコン膜と前記イオン源電極との間に設けられたポリシリコン膜と、を有するメモリセルを備えている。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択メモリセルトランジスタに電荷を蓄積する際の電圧を従来よりも自由に設定し得る不揮発性半導体記憶装置を提案する。

【解決手段】不揮発性半導体記憶装置1では、選択メモリセルトランジスタ115に電荷を蓄積させる際、電圧の高い書き込み禁止電圧をP型MOSトランジスタ9bから印加し、電圧の低い書き込み電圧をN型MOSトランジスタ15aから印加して、選択メモリセルトランジスタ115又は非選択メモリセルトランジスタ116へ電圧を印加する役割分担を、P型MOSトランジスタ9b及びN型MOSトランジスタ15aに分けたことで、P型MOSトランジスタ9b及びN型MOSトランジスタ15aそれぞれのゲート電圧やソース電圧を個別に調整でき、最終的にゲート基板間電圧を例えば4[V]等に設定し得る。

(もっと読む)

不揮発性プログラマブルロジックスイッチ

【課題】メモリの選択的な書き込みを行う際のパストランジスタのゲート絶縁膜の破壊を防ぐとともにパストランジスタのゲート絶縁膜を薄くすることを可能にし、かつメモリの微細化によって書き込み効率が損なわれない不揮発性プログラマブルロジックスイッチを提供する。

【解決手段】第1端子と、第2端子と、メモリ状態を制御する制御信号を受ける第3端子とを有する第1メモリと、ソース/ドレインの一方が第2端子に接続される第1トランジスタと、第1トランジスタのソース/ドレインの他方にゲートが接続される第2トランジスタとを備えた、第1セルおよび第2セルを有する。第1セルの第1メモリの第3端子と、第2セルの第1メモリの第3端子は共通に接続され、第1セルに書き込みを行う場合、第3端子が書き込み電源に接続され、第1セルの第1端子は接地電源に接続され、第2メモリの第1端子は書き込み防止電源に接続される。

(もっと読む)

不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置の動作電力を低減する。

【解決手段】不揮発性半導体記憶装置は、TiN層からなる上部電極TE及びバリアメタルBM1,BM2と、金属酸化物HfOx層を有する可変抵抗素子VRと、ポリシリコン層及びポリシリコン層と金属酸化物HfOx層との界面に形成されたSiGe層を有する下部電極BEと、バリアメタルBM1と、NIP層からなるバイポーラ型の電流整流素子Diとを直列接続したメモリセルMCを備える。

(もっと読む)

メモリ用シフトレジスタ

【課題】大容量なメモリ用シフトレジスタを提供する。

【解決手段】メモリ用シフトレジスタは、基板101と、基板101上に形成され、基板101の主面に垂直な軸Lの周りを回転する螺旋形状を有するチャネル層111とを備える。さらに、メモリ用シフトレジスタは、基板101上に形成され、軸Lに平行な方向に延びており、チャネル層111内の電荷を転送するために使用される3本以上の制御電極1121,1122,1123を備える。

(もっと読む)

半導体装置

【課題】メモリの大容量化と図りつつ、消費電力を軽減でき、且つ、消費電力を一定にす

る。

【解決手段】メモリを、複数のメモリブロックを対称に配置して構成する。また、メモリ

に供給されるアドレス信号のうち、特定の信号の組み合わせにより、データ読み出しまた

は書き込みの対象となるメモリセルを含むメモリブロックを一意に特定する。さらに、当

該メモリブロック以外のメモリブロックに供給される信号を一定値に保つ。このようにす

ることで、メモリアレイにおけるビット線の配線長を短縮し、負荷容量を軽減すると同時

に、メモリ内のあらゆるアドレスのメモリセルに対するデータ読み出しもしくは書き込み

において、消費電流を一定にできる。

(もっと読む)

半導体記憶装置、半導体装置及び半導体記憶装置の製造方法

【課題】DRAMとReRAMとを混載する場合において、容量素子及び抵抗変化素子の性能を維持しながら製造コストを低減する。

【解決手段】半導体記憶装置は、抵抗変化素子1と容量素子101とを具備している。抵抗変化素子1は、第1深さD1のシリンダー型のMIM構造を有し、抵抗変化型メモリ用である。容量素子101は、第1深さD1よりも深い第2深さD2のシリンダー型のMIM構造を有し、DRAM用である。

(もっと読む)

メモリ装置

【課題】大容量化が容易であり、高収率且つ高信頼性を有する半導体メモリ装置が提供される。

【解決手段】本発明に従うメモリ装置は、記憶素子と前記記憶素子にデータを書き込むか、又は読み出す周辺回路を含む第1半導体チップ、及び外部と前記第1半導体チップとの間で交換されるデータ又は信号の入出力機能を遂行する第2半導体チップを含み、本発明のその他の特徴に従うメモリ装置は、外部とデータ又は信号を交換するための入出力回路チップ、及び各々前記入出力回路チップから提供される信号に応答して前記データを格納するか、或いは内部に格納されたデータを読み出して前記入出力回路チップへ出力する、垂直方向に積層される複数のコアチップを含む。

(もっと読む)

抵抗変化型不揮発記憶装置、半導体装置及び抵抗変化型不揮発記憶装置の動作方法

【課題】低電圧かつ高速なスイッチング動作を、低いばらつきで実現可能な抵抗変化型不揮発記憶装置を提案する。

【解決手段】抵抗変化型不揮発性記憶装置は、第1電極14と、第1電極14上に設けられた抵抗変化部18と、抵抗変化部18上に設けられた第2電極11とを具備している。抵抗変化部18は、第1電極14上に設けられ、印加する電圧により抵抗が変化する抵抗変化層13と、抵抗変化層13上に設けられ、フィラメントを形成する安定層12とを備えている。抵抗変化層と安定層は異なる金属酸化物である。抵抗変化層の酸化物生成エネルギーは、安定層の酸化物生成エネルギーよりも高い。抵抗変化層13の膜厚は、抵抗変化部18のオフ状態の抵抗が膜厚で律速される範囲の抵抗になるような値を有する。

(もっと読む)

ALD/CVDプロセスにおけるGST膜のためのアンチモン前駆体

【課題】原子層堆積及び化学気相成長からなる群より選択されるプロセスを用いてゲルマニウム−アンチモン−テルル合金膜を製造する方法を提供する。

【解決手段】原子層堆積及び化学気相成長からなる群より選択されるプロセスを用いてゲルマニウム−アンチモン−テルル合金膜を製造する方法であって、シリルアンチモン前駆体が該合金膜のためのアンチモン源として用いられる方法が提供される。新規のシリルアンチモン化合物もまた開示される。

(もっと読む)

SOI基板の作製方法

【課題】表面のP−V値が小さく、かつ、高い結晶性を有する半導体薄膜層を備えたSOI基板の作製方法を提供する。

【解決手段】半導体薄膜層の結晶性を高く保つため、水素イオン添加処理中の半導体基板の温度を200℃以下に抑制した。加えて、水素イオン添加処理後の半導体基板を100℃以上400℃以下に保持した状態で半導体基板に対してプラズマ処理を行うことにより、水素イオン添加処理により生じる、半導体薄膜層の分離に対して寄与度の高いSi−H結合を残存させたまま、半導体薄膜層の分離に対して寄与度の低いSi−H結合を低減した。

(もっと読む)

半導体記憶装置

【課題】4個のトランジスタと2個のMTJ素子からなり、電源を印加しないでも不揮発性メモリとして動作するSRAMからなる半導体記憶装置を提供する。

【解決手段】第1及び第2のインバータ2,4と第1及び第2の転送用MOSFET3,5とを含むメモリセル1からなるSRAMにおいて、第1及び第2のインバータ2,4はスピン注入型のMTJ素子6,8と駆動用MOSFET7,9とからなり、これらのインバータ2,4からフリップフロップ回路が構成され、第1及び第2のインバータ2,4の出力端子は、それぞれ第1及び第2の転送用MOSFET3,5を介してビットライン及びビットラインバーに接続され、第1及び第2の転送用MOSFET3,5のゲートは、同一のワードラインに接続される。従来のSRAMに比較してメモリセルの面積が小さく、高速で低消費電力の不揮発性メモリが得られる。

(もっと読む)

抵抗変化型不揮発性記憶素子の書き込み方法および抵抗変化型不揮発性記憶装置

【課題】書き込み動作の安定性および信頼性を向上した抵抗変化型不揮発性記憶素子の書き込み方法を提供する。

【解決手段】抵抗変化素子を含むメモリセルに対して電圧パルスを印加することにより、抵抗変化素子を、印加される電圧パルスの極性によって第1の抵抗状態と第2の抵抗状態とを可逆的に変化させる書き込み方法であって、抵抗変化素子を第2の抵抗状態から第1の抵抗状態に変化せしめる時に、抵抗変化素子に対して、第2の電圧パルス(VL)よりも電圧の絶対値が小さく、かつ、第1の電圧パルス(VH)と極性が異なる第1の抵抗化プレ電圧パルス(VLpr)を印加する第1ステップと、その後、第1の電圧パルス(VH)を印加する第2ステップとを含む第1の抵抗状態化ステップを含む。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造のフラッシュメモリーの提供

【解決手段】

半導体基板1上にシリコン窒化膜2及びシリコン酸化膜3が選択的に設けられ、シリコン酸化膜3上には、選択的に横(水平)方向エピタキシャルSi層5が設けられ、Si層5の両側面には、それぞれ側面を接して横(水平)方向エピタキシャルSi層6が設けられた構造からなる半導体層が素子分離領域のシリコン窒化膜4により絶縁分離されている。Si層6の残りの周囲には第1のゲート酸化膜10を介して包囲型フローティングゲート電極11が設けられ、包囲型フローティングゲート電極11の周囲には第2のゲート酸化膜12を介して包囲型コントロールゲート電極13(ワード線)が設けられ、Si層5には概略ソースドレイン領域9が設けられている2重包囲型ゲート電極を有するMIS電界効果トランジスタより構成したフラッシュメモリー。

(もっと読む)

41 - 60 / 1,011

[ Back to top ]