Fターム[5F083GA19]の内容

Fターム[5F083GA19]に分類される特許

61 - 80 / 168

不揮発性半導体記憶装置

【課題】ダミーセルのゲート間絶縁膜に印加される電界を緩和して、不良が発生することを回避することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1導電型のウェル102と、ウェル内に形成された第1の素子分離膜121と、第1の素子分離膜と平行に形成され、第1の素子分離膜との間の基板表面の幅が広く設定された第2の素子分離膜122と、第1の素子分離膜間に順に形成されたゲート絶縁膜、浮遊ゲート、ゲート間絶縁膜、及び制御ゲートを含むメモリセル201と、第1の素子分離膜と第2の素子分離膜との間に順に形成されたゲート絶縁膜、浮遊ゲート、ゲート間絶縁膜、及び制御ゲートを含むダミーセル301と、ダミーセルの下方に、第1の素子分離膜と第2の素子分離膜との間のウェル内に形成され、素子分離膜の底面よりも高い位置に上面を有する第2導電型の拡散層103とを備える。

(もっと読む)

半導体装置

【課題】トランジスタ特性に優れ、ゲート絶縁膜のゲート電極の近傍の領域中で電荷や電界の集中が起こらない半導体装置を提供する。

【解決手段】半導体装置は、トランジスタを備える。トランジスタのゲート絶縁膜は窒素原子及び酸素原子を含有する。ゲート絶縁膜は、半導体層に接する第1の面及びゲート電極に接する第2の面において窒素原子を含有せず、第1の面と第2の面の間に窒素原子濃度のピークを有する。

(もっと読む)

スプリットゲート不揮発性メモリセルの作製に有用な半導体構造を形成する方法

半導体層(12)に半導体デバイス(10)を形成する方法が提供される。方法は、半導体層(12)の上方に選択ゲート誘電体層(14)を形成すること、選択ゲート誘電体層(14)の上方に選択ゲート層(16)を形成すること、選択ゲート層の少なくとも一部分を除去することによって、選択ゲート層(16)の側壁を形成することを含む。方法は、選択ゲート層(16)の側壁の少なくとも一部分に、および選択ゲート層(16)の少なくとも一部分の下に、犠牲層(22)を成長させること、犠牲層(22)を除去して、選択ゲート層の側壁の少なくとも一部分の表面および選択ゲート層の下の半導体層の表面を露出させることをさらに含む。方法は、制御ゲート誘電体層(28)、電荷蓄積層(32)、および制御ゲート層(34)を形成することをさらに含む。 (もっと読む)

半導体装置

【課題】電荷蓄積膜を用いる不揮発性記憶用MOS型トランジスタと、これを選択するMOS型トランジスタが隣接するスプリットゲート構造を有する不揮発性メモリセルにおいて、電荷保持特性を向上し、ゲート電極を低抵抗化する。

【解決手段】電荷蓄積膜のコーナー部の薄膜化を抑制して電荷保持特性を向上するために、選択ゲート電極15の側壁にテーパーを設ける。また、自己整合で形成するゲート電極を低抵抗化するシリサイドを安定に行うため、選択ゲート電極15の側壁をリセスさせる。もしくは、自己整合ゲート電極上部18と選択ゲート電極上部65の間に段差を設ける。

(もっと読む)

半導体記憶装置およびその制御方法

【課題】SOI構造の半導体記憶装置に電気的に書換え可能な不揮発性メモリを形成する手段を提供する。

【解決手段】第1の拡散層16、第2の拡散層17、前記第1および第2の拡散層間に配置された第3の拡散層、および第4の拡散層21と、前記第1および第2の拡散層とそれぞれ一部がオーバーラップし、前記第3の拡散層上から前記第4の拡散層にかけて延在するフローティングゲート電極13と、前記第1の拡散層および前記第3の拡散層に、共通の第1の電位を与える第1の制御線31と、前記第2の拡散層に、第2の電位を与える第2の制御線37と、前記第4の拡散層に、第3の電位を与える第3の制御線33と、を備え、前記フローティングゲート電極が前記第4の拡散層とオーバーラップした面積が、前記第2の拡散層とオーバーラップした面積よりも大きく、前記第1および第3の拡散層とオーバーラップした合計の面積よりも小さい。

(もっと読む)

3次元積層不揮発性半導体メモリ及びその製造方法

【課題】制御ゲート電極の角部近傍に形成されたトンネル絶縁膜に掛かる電界を緩和する。

【解決手段】本発明の例に係わる3次元積層不揮発性半導体メモリは、半導体層と、半導体層上に形成され、半導体層に対して垂直な柱状の半導体領域101と、半導体領域101の側面に形成された第1の絶縁膜102と、第1の絶縁膜102の側面に形成される電荷蓄積膜103と、電荷蓄積膜103の側面に形成される第2の絶縁膜104と、第2の絶縁膜104の側面に接し、半導体層に対して平行で平板状に形成された複数の制御ゲート電極105と、第2の絶縁膜104及び制御ゲート電極105それぞれの表面に形成された第3の絶縁膜106とを具備し、半導体領域101を介して対向する第3の絶縁膜106の距離は、半導体領域101を介して対向する制御ゲート電極105の距離より長く、制御ゲート電極105の角部は曲率を有している。

(もっと読む)

半導体装置およびその製造方法

【課題】FINFETにおいて、寄生抵抗の改善を図ることができる技術を提供する。

【解決手段】本発明におけるFINFETでは、サイドウォールSWを積層膜から形成している。具体的に、サイドウォールSWは、酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から構成されている。一方、フィンFIN1の側壁には、サイドウォールSWが形成されていない。このように本発明では、ゲート電極G1の側壁にサイドウォールSWを形成し、かつ、フィンFIN1の側壁にサイドウォールSWを形成しない。

(もっと読む)

半導体装置の製造方法

【課題】浮遊ゲート電極を有するメモリセルの高集積化を実現する半導体装置の製造方法を提供する。

【解決手段】半導体層11の表面にトンネル絶縁膜12を介してシリコンを含む第1の導電体層を形成する工程と、第1の導電体層の表面から半導体層11に至る分離溝9を形成し、第1の導電体層が所定幅で分離された、浮遊ゲート電極となる複数の導電板13bを形成する工程と、導電板13b側面の中間部まで、分離溝9を素子間絶縁膜15で埋め込む工程と、複数の導電板13bの間隔を所定幅と同等以上の幅に維持しながら、導電板13bの露出面にシリコン窒化膜16aを形成する工程と、制御ゲート電極19aとなる第2の導電体層を形成して分離溝9の上部を埋め込む工程と、を備え、シリコン窒化膜16aは、窒素元素を含む原料ガスを励起させて生成する窒素ラジカルによって、導電板13bに含まれるシリコンを窒化して形成される。

(もっと読む)

半導体装置の製造方法

【課題】電荷蓄積膜を用いる不揮発性記憶用MOS型トランジスタと、これを選択するMOS型トランジスタが隣接するスプリットゲート構造を有する不揮発性メモリセルにおいて、電荷保持特性を向上し、ゲート電極を低抵抗化する。

【解決手段】電荷蓄積膜のコーナー部20の薄膜化を抑制して電荷保持特性を向上するために、選択ゲート電極15の側壁にテーパーを設ける。また、自己整合で形成するゲート電極を低抵抗化するシリサイドを安定に行うため、選択ゲート電極15の側壁をリセスさせる。もしくは、自己整合ゲート電極上部18と選択ゲート電極上部65の間に段差を設ける。

(もっと読む)

半導体装置の製造方法

【課題】リーク電流の増加が抑制されたキャパシタを形成可能な半導体装置の製造方法を提供する。

【解決手段】基板上に第1絶縁膜と第2絶縁膜とを順次形成する工程と、第2絶縁膜を貫いて第1絶縁膜内に達する孔部を形成する工程と、孔部の底部及び側面を覆うとともに断面視で凹字型の形状を有する電極を形成する工程と、電極上及び第2絶縁膜上に、電極の上面の一部から第2絶縁膜の上面の一部にかけて開口を有するマスクを形成する工程と、マスクを用いてドライエッチングを行い、開口から露出する第2絶縁膜を除去して第2絶縁膜に開口部を形成すると共に、開口から露出する電極の上部の一部を掘削して電極の上部に切り欠き部を形成する工程と、切り欠き部の端部の少なくとも一部を等方性エッチングにより削る工程とを備える半導体装置の製造方法を採用する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高カップリング比を維持しつつ、浮遊ゲートの頂部のリーク電流を低減する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】トランジスタTRは、半導体層10に設けられた、ソース領域10sと、ドレイン領域10dと、ソース領域10sとドレイン領域10dとの間のチャネル領域10cと、チャネル領域10cの上に設けられたゲート絶縁膜30と、ゲート絶縁膜30の上に設けられ、側部40bと頂部40aとを有する電荷保持層(浮遊ゲート40)と、側部40b及び頂部40aを覆う電極間絶縁膜50と、電極間絶縁膜50の上に設けられた制御ゲート60と、を有する。制御ゲート60は、側部40bに対向する側部導電層60bと、頂部40aに対向し、仕事関数が、電荷保持層よりも高く、側部導電層60bよりも高い頂部導電層60aと、を有する。

(もっと読む)

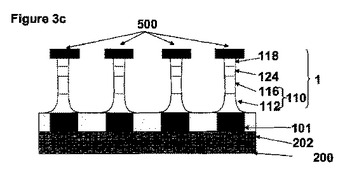

丸いコーナーを有する複数の柱を備えるクロスポイント形不揮発性メモリ装置およびその製造方法

不揮発性メモリ装置が複数の柱(1)を備え、複数の柱のそれぞれは、ステアリング素子(110)および記憶素子(118)を含む不揮発性メモリセルを備え、複数の柱のそれぞれのトップコーナーまたはボトムコーナーの少なくとも一方が丸くされる。不揮発性メモリ装置を製作する方法が、装置層のスタックを形成すること、およびこのスタックをパターン形成して複数の柱を形成することを含み、複数の柱のそれぞれは、ステアリング素子および記憶素子を含む不揮発性メモリセルを備え、複数の柱のそれぞれのトップコーナーまたはボトムコーナーの少なくとも一方が丸くされる。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置

【課題】コントロールゲートとフローティングゲートとの間の電極間絶縁膜に発生するリーク電流を低減させ、メモリセルの微細化に伴うリーク耐性の劣化を抑制する半導体不揮発性記憶装置を提供する。

【解決手段】半導体基板1上に複数の不揮発性メモリセルを集積した不揮発性半導体記憶装置であって、メモリセルは、半導体基板1上に形成されたトンネル絶縁膜2aと、トンネル絶縁膜2a上に形成されたフローティングゲート電極3aと、フローティングゲート電極3aの上面に形成された第1の電極間絶縁膜4aと、フローティングゲート電極3aの側面及び第1の電極間絶縁膜4aを覆うように形成された第2の電極間絶縁膜5aと、電極間絶縁膜5a上に形成されたコントロール電極6aとを備えている。

(もっと読む)

半導体装置

【課題】第1導電型の半導体層とトンネルウィンドウが対向する第2導電型の不純物拡散領域との高い接合耐圧を得ることができる、半導体装置を提供する。

【解決手段】各メモリセルにおいて、半導体基板2の表層部には、N型の第1不純物拡散領域3が形成されている。また、半導体基板2の表層部には、第1不純物拡散領域3に対して所定方向の一方側に、第1不純物拡散領域3と間隔を空けて、N型の第2不純物拡散領域4が形成されている。半導体基板2上には、第1絶縁膜6が形成されている。第1絶縁膜6には、第1厚膜部8が形成されており、第2不純物拡散領域4の全周縁は、第1厚膜部8の直下に位置している。

(もっと読む)

半導体装置およびその製造方法

【課題】浮遊ゲート電極膜と制御ゲート電極膜との間に設ける電極間絶縁膜の絶縁特性をより一層改善することができる半導体装置およびその製造方法を提供する。

【解決手段】素子分離絶縁膜4の上面、浮遊ゲート電極膜6の側面及び浮遊ゲート電極膜6の上面に、シリコン窒化膜と同等以上の誘電率を有する高誘電率膜を含む複数層構造で構成された電極間絶縁膜7を形成し、この電極間絶縁膜7上に制御ゲート電極膜9を形成した半導体装置であって、浮遊ゲート電極膜6の上面と電極間絶縁膜7との間にシリコン酸化膜8を形成し、浮遊ゲート電極膜6の側面に電極間絶縁膜7の高誘電率膜を直接接触させるように構成した。

(もっと読む)

半導体装置およびその製造方法

【課題】コントロールゲート電極とメモリゲート電極間に発生する電界強度を緩和してリーク電流を低減できる、コントロールゲート電極とメモリゲート電極が近接するスプリットゲート型不揮発性メモリを提供する。

【解決手段】半導体基板1S上にゲート絶縁膜GOXが形成され、このゲート絶縁膜GOX上にコントロールゲート電極CGが形成されている。そして、コントロールゲート電極CGの右側の側壁には、積層絶縁膜を介してメモリゲート電極MGが形成されている。このとき、コントロールゲート電極CGの上端部にバーズビークBVが形成されている。この結果、コントロールゲート電極CGの上端部と、メモリゲート電極MGの上端部が、バーズビークBV分だけ離れるので電界強度の緩和を図ることができ、コントロールゲート電極CGとメモリゲート電極MG間を流れるリーク電流を低減できる。

(もっと読む)

記憶素子とその製造方法および半導体記憶装置

【課題】抵抗変化層に接触する下部電極の部分の全域に均一に電界を集中させることで、特性ばらつきをなくすことを可能にする記憶素子とその製造方法および半導体記憶装置を提供する。

【解決手段】第1電極21と、第1電極21に対向した位置に形成された第2電極23と、第1電極21と前記第2電極23との間に挟まれて形成された抵抗変化層22とを有し、第1電極21は、筒状体でかつ前記抵抗変化層22側より抵抗変化層22とは反対側の方が厚く形成されている。

(もっと読む)

NAND型フラッシュメモリ

【課題】メモリセルのしきい値電圧の分布幅の拡大を抑制することが可能なNAND型フラッシュメモリを提供する。

【解決手段】NAND型フラッシュメモリは、第1の絶縁膜、電荷保持層、第2の絶縁膜、および、制御ゲートを含み、電荷保持層に保持された電荷量に応じた情報を記憶するメモリセルが直列に複数接続されたNANDストリングと、制御ゲートおよび半導体ウェルに印加する電圧を制御する制御回路とを備え、書き込み動作後、選択メモリセルにデータが書き込まれたか否かを検証するベリファイリード動作を行う前に、制御回路は、選択メモリセルの制御ゲートに、半導体ウェルの電位と同電位または書き込み電圧と同極性である第1の電圧を印加し、書き込み対象ではない非選択メモリセルの制御ゲートには、書き込み電圧と同極性であり第1の電圧よりも絶対値として大きい第2の電圧を印加するデトラップ動作を行う。

(もっと読む)

半導体装置およびその製造方法

【課題】ブロック絶縁膜をゲート幅方向に連続するように構成しながら、シリコン基板の上面部のうちのワード線方向の端部とゲート電極との間の絶縁破壊の発生を抑制する。

【解決手段】素子分離領域2によって区画された活性領域3を有する半導体基板1と、活性領域3上に形成されたトンネル絶縁膜7と、トンネル絶縁膜7上に形成された電荷蓄積膜8と、電荷蓄積膜8上に形成されたブロック絶縁膜9と、ブロック絶縁膜9上に形成されたゲート電極10、11とを有してなるメモリセルトランジスタを備え、ブロック絶縁膜9をゲート幅方向に連続するように形成し、更に、電荷蓄積膜8のうちのゲート幅方向の端部8aの膜厚を厚くするように構成した。

(もっと読む)

キャパシタの製造方法

【課題】クラウン型キャパシタの電極保護膜を新たなフォトリソグラフィー工程を追加することなく形成でき、また、該電極保護膜により下部電極への応力集中を抑制し、下部電極にき裂や断裂が発生することを防止した電極保護膜の形成方法を提供する。

【解決手段】半導体基板上に複数の絶縁膜(15,16,100,101)を有する多層膜を形成する工程と、前記多層膜に少なくとも一つのシリンダ孔31を形成する工程と、前記シリンダ孔の内壁に凹部32を形成する工程と、前記凹部の少なくとも一部に電極保護膜30を形成する工程と、前記シリンダ孔の内壁に下部電極18を形成する工程とを、この順で有するキャパシタの製造方法。

(もっと読む)

61 - 80 / 168

[ Back to top ]