Fターム[5F083GA19]の内容

Fターム[5F083GA19]に分類される特許

41 - 60 / 168

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】電気的書き換え可能な半導体不揮発性メモリにおいて、第2導電型のドレイン領域内のトンネル領域の表面には、薄い不純物濃度の第1導電型の領域を形成した。

(もっと読む)

半導体記憶装置

【課題】1つの実施形態は、例えば、電荷蓄積層内に蓄積された電荷の第2のゲート絶縁膜を介した制御ゲート電極へのリークを低減することを目的とする。

【解決手段】1つの実施形態によれば、半導体基板内で素子分離部により画定された素子領域と、素子領域を覆う第1のゲート絶縁膜と、第1のゲート絶縁膜を覆う電荷蓄積層と、半導体基板の素子領域が確定された面側を上とした場合において、電荷蓄積層の上面を覆う第1の部分と電荷蓄積層の側面を覆う第2の部分とを有する第2のゲート絶縁膜と、第2のゲート絶縁膜を介して電荷蓄積層の上面及び側面を覆う制御ゲート電極とを備え、第1の部分の耐圧は、前記第2の部分の耐圧より高い半導体記憶装置が提供される。

(もっと読む)

不揮発性半導体記憶装置

【課題】電源線等への電圧供給源であるポンプの面積を削減でき、電源線等に電圧を転送するスイッチ回路のストレスを緩和できる不揮発性半導体記憶装置を提供する。

【解決手段】第1領域と第2領域との間に配置されたセルアレイ11と、第1領域に配置された第1,第2ローデコーダ12−0と、第1領域に配置され、第1ローデコーダに電圧を伝送する第1電源線VRDEC_T<0>、第2ローデコーダに電圧を伝送する第2電源線VRDEC_B<0>と、第1,第2電源線に電圧を供給するロー系周辺回路17と、第1電源線と回路17との間を接続または遮断状態に切り換える第1スイッチ回路SWV_T<0>と、第2電源線と回路17との間を接続または遮断状態に切り換える第2スイッチ回路SWV_B<0>とを備える。書き込み動作時に、第1スイッチ回路は第1電源線と回路17との間を接続状態にし、第2スイッチ回路は第2電源線と回路17との間を遮断状態にする。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】電気的書き換え可能な半導体不揮発性メモリにおいて、第2導電型のドレイン領域内のトンネル領域と前記フローティングゲート電極領域との間には、トンネル絶縁膜が設けられており、前記フローティングゲート電極は第1導電型の導電体で形成されている電気的書き換え可能な半導体不揮発性メモリ装置。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】隣接セルとの容量を抑制することが可能な半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態の半導体記憶装置は、第1の方向および前記第1の方向と直交する第2の方向に配置される複数のメモリセルトランジスタを備える。前記メモリセルトランジスタのそれぞれは、半導体基板上に形成される第1の絶縁膜と、前記第1の絶縁膜上に形成される浮遊ゲート電極と、前記浮遊ゲート電極上に形成される第2の絶縁膜と、前記第2の絶縁膜上に形成される制御ゲート電極と、を有する。前記第1および第2の方向に隣接する2つの前記メモリセルトランジスタの前記浮遊ゲート電極は、前記隣接する方向の側面に括れた領域を有する。

(もっと読む)

半導体不揮発性メモリ装置

【課題】膜質の劣化を抑え、トンネル領域のエッジ部への電界集中を防止し、占有面積を増加することなくトンネル絶縁膜の劣化を抑制して、高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】電気的書き換え可能な半導体不揮発性メモリにおいて、ドレイン領域内のトンネル領域と前記フローティングゲート電極領域との間には、第1のトンネル絶縁膜と第2のトンネル絶縁膜が設けられており、第1のトンネル絶縁膜は、トンネル領域のエッジ部近傍に形成されており、第2のトンネル絶縁膜はトンネル領域の前記第1のトンネル絶縁膜か形成されていない領域に形成されており、第1のトンネル絶縁膜の膜厚は、第2のトンネル絶縁膜の膜厚よりも大きく、ゲート絶縁膜よりも小さく形成した。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて絶縁膜にエッチング処理を行うことにより、絶縁層を形成し、絶縁層を覆うように酸化物半導体層を形成し、酸化物半導体層を覆うように導電膜を形成し、導電膜に研磨処理を行うことにより導電膜表面を平坦化し、導電膜をエッチング処理して導電層とすることにより酸化物半導体層の最上部の表面よりも導電層の表面を低くし、導電層と酸化物半導体層に接するゲート絶縁膜を形成し、ゲート絶縁膜の上で絶縁層と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】周辺回路領域の素子の寿命が劣化するのを抑制しつつ、浮遊ゲート電極と制御ゲート電極とのカップリング性を確保する。

【解決手段】シリコン基板11は、セル領域および周辺回路領域が設けられている。トンネル絶縁膜12は、セル領域および周辺回路領域のシリコン基板11上に形成されている。浮遊ゲート電極膜13は、セル領域および周辺回路領域のトンネル絶縁膜12上に形成されている。電極間絶縁膜16は、セル領域の浮遊ゲート電極膜13上に形成されている。シリコン酸化膜14および電極間絶縁膜16は、周辺回路領域の浮遊ゲート電極膜13上に形成されている。制御ゲート電極膜17は、セル領域および周辺回路領域の電極間絶縁膜16上に形成されている。

(もっと読む)

半導体記憶装置

【課題】書き込み特性及び電荷保持特性に優れたメモリセル(セルトランジスタ)を具備する半導体記憶装置、或いは、メモリセルと共に製造するのに適した選択又は周辺トランジスタの提供。

【解決手段】セルトランジスタ201は、基板101上に、FNトンネル膜として機能するゲート絶縁膜111、最下層の浮遊ゲートに相当する第1の浮遊ゲート112を備える。更に、FNトンネル膜として機能する第1の浮遊ゲート間絶縁膜113を介して形成され、前記セルトランジスタ内の最下層の浮遊ゲートと最上層の浮遊ゲートとの間に介在する第2の浮遊ゲート114を備える。更に、FNトンネル膜として機能する第2の浮遊ゲート間絶縁膜115を介して形成され、前記セルトランジスタ内の最上層の浮遊ゲートに相当する第3の浮遊ゲート116を備える。更に、電荷ブロック膜として機能するゲート間絶縁膜117を介して形成された制御ゲート118を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】ゲート電極間絶縁膜のリーク電流を抑制し、電気的信頼性を向上した不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板上に行列状に形成された複数のメモリ素子と、同一列方向のメモリ素子に選択的に接続される複数のビット線と、同一行方向のメモリ素子に接続される複数のワード線とを具備し、各メモリ素子は、半導体基板上に順次形成された第1のゲート絶縁膜、電荷蓄積層、第2のゲート絶縁膜、制御電極と、電荷蓄積層の対向する側面に沿って、前記シリコン基板上面に形成された1対の不純物注入層とを具備し、ビット線に垂直な方向に沿った断面における電荷蓄積層の上部コーナー部が曲面を有し、上部コーナー部が前記第1のゲート絶縁膜の上方にある。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】ビット線に拡散層を用いる半導体記憶装置のチャネル領域に発生する2次電子を抑制して信頼性を向上できるようにする。

【解決手段】半導体記憶装置100は、P型の半導体基板101の上部にそれぞれが互いに並行に延びるように形成された複数のビット線拡散層108と、半導体基板101の上で、且つそれぞれが各ビット線拡散層108と交差する方向に互いに並行に延びるように形成された複数のワード線電極110とを有している。さらに、半導体基板101における各ワード線電極110の下方の領域には、周囲よりも濃度が低いP型の複数の第3の不純物層111Aがそれぞれ自己整合的に形成されている。

(もっと読む)

抵抗変化メモリ

【課題】大きい静電容量のキャパシタを含む抵抗変化メモリを提供する。

【解決手段】本実施形態の抵抗変化メモリは、アクティブ領域としての半導体領域20と、ゲート絶縁膜22を介して半導体領域21の側面に対向するゲート電極21とを有する選択トランジスタと、記憶するデータに応じて抵抗値が変化するメモリ素子1とを含むメモリセルMCと、第1のキャパシタ電極としての半導体領域30と、半導体領域30の側面に対向するキャパシタ電極31と、半導体領域20とキャパシタ電極31との間に設けられたキャパシタ絶縁膜32とを含むキャパシタ3と、を含む。

(もっと読む)

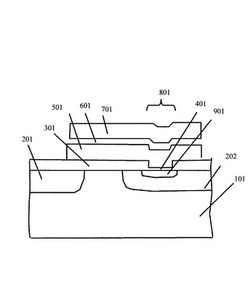

半導体記憶装置

【課題】動作信頼性を向上出来る半導体記憶装置を提供すること。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板10上に第1絶縁膜13を介在して形成された電荷蓄積層14と、電荷蓄積層14上に第2絶縁膜15を介在して形成された制御ゲート16とを具備し、制御ゲート16は、その少なくとも一部領域16−2において、その側面が外側に向かって膨らんだ形状を有し、制御ゲート16において側面が膨らみ始める部分から該制御ゲート16の頂上までの高さH1は、膨らみ始める部分より上の領域における制御ゲート16の最大幅W2_max2よりも大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧MISFETを含む半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】高耐圧MISFETQ4のゲート絶縁膜GOX4を、酸化シリコン膜と窒化シリコン膜という異なる種類の膜から形成する。具体的に、高耐圧MISFETQ4では、ゲート絶縁膜GOX4を、酸化シリコン膜PREOX1と、この酸化シリコン膜PREOX1上に形成された酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から形成している。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上にマスクを形成し、マスクにスリミング処理を行い、マスクを用いて絶縁膜にエッチング処理を行い、絶縁膜を覆うように導電膜を形成し、導電膜および絶縁膜に研磨処理を行うことにより、導電膜および絶縁膜の厚さを等しくし、導電膜をエッチングして、導電膜より厚さの小さいソース電極およびドレイン電極を形成し、絶縁膜、ソース電極、およびドレイン電極と接する酸化物半導体膜を形成し、酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上の絶縁膜と重畳する領域にゲート電極を形成する。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】デバイス特性の劣化を抑制した不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】第1ダミーセル領域121に設けられた素子分離絶縁層33と、第2ダミーセル領域122に設けられた素子分離絶縁層43と、第1ダミーセル領域121と第2ダミーセル領域122との間の境界に位置する素子分離絶縁層51とを備える。素子分離絶縁層33の上面は、浮遊電極層32の上面よりも低い高さに位置する。素子分離絶縁層43の上面は、浮遊電極層42の上面と同じ高さに位置する。浮遊電極層32に隣接する素子分離絶縁層51の上面の端部は、浮遊電極層32の上面よりも低い高さに位置する。素子分離絶縁層51の上面は、浮遊電極層32の側面から浮遊電極層42の側面へ向かって上昇する傾斜TLを有する。

(もっと読む)

電荷トラップを有するゲート誘電体を含む揮発性メモリ及びその製造方法

【課題】チャネルイオン注入領域のドーピング濃度を相対的に低下しながらも所望のしきい電圧値を得ることができる揮発性メモリを提供する。

【解決手段】ゲート誘電体として順次積層された下部ゲート誘電体、電荷トラップのための中間ゲート誘電体、及び上部ゲート誘電体を備えたセルトランジスタと、ゲート誘電体として単一層の酸化膜を備えたロジック用トランジスタとで、揮発性メモリを構成する。

(もっと読む)

半導体装置および半導体装置の製造方法。

【課題】耐圧に優れた半導体装置および半導体装置の製造方法を提供する。

【解決手段】ビット線BL方向に延伸した素子領域AAと、素子領域AAの第1の部分上に配置されたコンタクトプラグCPと、素子領域AAの第1の部分とビット線BL方向で隣接する第2の部分上に配置された選択トランジスタSTとを備え、第1の部分の上面領域のビット線BL方向に垂直なワード線WL方向の幅は、第2の部分の上面領域のワード線WL方向の幅よりも狭い。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタの微細化を達成し、電界緩和がなされた、酸化物半導体を用いた半導体装置を提供することを課題の一とする。

【解決手段】ゲート電極の線幅を微細化し、ソース電極層とドレイン電極層の間隔を短縮する。ゲート電極をマスクとして自己整合的に希ガスを添加し、チャネル形成領域に接する低抵抗領域を酸化物半導体層に設けることができるため、ゲート電極の幅、即ちゲート配線の線幅を小さく加工しても位置精度よく低抵抗領域を設けることができ、トランジスタの微細化を実現できる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の不純物分布のバラツキを抑え、STIエッジ部分への電界集中をより効果的に制御でき、実効チャネル幅が狭くなることを抑制できる半導体装置およびその製造方法を提供する。

【解決手段】P型のシリコン基板10の一主面11に、トレンチ22と絶縁物24とを有する素子分離領域25と、素子分離領域25に囲まれた素子領域12であって、シリコン基板10の側面上部17が、トレンチ25に露出した素子領域12を形成し、ゲート絶縁膜40をシリコン基板10の上面14から側面上部17に延在して形成し、N+型ポリシリコン32とN+型ポリシリコン32の両側のP+型ポリシリコン34と、P+型ポリシリコン34の下側の側面上部17に沿って設けられたN+型ポリシリコン36とを有するゲート電極30を形成する。

(もっと読む)

41 - 60 / 168

[ Back to top ]