Fターム[5F083HA02]の内容

Fターム[5F083HA02]に分類される特許

81 - 100 / 1,580

半導体装置

【課題】不揮発性を有し、書き込み回数に制限のない新たな構造の半導体装置を提供する。

【解決手段】複数の記憶素子が直列に接続され、複数の記憶素子の一は、第1〜第3のゲート電極、第1〜第3のソース電極、および第1〜第3のドレイン電極を有する第1〜第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含んで構成され、第1のゲート電極と、第2のソース電極または第2のドレイン電極の一方とは、電気的に接続され、第1の配線と、第1のソース電極と、第3のソース電極とは、電気的に接続され、第2の配線と、第1のドレイン電極と、第3のドレイン電極とは、電気的に接続され、第3の配線と、第2のソース電極または第2のドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のゲート電極とは、電気的に接続され、第5の配線と、第3のゲート電極とは電気的に接続された半導体装置。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

三次元集積回路を作製する方法

【課題】集積回路を作製する新規なタイプの方法を提供する。

【解決手段】少なくとも第3の層がその間に配置された、少なくとも半導体の第1および第2の層を備える基板を作製するステップと、少なくとも第1のMOSデバイスを作製するステップであって、その活性領域が半導体の第1の層の少なくとも一部に形成される、ステップと、少なくとも第2のMOSデバイスを作製するステップであって、その活性領域が半導体の第2の層の少なくとも一部に形成され、第2のMOSデバイスの活性領域が第2のMOSデバイスのゲートと第1のMOSデバイスの活性領域との間に配置される、ステップとを少なくとも含む、集積電子回路を作製する方法。

(もっと読む)

不揮発性半導体記憶装置

【課題】相変化メモリの書き換え電流および書き換え電圧を低減する。

【解決手段】相変化膜を記憶素子として用いた相変化メモリにおいて、相変化膜2a、2bとして、温度低下に対して結晶化領域の抵抗変化が減少する温度領域を持つ材料を用い、かつ相変化膜2a、2bの間に、相変化膜2a、2bよりも大きい熱伝導率と、相変化膜2a、2bよりも小さい抵抗率を有する中間金属膜1を挿入する。そして、書き換え時に発生する相変化膜2a、2b内の熱を中間金属膜1を通じて放熱することにより、相変化膜2a、2b内の熱分布を均一にすると共に、中間金属膜1近傍の相変化膜2a、2bを局所冷却し、高抵抗状態にすることにより、書き換え電流の過剰な増加を抑制する。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】短チャネル効果が抑制され、微細化を実現しつつ、安定した電気的特性を付与する半導体装置を提供する。また、上記半導体装置を作製する。

【解決手段】酸化物絶縁層に設けたトレンチに、トレンチに沿って成膜される酸化物半導体膜と、酸化物半導体膜と接するソース電極及びドレイン電極と、酸化物半導体膜上のゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有する半導体装置(トランジスタ)を設ける。該トレンチは下端コーナ部に曲面を有し、側部が酸化物絶縁層上面に対して略垂直な側面を有する。また、トレンチの上端の幅がトレンチの側面の幅の1倍以上1.5倍以下である。

(もっと読む)

不揮発性半導体記憶装置

【課題】高い信頼性を有し且つ安価な不揮発性半導体記憶装置を提供する。

【解決手段】この不揮発性半導体記憶装置において、メモリストリングスは、基板に対して垂直方向に延びる一対の柱状部、及び前記一対の柱状部の下部を連結させるように形成された連結部を有する半導体層と、前記柱状部の側面を取り囲むように形成された電荷蓄積層と、前記柱状部の側面及び前記電荷蓄積層を含む第1の絶縁膜と、前記柱状部の側面及び前記第1の絶縁膜を覆うように形成された第1導電層と、前記連結部の周囲に形成される第2の絶縁膜と、前記連結部に前記ゲート絶縁膜を介して形成される第2導電層とを備える。

(もっと読む)

半導体装置

【課題】非接触でデータの送受信が可能な半導体装置は、鉄道乗車カードや電子マネーカ

ードなどの一部では普及しているが、さらなる普及のためには、安価な半導体装置を提供

することが急務の課題であった。上記の実情を鑑み、単純な構造のメモリを含む半導体装

置を提供して、安価な半導体装置及びその作製方法の提供を課題とする。

【解決手段】有機化合物を含む層を有するメモリとし、メモリ素子部に設けるTFTのソ

ース電極またはドレイン電極をエッチングにより加工し、メモリのビット線を構成する導

電層とする。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】重畳する第1のトランジスタおよび第2のトランジスタからなる第1のインバータと、重畳する第3のトランジスタおよび第4のトランジスタからなる第2のインバータと、第1の選択トランジスタと、第2の選択トランジスタと、を有し、第1のインバータの出力端子、第2のインバータの入力端子および第1の選択トランジスタのソースおよびドレインの一方が接続され、第2のインバータの出力端子、第1のインバータの入力端子および第2の選択トランジスタのソースおよびドレインの一方が接続されることによって、微細化したSRAM回路を形成する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてエネルギーギャップの異なる少なくとも2層の酸化物半導体層を含み、かつ積層された酸化物半導体層の間に混合領域を有する酸化物半導体積層を用いる。

(もっと読む)

半導体装置およびその作製方法

【課題】高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを有する半導体装置を提供する。

【解決手段】加熱処理により酸素を放出する絶縁体基板と、該絶縁体基板上に設けられた酸化物半導体膜と、を有し、該酸化物半導体膜にチャネルが形成されるトランジスタを有する半導体装置である。加熱処理により酸素を放出する絶縁体基板は、絶縁体基板の少なくとも酸化物半導体膜が設けられる側に、酸素イオン注入を行うことで作製することができる。

(もっと読む)

抵抗変化物質を含む半導体素子及びその製造方法

【課題】抵抗変化物質を含む半導体素子及びその製造方法を提供する。

【解決手段】印加された電圧によって抵抗が変化する抵抗変化物質をチャネル層として含む半導体素子及びその製造方法、前記半導体素子を含む不揮発性メモリ装置に係り、前記半導体素子は、絶縁基板上に配置されたチャネル層、前記チャネル層内に配置されたゲート電極、前記ゲート電極を取り囲むゲート絶縁膜、前記ゲート電極の両側面で、前記チャネル層上に配置されるソース電極及びドレイン電極、並びに前記基板と前記ゲート電極との間に配置される抵抗変化物質層を含み、これにより、前記半導体素子は、スイッチの機能と不揮発性メモリの機能とを同時に遂行することができる。

(もっと読む)

半導体装置

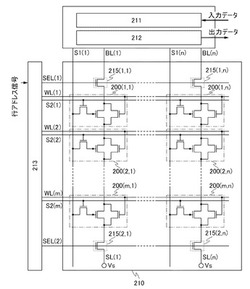

【課題】トランジスタのしきい値電圧のばらつきの影響を緩和し、複数の状態(例えば3以上の状態)の区別を正確、かつ容易にした半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、ワード線と、ビット線とワード線に接続されたメモリセルと、入力されたアドレス信号によって指定されたメモリセルを選択するように、複数の第2信号線及び複数のワード線を駆動する、第2信号線およびワード線の駆動回路と、書き込み電位を第1信号線に出力する、書き込み回路と、指定されたメモリセルに接続されたビット線から入力されるビット線の電位と、複数の読み出し電位とを比較する読み出し回路と、ビット線の電位と複数の読み出し電位の比較結果に基づいて複数の補正電圧のいずれかを選択する制御回路と、書き込み電位及び複数の読み出し電位を生成して、書き込み回路及び読み出し回路に供給する、電位生成回路と、を有する半導体装置。

(もっと読む)

酸化物半導体膜の成膜方法、半導体装置および半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタは、非晶質シリコンを用いたトランジスタと比較して信頼性が劣る場合があった。そこで、信頼性が高い酸化物半導体を用いたトランジスタを有する半導体装置を提供する。

【解決手段】酸化物半導体膜に含まれる水素、窒素および炭素などの不純物は酸化物半導体膜の半導体特性を低下させる要因となる。例えば、酸化物半導体膜に含まれる水素および窒素は、酸化物半導体膜を用いたトランジスタのしきい値電圧をマイナス方向へシフトさせてしまう要因となる。また、酸化物半導体膜に含まれる窒素、炭素および希ガスは、酸化物半導体膜中に結晶領域が生成されることを阻害する。そこで、酸化物半導体膜の不純物濃度を低減することで、高い信頼性を有するトランジスタを作製する。

(もっと読む)

半導体装置およびその駆動方法

【課題】2Tr1C型半導体メモリ装置の消費電力を削減する。

【解決手段】読み出しトランジスタのしきい値の絶対値をビット線のデータ電位の変動幅よりも大きくする(あるいはビット線のデータ電位の変動幅を読み出しトランジスタのしきい値の絶対値よりも小さくする)ことで、ソース線の電位を固定し、また、書き込みワード線の電位変動を小さくでき、読み出しワード線の電位は、読み出しの際にのみ変動させる。また、そのようなしきい値の絶対値の大きなトランジスタは、ゲートの材料を仕事関数の高い窒化インジウム等を用いて形成する。仕事関数の高い材料を用いることで、ゲート絶縁物のポテンシャル障壁が高まり、リーク電流が抑制できるので、電荷保持特性も向上する。

(もっと読む)

半導体記憶装置

【課題】TFTなどのトランジスタ特性がばらつく状況や、RF回路から電源が供給され

電源が安定しない状況で、SRAMを作製する場合、従来の1つのメモリセルに6つのト

ランジスタの構成では読み出し時にメモリセルが保持する値が書き換わる誤書き込みが発

生してしまう。

【解決手段】SRAMのメモリセルは、書き込みの回路と読み出しの回路を分離する事に

より、SRAMの誤書き込みを防ぎ、安定した動作を行うことを可能にする。また、書き

込みのタイミングを考慮する事により、誤書き込みを起こさず、より確実に書き込みの動

作を行うことが可能なSRAMを提供する。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置

を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極およびド

レイン電極と、酸化物半導体層、ソース電極およびドレイン電極を覆うゲート絶縁層と、

ゲート絶縁層上のゲート電極と、を有し、酸化物半導体層の厚さは1nm以上10nm以

下であり、ゲート絶縁層は、ゲート絶縁層に用いられる材料の比誘電率をεr、ゲート絶

縁層の厚さをdとして、εr/dが、0.08(nm−1)以上7.9(nm−1)以下

の関係を満たし、ソース電極とドレイン電極との間隔は10nm以上1μm以下である半

導体装置である。

(もっと読む)

メモリ用シフトレジスタ及びその製造方法

【課題】大容量で、信頼性が高く、少ない工程数で製造可能なメモリ用シフトレジスタを提供する。

【解決手段】一の実施形態によれば、メモリ用シフトレジスタは、基板の主面に平行な第1方向に延び、前記第1方向に垂直な第2方向に向かい合う第1及び第2の制御電極を備える。さらに、前記レジスタは、前記第1及び第2の制御電極間において、前記第1の制御電極側に一列に設けられた複数の第1の浮遊電極を備える。さらに、前記レジスタは、前記第1及び第2の制御電極間において、前記第2の制御電極側に一列に設けられた複数の第2の浮遊電極を備える。さらに、前記第1及び第2の浮遊電極の各々は、前記第1方向に垂直な平面に対し、鏡面非対称な平面形状を有する。

(もっと読む)

半導体装置

【課題】1T−DRAMにおいて、高いGIDL電流は、主にPN接合でのリーク電流によるものであり、データ保持時にリーク電流が発生する原因にもなり、DRAMにおける電荷保持時間を低下させている。

【解決手段】ドレイン拡散層のうちゲート電極とオーバーラップする部分を、不純物濃度の異なる2つの部分に分けている。これら2つの部分のうち、不純物濃度がより低い一方の部分では、ボディ部に隣接しており、電界が低減されるためリーク電流が抑制される。また、不純物濃度がより高い他方の部分では、ボディ部から絶縁されており、ゲート絶縁層との界面において比較的大きなトンネル効果が得られる。その結果、GIDL電流を増大しつつ、PN接合によるリーク電流を抑制し、データ保持時間を増大させることが可能となっている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高集積化に適した不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第3のフィン型積層構造Fin1〜Fin3を有する。第1乃至第3のフィン型積層構造Fin1〜Fin3は、第1の方向に積み重ねられる第1及び第2の半導体層Sm1,Sm2を備える。第1及び第2のアシストゲート電極AG1,AG2は、第3の方向に並んで配置され、第3のフィン型積層構造Fin3の第1の方向にある表面上で互いに分断される。第1のアシストゲートトランジスタAGT1は、第1及び第3のフィン型積層構造Fin1,Fin3内に形成され、第2のアシストゲートトランジスタAGT2は、第2及び第3のフィン型積層構造Fin2,Fin3内に形成される。

(もっと読む)

81 - 100 / 1,580

[ Back to top ]