Fターム[5F083HA02]の内容

Fターム[5F083HA02]に分類される特許

1,561 - 1,580 / 1,580

ブリッジ電界効果トランジスタメモリセル、上記セルを備えるデバイス、および、ブリッジ電界効果トランジスタメモリセルの製造方法

本発明は、第1および第2の各ソース/ドレイン領域、第1および第2の各ソース/ドレイン領域の間に配置されたチャネル領域とを備え、これらの各ソース/ドレイン領域とチャネル領域とが半導体ブリッジに形成されている、ブリッジ電界効果トランジスタメモリセルに関するものである。

本発明のメモリセルは、さらに、半導体ブリッジの少なくとも部分上に堆積されている電荷記憶層と、電荷記憶層の少なくとも一部上の金属性で導電性のゲート領域とを備え、電荷記憶層は、ブリッジ電界効果トランジスタメモリセルに所定の電気的電圧を印加することにより、選択的に、電気的な電荷キャリアが、電荷記憶層に対し導入されるように、または、電荷記憶層から除去されるように配置されている。  (もっと読む)

(もっと読む)

高K誘電体膜

誘電体層(14,22,24,32)は、ランタン、ルテチウム、及び酸素により構成され、かつ2つの導体の間、または導体(14,20,34)と基板(12,26,30)との間に形成される。一の実施形態では、誘電体層は基板を覆って形成され、境界層を追加する必要がない。別の実施形態では、誘電体層(22,42,46)に含まれる元素の分布は、ランタン含有量またはルテチウム含有量に関して傾斜する、または誘電体層(22,42,46)は別の構成として、アルミニウムを含むことができる。更に別の実施形態では、絶縁層を導体または基板と誘電体層との間、または導体及び基板の両方と誘電体層との間に形成する。誘電体層は、分子ビームエピタキシー法によって形成することが好ましいが、原子層化学気相成長、物理気相成長、有機金属化学気相成長、またはパルスレーザ堆積によって形成することもできる。  (もっと読む)

(もっと読む)

極薄シリコンにおけるNROM型フラッシュメモリデバイス

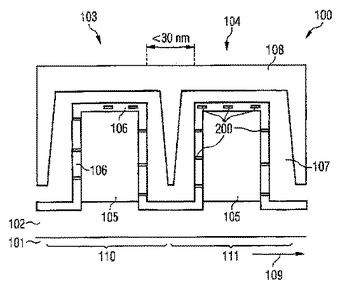

【課題】SOI技術を取り入れたCMOSデバイスにおける浮遊ボディの影響を抑制可能とする。

【解決手段】極薄シリコン・オン・インシュレータ構造においてNROMフラッシュメモリセルを実現する。平面型デバイスでは、ソース/ドレイン領域間のチャネルが通常時に完全空乏化されている。ソース/ドレイン領域と上方のゲート絶縁層との間に酸化物層を形成することで絶縁層を設ける。制御ゲートがゲート絶縁層の上部に形成される。縦型デバイスでは、ソース/ドレイン領域に側面が接する酸化物柱状体を基板から延伸させる。エピタキシャル再成長により、酸化物柱状体の側面に沿って極薄シリコンボディ領域が形成される。本構造の上部には、第2のソース/ドレイン領域が形成される。さらにその上部にゲート絶縁層及び制御ゲートが形成される。

(もっと読む)

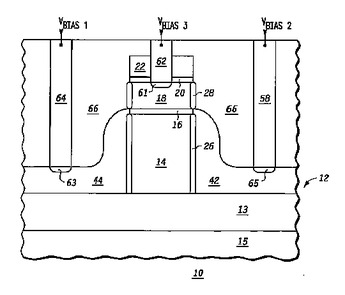

3つの電気絶縁電極を有するトランジスタ及びトランジスタの形成方法

トランジスタ(10)は別々に制御することができるゲート(44,42,18)を有するように形成される。3つのゲート領域は異なる電位でバイアスすることができ、かつこれらのゲート領域は異なる伝導特性を持つことができる。チャネルサイドウォール上の誘電体はチャネル上部の上の誘電体と異ならせることができる。ソース、ドレイン、及び3つのゲートとの電気コンタクトは別々に取る。ナノクラスター(143,144)のような電荷蓄積層をトランジスタのチャネルに隣接するように設け、そして電荷蓄積層を3つのゲート領域を通して制御することにより、揮発性メモリセル及び不揮発性メモリセルの両方を同じプロセスを使用して実現することにより世界共通のメモリプロセスを提供する。揮発性セルとして用いる場合、トランジスタの高さ、及びチャネルサイドウォール誘電体の特性によって記憶保持特性を制御する。不揮発性セルとして用いる場合、トランジスタの幅、及びチャネルを覆う誘電体の特性によって記憶保持特性を制御する。  (もっと読む)

(もっと読む)

完全空乏型シリコン・オン・インシュレータのCMOSロジック

【課題】SOI技術を用いた部分空乏型CMOSデバイスにおける浮遊ボディの不必要な影響を制御可能とする。

【解決手段】シリコン・オン・インシュレータのCMOSメモリデバイスにおいて、引き出し線を含む領域が用いられる。引き出し線を逆方向にバイアスすることで、部分空乏型メモリセルのボディ領域から少数キャリアを取り除く。これにより、ボディ領域を完全空乏化し、浮遊ボディの不必要な影響を抑制する。

(もっと読む)

短チャネル効果を減少させる埋め込みチャネルフラッシュ構造

短チャネル効果を減少させたメモリセルを記載する。ソース領域(54)およびドレイン領域(56)を半導体ウェーハ(58)中に形成する。ソース領域(54)およびドレイン領域(58)の間にトレンチ領域(59)を形成する。このトレンチ領域、ソース領域およびドレイン領域の下に埋め込みチャネル領域(52)を形成する。半導体基板のトレンチ領域中にゲート絶縁層(60)を形成する。このゲート絶縁層は、埋め込みチャネル領域上に、およびソース領域とドレイン領域との間に形成される。埋め込みチャネル領域の上の半導体基板上に、制御ゲート層(70)を形成する。この制御ゲート層は、ゲート絶縁層によって埋め込みチャネルから分離される。  (もっと読む)

(もっと読む)

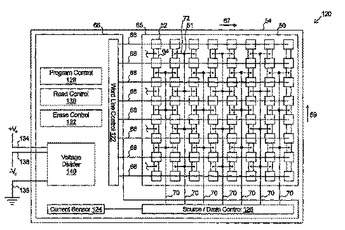

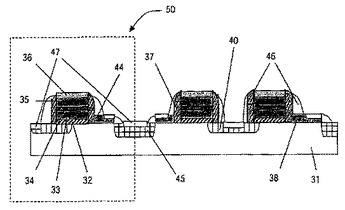

スタガー式ローカル接続構造を持つメモリセルアレイ

メモリセルアレイ(50)は、半導体基板(54)に製造された、2次元アレイのメモリセル(52)を含む。メモリセル(52)は、行方向(67)を形成する複数の行と、列方向(69)を形成する複数の列で並べられている。メモリセル(52)の各列は、複数の交互に配置されたチャネル領域(58)及びソース/ドレイン領域(64)を含む。各ソース/ドレイン領域(64)上には導電性インターコネクト(72)が配置されており、この導電性インターコネクト(72)はただ1つのその他のソース/ドレイン領域(64)に結合する。この1つのソース/ドレイン領域(64)とは、その列に隣接する第2の列に存在する領域である。導電性インターコネクト(64)は、1つおきの導電性インターコネクト(64)がその列の右側に隣接する列に接続するように、また、1つおきの導電性インターコネクトが、その列の左側に隣接する列に接続するように、配置される。複数のソース/ドレインコントロールライン(70)は、隣接するメモリセル(52)の列間に延在し、また、その隣接する列と列との間を結合する各導電性インターコネクト(72)に電気的に結合する。  (もっと読む)

(もっと読む)

増大されたセル比を有する6トランジスタFINFET型CMOSスタティックRAMセル

本発明に係るCMOSスタティックRAMセルは、2つのアクセスデバイスであり、各々のアクセスデバイスが単一のフィンを有する3ゲートトランジスタから成るところの2つのアクセスデバイス;2つのプルアップデバイスであり、各々のプルアップデバイスが単一のフィンを有する3ゲートトランジスタから成るところの2つのプルアップデバイス;及び2つのプルダウンデバイスであり、各々のプルダウンデバイスが複数のフィンを有する3ゲートトランジスタから成るところの2つのプルダウンデバイスを有する。さらに、2つのフィンを有する3ゲートトランジスタを備えたCMOSスタティックRAMセルの製造方法が提供される。  (もっと読む)

(もっと読む)

2−トランジスタメモリセル及びその製造方法

本発明は、メモリゲートスタック(1)を有する記憶トランジスタ(1)及び選択トランジスタを有する2-トランジスタメモリセルを基板(50)上に製造する方法であって、トンネル誘電層(51)が前記基板(50)と前記メモリゲートスタック(1)との間にもたらされる方法を提供する。前記方法は、第一の導電層(52)及び第二の導電層(54)をもたらし、前記第二の導電層(54)をエッチし、それによってコントロールゲートを形成し、前記第一の導電層(52)をエッチし、それによってフローティングゲートを形成することによって前記メモリゲートスタック(1)を形成するステップを有する。前記方法は更に、前記第一の導電層(52)がエッチされる前に、前記トンネル誘電層(51)の下に形成されるべきチャネルの方向で前記コントロールゲートに対してスペーサ(81)を形成するステップと、その後、前記第一の導電層(52)をエッチするために前記スペーサ(81)をハードマスクとして使用し、それによって前記フローティングゲートを形成し、それによってフローティングゲートをコントロールゲートに自己整合させるステップとを有することを特徴とする。本発明は、前記コントロールゲート(54)は前記フローティングゲート(52)よりも小さくなり、スペーサ(81)が、前記コントロールゲート(54)に隣接してもたらされるメモリセルも提供する。  (もっと読む)

(もっと読む)

不揮発性メモリ装置を製造する方法及びそれによって得られるメモリ装置

本発明は、ダブル・ゲート・スタック及びシングル・アクセス・ゲートを備える不揮発性メモリ・セル(50)を加工する方法に関する。この方法は、アクセス・ゲートを加工する方法を、自己整合的な、ソース注入とは別のドレイン注入と組み合わせる。本発明の方法は、マスク位置合せ精度を考慮せずに、メモリ装置を消去するための延長されたドレインを自己整合的に注入することを可能にする。さらに、この方法は、さらなるマスクを使用せずにドレイン及びソース注入を互いに異なるドーピングで実施する方法を提供する。  (もっと読む)

(もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

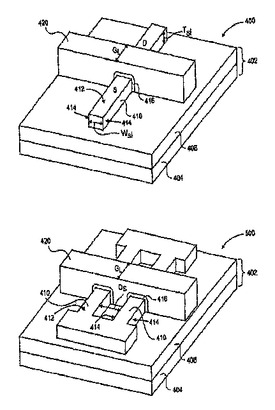

並列相補型FinFETの対を有する集積回路構造体及び該形成方法

【課題】 従来の単一のFinFETのスペースに2またはそれ以上のFinFETを形成すること。

【解決手段】 相補的フィン型電界効果トランジスタ(FinFET)を用いる集積回路構造体のための方法および構造体を開示する。本発明は、第1フィン(100)を含む第1型FinFETと、第1フィン(100)に並列に延在する第2フィン(102)を含む第2型FinFETを含む。また、本発明は、第1型FinFETおよび第2型FinFETのソース/ドレイン領域(130)の間に配置される絶縁体フィンを含む。第1型FinFETと第2型FinFETとの間隔が1個のフィンの幅とほぼ等しくなるように、絶縁体フィンは、第1フィン(100)および第2フィン(102)とほぼ同じ寸法の幅にされる。また、本発明は、第1型FinFETおよび第2型FinFETのチャネル領域を覆うように形成された共通ゲート(106)を含む。ゲート(106)は、第1型FinFETに隣接する第1不純物ドーピング領域と、第2型FinFETに隣接する第2不純物ドーピング領域とを含む。第1不純物ドーピング領域と第2不純物ドーピング領域の差異が、ゲートに、第1型FinFETと第2型FinFETとの差異に関係した異なる仕事関数を与える。第1フィン(100)および第2フィン(102)はほぼ同じ幅である。

(もっと読む)

不揮発性メモリデバイス

不揮発性メモリデバイス(100)は、基板(110)、絶縁層(120)、フィン(210)、複数の誘電層(310〜330)及び制御ゲート(510/520)を備える。絶縁層(120)は、基板(110)上に形成され、フィン(210)は、絶縁層(120)上に形成される。誘電層(310〜330)は、このフィン(210)を覆うように形成され、制御ゲート(510/520)は、誘電層(310〜330)上に形成される。誘電層(310〜330)は、メモリデバイス(100)の電荷格納構造として機能する酸化物−窒化物−酸化物層を備える。  (もっと読む)

(もっと読む)

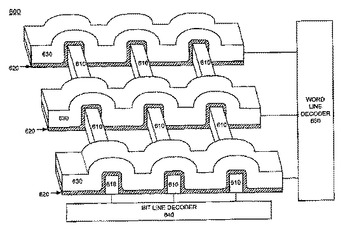

電荷蓄積場所を有するメモリ

メモリは、チャネル領域(1725)を含む半導体構造(1105)の対向する側壁に隣接するゲート構造と、ゲート構造と対向する側壁との間にある複数の電荷蓄積場所(1713、1715、1709及び1711)とを有する。チャネル領域は、2つの電流端子領域間に配置され、それらの電流端子領域は一例ではソース/ドレイン領域としての役割を果たす。メモリセルは、メモリセルのアレイ(1801)内に実装することができ、一方のゲート構造が1つのワード線に結合され、他方のゲート構造が別のワード線に結合される。一例では、各セルは、それぞれが1ビットのデータを記憶する、4つの電荷蓄積場所を含む。  (もっと読む)

(もっと読む)

個別ゲート構造を備えたトランジスタ

個別ゲート構造(701,703)を備えたトランジスタを形成する方法。これらのゲート構造はそれぞれ、半導体構造(105)の複数の側壁に隣接する。本方法は、ゲート材料層(203)を含む少なくとも一つの共形な層を、チャネル領域を含む半導体基板の上に堆積させることを含む。平坦層(403)がウェハの上に形成される。平坦層は、基板上の所定の位置において少なくとも一つの共形な層の頂部表面よりも低い位置に頂部表面を有する。少なくとも一つの共形な層をエッチングすることにより、半導体構造の上のゲート材料は除去される。  (もっと読む)

(もっと読む)

1T‐nメモリセル積層構造体

本発明は、クロスポイントと1T‐1セルとの双方の設計に基づくある種の利点を導入するためのメモリ技術及びメモリアレイに関する新規な変更に関する。これらの設計のある特徴を組み合わせることにより、1T‐1セル設計における読出し時間の高速化及び信号対雑音比の増大と、クロスポイント設計における高記録密度化との双方が達成される。そのために、単一のアクセストランジスタ16を用いて、“Z”軸方向に配置された複数のメモリアレイ層で垂直方向に互いに上下に積み重ねうる多重メモリセルを読出すようにする。  (もっと読む)

(もっと読む)

半導体メモリ素子及び該素子を動作させる方法

【課題】 行と列のマトリクスに配置された複数の半導体ダイナミック・ランダム・アクセス・メモリセルを含む半導体メモリアレイを提供する。

【解決手段】 第1の実施例では、本発明はメモリ素子とメモリ素子のメモリセルからデータを読み取る及びメモリセルにデータを書き込む技術を対象としている。この点において、本実施形態の本実施例の1つの実施形態では、メモリ素子及びその素子を動作させる技術は、電荷ポンピング現象の衰弱効果を最小限にする、削減する及び取り除く。本発明の本実施形態は、振幅及び/又は極性の遷移を最小限にする、削減する及び/又は取り除く制御信号を採用する。別の実施形態では、本発明は行と列のマトリクスに配置された複数の半導体ダイナミック・ランダム・アクセス・メモリを含むメモリアレイを含む半導体メモリ素子である。それぞれの半導体ダイナミック・ランダム・アクセス・メモリセルは、ソース領域、ドレイン領域、ソース領域とドレイン領域の間に及びそれらに隣接して配置される電気的浮体領域、及びそのボディ領域から離れ、及びそれと容量結合されたゲートを有するトランジスタを含む。それぞれのトランジスタは、ボディ領域の第1の電荷を表す第1の状態、及びボディ領域の第2の電荷を表す第2のデータ状態を含む。さらに、半導体ダイナミック・ランダム・アクセス・メモリセルのそれぞれの行は、関連する行の半導体ダイナミック・ランダム・アクセス・メモリセルだけに結合される関連するソース線を含む。

(もっと読む)

半導体メモリセル、アレイ、構造及び素子、及びこれらを動作させる方法

【課題】 第1のデータ状態と第2のデータ状態を保存する半導体ダイナミック・ランダム・アクセス・メモリセルを提供する。

【解決手段】 ここには、多くの発明が記載され及び示されている。第1の側面では、本発明はメモリセル及びメモリセルからデータを読み取る及びメモリセルへデータを書き込む技術を対象としている。これに関して、本発明の本側面の1つの実施形態では、メモリセルは相補的なデータ状態を保存する2つのトランジスタを含む。つまり、2つのトランジスタを持つメモリセルは、第2のトランジスタに対する相補的な状態を維持する第1のトランジスタを含む。そのため、プログラムされるとき、メモリセルのトランジスタの1つが論理低(バイナリ「0」)を保存し、及びメモリセルの他のトランジスタが論理高(バイナリ「1」)を保存する。2つのトランジスタを持つ相補的なメモリセルのデータ状態は、相補的なメモリセルの各トランジスタに保存された論理状態の極性をサンプリングする、検出する、測定する及び/又は検知することにより読み取られる及び/又は決定される。つまり、2つのトランジスタを持つ相補的なメモリセルは、2つのトランジスタに保存される信号(電流又は電圧)の差異をサンプリングする、検出する、測定する及び/又は検知することにより読み取られる。

(もっと読む)

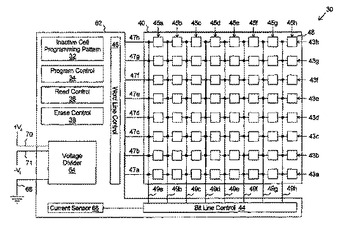

非揮発性メモリセルアレイの非活性領域に隣接する非揮発性メモリセルを読み出すための改善された方法

メモリセル48のアレイ30にデータパターンをストアし、再生するための方法であり、活性コラム45b及び45gと、不活性コラム45c及び45fとを含み、活性コラム45b及び45gにデータパターンをストアする。不活性メモリセルプログラミングパターン32が識別される。バルク消去中、過消去及び活性メモリセル48への電流リークを回避するために定期的に電荷をストアする目的で電荷がストアされる、不活性コラム45c及び45fのメモリセル48の全てあるいは選択された複数のメモリセルを、前述の不活性メモリセルプログラミングパターン32が識別する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 より優れたソフトエラー耐性を有するSOI基板を用いた高信頼性のCMOS・SRAMセルを備える半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 SOI基板の表面半導体層上にゲート絶縁膜を介して形成されたゲート電極と、該ゲート電極の両側の表面半導体層に形成された第1導電型ソース/ドレイン領域とから構成される半導体装置であって、前記第1導電型ソース/ドレイン領域の双方又は一方に接して第2導電型引出拡散層が形成され、少なくとも前記第1導電型ソース/ドレイン領域上から第2導電型引出拡散層上にわたってシリサイド層が形成されており、シリサイド層に接地電位が与えられてなる半導体装置。

(もっと読む)

1,561 - 1,580 / 1,580

[ Back to top ]