Fターム[5F083JA04]の内容

半導体メモリ (164,393) | 材料 (39,186) | キャパシタ絶縁膜材料、ゲート絶縁膜材料 (10,102) | 酸化物系 (9,104) | 酸化膜を含む複合膜 (2,564) | シリコン酸化膜とシリコン窒化膜による複合膜 (1,945)

Fターム[5F083JA04]に分類される特許

141 - 160 / 1,945

半導体装置

【課題】半導体装置を小型化する。また、メモリセルを有する半導体装置の駆動回路の面積を縮小する。

【解決手段】少なくとも第1の半導体素子を有する素子形成層と、素子形成層上に設けられた第1の配線と、第1の配線上に設けられた層間膜と、層間膜を介して第1の配線と重畳する第2の配線と、を有し、第1の配線と、層間膜と、第2の配線と、は、第2の半導体素子を構成し、第1の配線と、第2の配線と、は、同電位が供給される配線である半導体装置である。

(もっと読む)

半導体装置

【課題】ラッチ型メモリが搭載されたCPUを動作させるに際して、処理内容に応じて常時記憶方式と終了時記憶方式のいずれかを選択し、ラッチ型メモリが搭載されたCPUの消費電力を低減する。

【解決手段】ラッチ型メモリが搭載されたCPUを動作させるに際して、電源のオンオフの繰り返し動作が多い場合には常時記憶方式とし、電源のオンオフの繰り返し動作が少ない場合には終了時記憶方式とする。常時記憶方式と終了時記憶方式のどちらを選択するかは、消費電力に応じて決定したしきい値をもとにして決定する。

(もっと読む)

メモリ装置、及びメモリ装置の作製方法

【課題】可能な限り占有面積が削減され、データ保持期間の極めて長いメモリ装置を提供する。

【解決手段】メモリ装置内のメモリ素子のセルトランジスタとして、リーク電流の極めて小さいトランジスタを用いる。さらにメモリセルの占有面積を縮小するために、ビット線とワード線とが交差する領域に、当該トランジスタのソース及びドレインが縦方向に積層されるように形成すればよい。さらにキャパシタは、当該トランジスタの上方に積層すればよい。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

半導体装置及びその駆動方法

【課題】信号処理回路に対する電源電圧の供給及び遮断を選択することができるスイッチとして機能する回路(電源供給制御回路)として好ましい回路を提供する。

【解決手段】信号処理回路に対する電源電位の供給を担う第1の配線と、電源電位を供給する第2の配線との電気的な接続を制御するトランジスタ、及び、信号処理回路に対する電源電位の供給を担う第1の配線を接地させるか否かを制御するトランジスタとを設け、当該2つのトランジスタの少なくとも一方として、チャネルが酸化物半導体層に形成されるトランジスタを適用する。これにより、2つのトランジスタの少なくとも一のカットオフ電流に起因する消費電力を低減することが可能となる。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】記憶回路におけるデータの保持期間を長くする。また、消費電力を低減する。また、回路面積を小さくする。また、1回のデータの書き込みに対する該データの読み出し可能回数を増やす。

【解決手段】記憶回路を具備し、記憶回路は、ソース及びドレインの一方にデータ信号が入力される第1の電界効果トランジスタと、ゲートが第1の電界効果トランジスタのソース及びドレインの他方に電気的に接続される第2の電界効果トランジスタと、一対の電流端子を有し、一対の電流端子の一方が第2の電界効果トランジスタのソース又はドレインに電気的に接続される整流素子と、を備える。

(もっと読む)

半導体装置

【課題】連想メモリは一つのメモリセル内の素子数が多く、一つのメモリセルの面積が大きくなりやすい。そこで、一つのメモリセルの面積を小さくする。

【解決手段】読み出し用のトランジスタのチャネル容量(ゲート電極とチャネル形成領域との間の容量)を用いて電荷の保持を行う。つまり、読み出し用のトランジスタを電荷保持用のトランジスタとして兼用する。また、読み出し用且つ電荷保持用のトランジスタのゲートに電荷供給用のトランジスタのソース又はドレインの一方を電気的に接続する。

(もっと読む)

半導体記憶装置

【課題】電荷蓄積層及び制御ゲートを有する半導体記憶装置のバックバイアス効果による影響を低減させることにより集積度を向上させ、占有面積を増加させずに浮遊ゲートと制御ゲートとの容量の比をより一層増大させるとともに、製造プロセスに起因するセル特性のばらつきが抑制された半導体記憶装置を提供する。

【解決手段】半導体基板と、少なくとも1つの島状半導体層110、該島状半導体層110の側壁の周囲の全部又は一部に形成された電荷蓄積層513及び制御ゲート523から構成される少なくとも1つのメモリセルとを有する半導体記憶装置であって、前記メモリセルの島状半導体層110が不純物拡散層により前記半導体基板から電気的に絶縁されてなる。

(もっと読む)

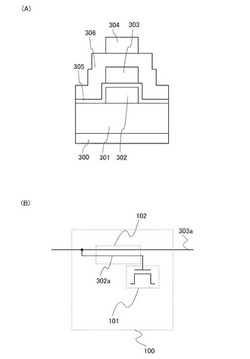

記憶装置及び半導体装置

【課題】データの保持期間を確保しつつ、単位面積あたりの記憶容量を高めることができる記憶装置を提供する。

【解決手段】複数のビット線を幾つかのグループに分割し、複数のワード線も幾つかのグループに分割する。そして、一のグループに属するビット線に接続されたメモリセルには、一のグループに属するワード線が接続されるようにする。さらに、複数のビット線は、複数のビット線駆動回路102a,102b,102cによってグループごとにその駆動が制御されるようにする。加えて、複数のビット線駆動回路102a,102b,102cと、ワード線駆動回路101とを含めた駆動回路上に、セルアレイ103a,103b,103cを形成する。駆動回路とセルアレイ103a,103b,103cが重なるように三次元化することで、ビット線駆動回路が複数設けられていても、記憶装置の占有面積を小さくすることができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置

【課題】占有面積が小さく、冗長性があり、かつリーク電流の小さい保護回路を提供する。

【解決手段】保護回路は、複数の非線形素子が重畳するように積層され、かつ該非線形素子が電気的に直列接続されている構成であり、該保護回路に含まれる少なくとも一つの非線形素子は、チャネル形成領域に酸化物半導体を用いたトランジスタをダイオード接続した素子であり、他の非線形素子は、チャネル形成領域にシリコンを用いたトランジスタをダイオード接続した素子、または、接合領域にシリコンを用いたダイオードとする。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

半導体装置、記憶装置および半導体装置の作製方法

【課題】書き込み回数に制限がなく、消費電力が低く、記憶内容(電荷)の保持特性が改善され、かつ小型化に適した構造の半導体装置および、当該半導体装置を備える、消費電力が低く、記憶内容(電荷)の保持特性が改善された記憶装置を提供する。

【解決手段】半導体装置の有するトランジスタの半導体層として酸化物半導体を用いることで、ソースとドレイン間のリーク電流を低減できるため、半導体装置および当該半導体装置を備える記憶装置の消費電力低減、保持特性の改善を達成できる。また、トランジスタのドレイン電極、半導体層およびドレイン電極と重なる第1の電極により容量素子を形成し、容量素子と重なる位置でゲート電極を上層へ取り出す構造とした。これにより、半導体装置および当該半導体装置を備える記憶装置を小型化できる。

(もっと読む)

不揮発性半導体記憶装置

【課題】複数のメモリストリングのうち特定のメモリストリングに対して選択的に消去動作を実行可能な不揮発性半導体記憶装置を提供する。

【解決手段】一態様に係る不揮発性半導体記憶装置は、メモリセルアレイ、複数のメモリストリング、ドレイン側選択トランジスタ、ソース側選択トランジスタ、複数のワード線、複数のビット線、ソース線、ドレイン側選択ゲート線、ソース側選択ゲート線、及び制御回路を有する。制御回路は、選択したビット線に第1電圧を印加して当該ビット線に接続されたメモリストリングに対し消去動作を実行する一方、非選択としたビット線に第2電圧を印加して当該ビット線に接続されたメモリストリングに対し消去動作を禁止する。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、容量素子と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、信号線及びワード線に接続された第2のトランジスタと、ワード線、に接続された容量素子とを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方とが接続された、半導体装置。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果を抑制しつつ微細化を達成した半導体装置およびその作製方法を提供することを目的の一とする。

【解決手段】絶縁層にトレンチを形成し、トレンチの上端コーナー部と接する酸化物半導体膜に不純物を添加し、ソース領域およびドレイン領域を形成する。上記構造にすることで微細化することが可能である。また、トレンチを有することで、ソース電極層とドレイン電極層との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果を抑制することができる。

(もっと読む)

半導体装置

【課題】ワード線の負荷を増大させることなく、ワード線に生じるノイズを低減する。

【解決手段】少なくとも一のスイッチング素子を有する複数の記憶素子がマトリクス状に配置され、前記記憶素子のそれぞれにはワード線とビット線がそれぞれ接続され、前記ワード線には少数キャリアが実質的に存在しないトランジスタのゲート(またはソース及びドレイン)が接続され、前記少数キャリアが実質的に存在しないトランジスタのソース及びドレイン(またはゲート)の電位が制御されることで前記少数キャリアが実質的に存在しないトランジスタの容量値の制御を行う半導体装置とする。前記少数キャリアが実質的に存在しないトランジスタは、ワイドギャップ半導体により設けられていればよい。

(もっと読む)

半導体装置およびその製造方法

【課題】FMONOSメモリセルとCMOSトランジスタが共存する半導体装置において、トランジスタの駆動電流を高めるとともにFMONOSメモリセルとしての機能を確保する半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、主表面上に形成された、チャネルを有するMONOS型メモリセルと、主表面上に形成されたnチャネル型トランジスタと、主表面上に形成されたpチャネル型トランジスタとを備える半導体装置である。上記MONOS型メモリセル、nチャネル型トランジスタおよびpチャネル型トランジスタの上面に接するように窒化膜CS1、CS2が形成されている。上記窒化膜CS1、CS2はMONOS型メモリセル、nチャネル型トランジスタおよびpチャネル型トランジスタのチャネルに応力を付加する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート電極用溝18の底部に設けられた第1の不純物拡散領域27と、第1の側面18aに配置されたゲート絶縁膜21の上部21Aを覆うように、半導体基板13に設けられた第2の不純物拡散領域28と、少なくとも第2の側面18bに配置されたゲート絶縁膜21を覆うように半導体基板13に設けられ、第1の不純物拡散領域27と接合された第3の不純物拡散領域29と、を有する。

(もっと読む)

141 - 160 / 1,945

[ Back to top ]