Fターム[5F083JA04]の内容

半導体メモリ (164,393) | 材料 (39,186) | キャパシタ絶縁膜材料、ゲート絶縁膜材料 (10,102) | 酸化物系 (9,104) | 酸化膜を含む複合膜 (2,564) | シリコン酸化膜とシリコン窒化膜による複合膜 (1,945)

Fターム[5F083JA04]に分類される特許

101 - 120 / 1,945

半導体装置

【課題】良好な特性を維持しつつ微細化を達成した半導体装置の提供と、さらに、これらの微細化を達成した半導体装置の良好な特性を維持しつつ、3次元高集積化を図る。

【解決手段】絶縁層中に埋め込まれた配線と、絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極及びドレイン電極と、酸化物半導体層と重畳して設けられたゲート電極と、酸化物半導体層と、ゲート電極との間に設けられたゲート絶縁層と、を有し、絶縁層は、配線の上面の一部を露出するように形成され、配線は、その上面の一部が絶縁層の表面の一部より高い位置に存在し、且つ、絶縁層から露出した領域において、ソース電極またはドレイン電極と電気的に接続し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さが1nm以下である半導体装置である。

(もっと読む)

半導体記憶装置

【課題】制御ゲート電極と浮遊ゲート電極との間のカップリングを確保しつつ、浮遊ゲート電極間の干渉を抑制することができる半導体記憶装置を提供する。

【解決手段】アクティブエリア12上に設けられたトンネル膜13と、前記トンネル膜上に設けられた浮遊ゲート電極14と、前記浮遊ゲート電極上に設けられ、前記第1方向に対して交差した第2方向に延びる電極間絶縁膜18と、制御ゲート電極19と、前記第2方向において隣り合う前記アクティブエリア間、前記トンネル膜間及び前記浮遊ゲート電極間に設けられた下側絶縁部16と、前記下側絶縁部と前記電極間絶縁膜との間に設けられ、上面が前記浮遊ゲート電極の上面よりも上方に位置している上側絶縁部17と、を備える。前記下側絶縁部は気体部分を有する。そして、前記上側絶縁部の比誘電率は前記下側絶縁部の比誘電率よりも高く、前記電極間絶縁膜の比誘電率は前記上側絶縁部の比誘電率よりも高い。

(もっと読む)

半導体装置の製造方法

【課題】スループットを低下させずに異なるメモリセルの誘電体膜とキャパシタの誘電体膜を同時に形成するための半導体装置の製造方法を提供する。

【解決手段】第1酸化膜18、窒化膜19、第2酸化膜20を順に形成した第1の誘電体膜を第1の半導体膜16上に形成する工程と、第1領域I内の第1の誘電体膜21をエッチングする工程と、第1領域Iの半導体基板1の表面に第3酸化膜25を形成する工程と、第1領域VI及び第2領域IIIに開口部28a、28bを有し、さらに第3領域II内の第1の誘電体膜21を覆う形状を有するマスク28を半導体基板1の上方に形成する工程と、マスク28の開口部28a、28bを通して、第1領域VI内の前記第3酸化膜25と前記第2領域III内の第1の誘電体膜21の第2酸化膜20を同時にエッチングする工程を含む。

(もっと読む)

メモリストリングにダイオードを有する3次元アレイのメモリアーキテクチャ

【課題】信頼でき、非常に小型の3次元集積回路メモリ用の構造を低い製造コストで提供する。

【解決手段】3次元アレイは第1の端部と第2の端部を含む2つの端部を有し、第1の端部と第2の端部の一方はビット線BLに接続され、第1の端部と第2の端部の他方はソース線CSLに接続される不揮発性メモリセルのNANDストリングのスタック1412、1413、1414と、ビット線BL及びソース線SLの一方をメモリセルのストリング1412、1413、1414に接続させるダイオード1492を有する。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲートトランジスタのゲート電極間の間隔の縮小を実現する不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板に、複数の第1の素子領域と、素子分離領域と、第2の素子領域を形成する。第1の素子領域上に、メモリセルゲート電極、2本の選択ゲート電極を形成し、第2の素子領域に周辺ゲート電極を形成する。第1の絶縁膜を形成し、周辺ゲート電極の側壁部上が開口される第1のレジストパターンを形成し、第1のエッチング処理を行い、側壁絶縁膜を形成する。第2のレジストパターンを形成し、第2のエッチング処理を行い、選択ゲート電極側壁部の第1の絶縁膜を除去する。第2の絶縁膜を堆積し、第3の絶縁膜を堆積する。2本の選択ゲート電極間上が開口される第3のレジストパターンを形成し、第3のエッチングおよび第4のエッチング処理を行い、コンタクトホールを形成する。

(もっと読む)

半導体装置、電子装置、配線基板、半導体装置の製造方法、及び配線基板の製造方法

【課題】配線基板に半導体素子を形成する場合において、配線基板の製造工程数を少なくする。

【解決手段】コア層200の一面上には、第1配線232が設けられている。第1配線232上、及びその周囲に位置するコア層200の一面上には、半導体層236が形成されている。第1配線232及び半導体層236は、半導体素子を形成している。本実施形態において半導体素子は、第1配線232をゲート電極としたトランジスタ230であり、半導体層236と第1配線232の間に、ゲート絶縁膜234を有している。

(もっと読む)

半導体素子の製造方法

【課題】400℃以上の温度で原子層蒸着法により蒸着が可能な前駆体を用いて高密度を有する非晶質の高誘電絶縁膜形成を通じてキャパシタンス等価厚及び漏洩電流特性を向上させることができる半導体素子の製造方法を提供する。

【解決手段】半導体基板100上にZr[C5H4(CH3)]2(CH3)2、Zr[C5H4(CH3)]2(OCH3)CH3及びZr[C5H4(CH2CH3)][N(CH3)(CH2CH3)]3の何れか一つの前駆体を用いて400℃〜500℃の温度で形成されたジルコニウム酸化膜(ZrO2)140を含む高誘電絶縁膜を形成することを特徴とする。

(もっと読む)

半導体記憶装置

【課題】3次元型の半導体記憶装置のパフォーマンスを向上させる。

【解決手段】実施形態によれば、半導体記憶装置は、半導体基板と、半導体基板上に設けられ、積層された複数のメモリセルを含む複数のメモリユニットと、カラム方向に配列された複数のメモリユニット上に複数本形成されたビット線とを備え、複数のビット線のロウ方向の配列ピッチは、メモリユニットのロウ方向の配列ピッチよりも小さく、カラム方向に配列された各メモリユニットの端部は、複数本形成されたビット線のいずれか1つに接続される。

(もっと読む)

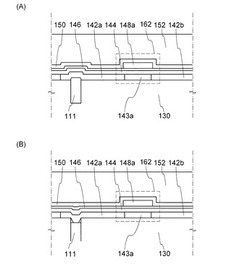

半導体装置

【課題】電力供給がない状況で記憶保持が可能で、書き込み回数に制限が無い、新たな半導体装置を提供する。

【解決手段】チャネル領域と第1のゲート絶縁層と第1のゲート電極と第1のソース及びドレイン電極とを有する第1のトランジスタと、酸化物半導体層140と第2のソース電極142a及び第2のドレイン電極142bと第2のゲート絶縁層146と第2のゲート電極148aとを有する第2のトランジスタ162と、第2のソース電極142aまたは第2のドレイン電極142bの一方と第2のゲート絶縁層146と第2のゲート絶縁層146上に第2のソース電極142a又は第2のドレイン電極142bの一方と重なるように設けられた第3の電極148bとを有する容量素子164と、を有し、第1のゲート電極と第2のソース電極142a又は第2のドレイン電極142bの一方とは接続され、第3の電極148bは酸化物半導体層140と重なる領域を有する。

(もっと読む)

半導体装置

【課題】消去特性と消去ディスターブ特性との双方を向上することが可能な、MONOS型メモリセルなどの半導体装置を提供する。

【解決手段】半導体基板SUBの主表面に形成される第1のゲート電極CGと、主表面上において第1のゲート電極CGと隣接するように形成された第2のゲート電極MGと、第2のゲート電極MGと半導体基板SUBとに挟まれた領域から、第1のゲート電極CGと第2のゲート電極MGとに挟まれた領域に連なるように延びる絶縁膜ONOと、第1および第2のゲート電極CG,MGの真下のチャネル領域を挟むように、主表面に形成される1対のソース/ドレイン領域NR1,NR2とを備える。上記ソース領域NR1は、第1のソース領域N11および第2のソース領域N12を含んでいる。上記第2のソース領域N12は第1のソース領域N11よりも主表面から深い領域に形成されている。上記第1のソース領域N11と第2のソース領域N12とに含まれる不純物の材質が異なっている。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜に酸素ドープ処理を行って、第1の絶

縁膜に酸素原子を供給し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに

、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半

導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された

酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜上の酸化物半導体膜と重畳す

る領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】選択用トランジスタのゲート電極と記憶用トランジスタのゲート電極との間の耐圧を確保し、かつ閾値電圧の変動が抑制されたMONOS型メモリセルを提供する。

【解決手段】主表面SBSを有する半導体基板SUBと、主表面SBS上に形成された第1のゲート電極CGと、主表面SBS上において第1のゲート電極CGと隣接するように形成された第2のゲート電極MGと、第2のゲート電極MGと半導体基板SUBとに挟まれた領域から、第1のゲート電極CGと第2のゲート電極MGとに挟まれた領域に連なるように延びる第1の絶縁膜ONOとを備える半導体装置である。上記第2のゲート電極MGの最上面MGSは第1のゲート電極CGの最上面CGSより低くなっている。上記第2のゲート電極MGの最上面MGSは主表面SBSに沿うように形成されている。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1及び第2のノードを有する論理回路と、第1のノードに接続された第1の記憶回路と、第2のノードに接続された第2の記憶回路と、第1のノード、第2のノード、第1の記憶回路、及び第2の記憶回路に接続されたプリチャージ回路と、を有し、読み出しの際に、プリチャージ回路は、プリチャージ電位を第1のノード及び第2のノードに出力し、第1の記憶回路及び第2の記憶回路は、チャネルが酸化物半導体膜に形成されるトランジスタを含む記憶装置である。

(もっと読む)

信号処理回路及びその駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路の提供する。

【解決手段】入力された信号の位相を反転させて出力する論理素子を2つ(第1の位相反転素子及び第2の位相反転素子)と、第1の選択トランジスタと、第2の選択トランジスタと、を有する記憶素子であって、酸化物半導体層にチャネルが形成されるトランジスタと容量素子との組を2つ(第1のトランジスタと第1の容量素子との組、及び第2のトランジスタと第2の容量素子との組)有する。そして、信号処理回路が有する記憶装置に上記記憶素子を用いる。例えば、信号処理回路が有するレジスタ、キャッシュメモリ等の記憶装置に上記記憶素子を用いる。

(もっと読む)

半導体装置の製造方法

【目的】幅寸法が異なるワード線に対する書き込み電圧の設定の適正化を図ることが可能な半導体装置の製造方法を提供することを目的とする。

【構成】実施形態の半導体装置の製造方法は、線幅の異なる複数のワード線の組が繰り返し配置された半導体記憶装置における全ページのそれぞれの書き込み電圧を取得する工程と、すべての組における前記複数のワード線のうちの第1のワード線に対応するページの書き込み電圧の第1の平均値を演算する工程と、すべての組における前記複数のワード線のうちの、前記第1のワード線と隣り合う第2のワード線に対応するページの書き込み電圧の第2の平均値を演算する工程と、各組の第1のワード線に対応するページに対する書き込み電圧を前記第1の平均値に設定し、各組の第2のワード線に対応するページに対する書き込み電圧を前記第2の平均値に設定する工程と、を備えた。

(もっと読む)

固集積フラッシュメモリーセルストリング、セル素子、及びこの製造方法

【課題】優れた縮小化特性を有し、閾値電圧の散布を減らすことができるフラッシュメモリーセルストリング及びこの製造方法を提供する。

【解決手段】本発明は、フラッシュメモリーセルストリング及びこの製造方法に関する。前記フラッシュメモリーセルストリングは、多数のセル素子及び前記セル素子の端部に連結されるスイッチング素子を含む。前記セル素子は、半導体基板と、半導体基板に順次に積層される透過絶縁膜と、電荷貯蔵ノードと、コントロール絶縁膜と、制御電極とを備え、ソース/ドレーンが形成されないことを特徴とする。前記スイッチング素子は、セル素子に連結される側にソースまたはドレーンを含まないし、セル素子に連結されない側にソースまたはドレーンを含むが制御電極と重なり、又はまたは重ならないことを特徴とする。

(もっと読む)

半導体記憶装置

【課題】単位面積あたりのメモリモジュールの記憶容量を増加させる。また、消費電力の小さなメモリモジュールを提供する。

【解決手段】半導体装置は、ビット線と、二以上のワード線と、トランジスタおよびキャパシタからなるサブメモリセルを二以上有するメモリセルと、を有する。トランジスタのソースまたはドレインの一方がビット線と接続し、トランジスタのソースまたはドレインの他方がキャパシタと接続し、トランジスタのゲートがワード線の一と接続し、キャパシタの容量が各サブメモリセルで異なる。

(もっと読む)

半導体装置

【課題】FETの駆動力性能や遮断性能などを向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に形成され、オフ状態とオン状態とで閾値電圧を可変させるFETからなる半導体素子と、を備える。前記半導体素子は、前記半導体基板のチャネル形成箇所の上方に形成される絶縁膜と、前記絶縁膜の上方に配置されるゲート電極と、前記絶縁膜と前記ゲート電極との間に介挿され、前記チャネルとの間よりも、前記ゲート電極との間で、より多くの電子の授受を行なうチャージトラップ膜と、を有する。

(もっと読む)

半導体装置

【課題】所望のタイミングでデータの評価、書き換えを行うことができる半導体装置を提供する。

【解決手段】フリップフロップ回路と、選択回路と、選択回路を介して前記フリップフロップ回路と電気的に接続する不揮発性記憶回路と、を含むレジスタ回路と、ビット線と、データ線と、を有し、データ線はフリップフロップ回路と電気的に接続し、ビット線は、選択回路を介して不揮発性記憶回路と電気的に接続し、選択回路は、データ線の電位またはビット線の電位に応じたデータを選択的に不揮発性記憶回路に格納する半導体装置。

(もっと読む)

101 - 120 / 1,945

[ Back to top ]