Fターム[5F083JA04]の内容

半導体メモリ (164,393) | 材料 (39,186) | キャパシタ絶縁膜材料、ゲート絶縁膜材料 (10,102) | 酸化物系 (9,104) | 酸化膜を含む複合膜 (2,564) | シリコン酸化膜とシリコン窒化膜による複合膜 (1,945)

Fターム[5F083JA04]に分類される特許

61 - 80 / 1,945

半導体装置およびその製造方法

【課題】メモリセル特性の向上、およびトランジスタ特性の劣化の抑制を図る。

【解決手段】半導体層10上に、第1絶縁膜11を形成する。第1領域における第1絶縁膜上に、表面に酸化膜15が形成された第1導電膜18を形成する。第1領域における第1導電膜上および第2領域における第1絶縁膜上に、第2導電膜19を形成する。第2導電膜上に、第2絶縁膜21を形成する。第2絶縁膜上に、第3導電膜25を形成する。第1領域における第3導電膜および第2絶縁膜の一部を貫通させて第2導電膜を露出させる。第2導電膜および第3導電膜の表面に形成された第1自然酸化膜23を除去する。第3導電膜上および第1領域における第2導電膜上に、第4導電膜27を形成する。第4導電膜上に金属層30a,30bを形成して、第4導電膜、第3導電膜、および第1領域における第2導電膜をシリサイド化する。

(もっと読む)

半導体メモリ及びその製造方法

【課題】素子分離絶縁膜の応力に起因する素子特性の劣化を低減する。

【解決手段】本実施形態の半導体メモリは、第1のゲート絶縁膜上の電荷蓄積層と電荷蓄積層上に積層される制御ゲート電極とを含む第1のアクティブ領域AA内のメモリセルMCと、第2のゲート絶縁膜20L上の第1の電極層21Lと、を含む、第2のアクティブ領域AAL内の第1のトランジスタLTとを具備する。第2のアクティブ領域AALを定義する第2の素子分離絶縁膜19Xは、第1の膜190と、第1の膜190と第2のアクティブ領域AALとの間の第2の膜195とを含み、第1の膜190の上面は、第2の膜195の上面よりも、半導体基板10の底部側に位置している。

(もっと読む)

半導体メモリ

【課題】素子間リークを低減できる半導体メモリを提供する。

【解決手段】本実施形態の半導体装置は、第1のゲート絶縁膜上の電荷蓄積層と、第1の絶縁体を介して電荷蓄積層上に設けられる制御ゲート電極とを含むメモリセルと、アクティブ領域AAH上の第2のゲート絶縁膜20Hと、第2のゲート絶縁膜上の第1の電極層21Hと、を含むトランジスタHTと、素子分離絶縁膜15H上に設けられるシールドゲート電極SIGと、を有する。シールドゲート電極SIGの底部は、素子分離絶縁膜15Hの最も高い上面より半導体基板10の底部側に位置している。

(もっと読む)

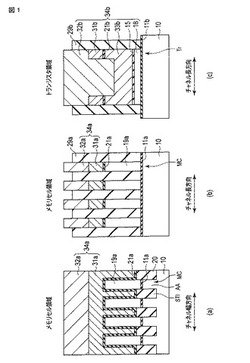

不揮発性半導体記憶装置

【課題】 不揮発性半導体記憶装置の書き込み特性を向上させることができる。また、不揮発性半導体記憶装置の隣接素子間の干渉を抑制することができる。

【解決手段】本発明の不揮発性半導体記憶装置は、半導体基板と、前記半導体基板の表面内に、チャネル領域を挟んで互いに離間して設けられたソース領域及びドレイン領域と、前記チャネル領域上に設けられたトンネル絶縁膜と、前記トンネル絶縁膜上に設けられた絶縁性電荷蓄積層と、前記絶縁性電荷蓄積層上に設けられた両側部に絶縁層が設けられた導電性電荷蓄積層と、前記導電性電荷蓄積層上に設けられた層間絶縁膜と、前記層間絶縁膜上に設けられた制御ゲートとを備えている。

(もっと読む)

半導体装置

【課題】電荷トラップを含むゲート電極と、電荷トラップを含まないゲート電極とを有する半導体装置において、両ゲート電極下のチャネル層にポテンシャルバリアが形成されないようにする。

【解決手段】基体8上に絶縁膜を介して第一のゲート電極1、第二のゲート電極2が形成され、両ゲート電極1、2を挟んで第一の拡散層5と第二の拡散層6が形成され、両拡散層5、6の間にチャネル層が形成されている。前記絶縁膜は、第一の拡散層5から第二の拡散層6の方向に第一の絶縁領域3、第二の絶縁領域4が配設された、両絶縁領域3、4のうち第二の絶縁領域4が電荷トラップを含み、第一の絶縁領域3を介して第一のゲート電極1が、第二の絶縁領域4を介して第二のゲート電極2が形成され、両ゲート電極1、2底部下に形成されるチャネル層の高さが相互に異なり、第二の拡散層6の先端部は、第二のゲート電極2直下の領域にまで到達している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離絶縁膜の形成時に、浮遊ゲート電極膜の基板に対面する部分の幅寸法が細くなってしまうことを防止する。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成され、浮遊ゲート電極膜、電極間絶縁膜および制御ゲート電極膜が積層されたゲート電極とを備えた。そして、前記浮遊ゲート電極膜を、窒素を含む下層シリコン層と窒素を実質的に含まない上層シリコン層とを有する多結晶シリコン層で構成し、前記下層シリコン層のゲート幅方向の寸法を、前記上層シリコン層のゲート幅方向の寸法よりも大きく構成した。

(もっと読む)

不揮発性半導体装置およびその製造方法

【課題】絶縁体に電荷を蓄える不揮発性メモリにおいて、データ保持特性を向上させることのできる技術を提供する。

【解決手段】メモリゲート電極MGと半導体基板1との間に介在する電荷蓄積層CSLをメモリゲート電極MGのゲート長または絶縁膜6t,6bの長さよりも短く形成して、電荷蓄積層CSLとソース領域Srmとのオーバーラップ量(Lono)を40nm未満とする。これにより、書込み状態では、書き換えを繰り返すことによって生じるソース領域Srm上の電荷蓄積層CSLに蓄積される正孔が少なくなり、電荷蓄積層CSL中に局在する電子と正孔との横方向の移動が少なくなるので、高温保持した場合のしきい値電圧の変動を小さくすることができる。また、実効チャネル長を30nm以下にすると、しきい値電圧を決定する見かけ上の正孔が少なくなり、電荷蓄積層CSL中での電子と正孔との結合が少なくなるので、室温保持した場合のしきい値電圧の変動を小さくすることができる。

(もっと読む)

半導体記憶装置の製造方法

【課題】スループットの向上を図る。

【解決手段】半導体記憶装置の製造方法は、基板上に、不純物濃度が第1濃度である第1シリコン層35、不純物濃度が第1濃度より低い第2濃度である第1犠牲層、不純物濃度が第1濃度である第2シリコン層35、および不純物濃度が第2濃度である第2犠牲層が順に積層された積層体を形成する工程と、積層体上に、第1絶縁膜を形成する工程と、積層体および第1絶縁膜内に、溝22を形成する工程と、溝内に、不純物濃度が第1濃度より低く、第2濃度より高い第3濃度である第3犠牲層90を埋め込む工程と、ウェットエッチングにより、溝内の第3犠牲層を上面から後退させて除去することで、第1犠牲層および第2犠牲層の端面を後退させる工程と、第1シリコン層および第2シリコン層の端面を第1犠牲層および第2犠牲層の端面に沿ってエッチングする工程とを具備する。

(もっと読む)

不揮発性半導体記憶装置

【課題】円筒型MONOSメモリセルで電荷保持特性の向上を図る。

【解決手段】不揮発性半導体記憶装置は、半導体基板と、前記半導体基板上に形成され、上面から下面まで達する円筒状の貫通ホールを有するコントロールゲートCGと、前記貫通ホール内における前記コントロールゲートの側面上に形成されたブロック絶縁膜150と、前記貫通ホール内における前記ブロック絶縁膜の側面上に形成された電荷蓄積膜151と、前記貫通ホール内における前記電荷蓄積膜の側面上に形成されたトンネル絶縁膜152と、前記貫通ホール内における前記トンネル絶縁膜の側面上に形成された半導体層SPと、を具備し、前記トンネル絶縁膜は、SiO2を母材とし、添加することで前記母材のバンドギャップを低下させる元素を含む第1絶縁膜を含み、前記元素の濃度および濃度勾配は、前記半導体層側から前記電荷蓄積膜側に向かって単調に増加する。

(もっと読む)

半導体記憶装置

【課題】十分な消去速度が得られる半導体記憶装置を提供することである。

【解決手段】実施形態に係る半導体記憶装置は、基板と、前記基板上にそれぞれ交互に積層された複数の電極層と複数の第1の絶縁層とを有する第1の積層体と、前記第1の積層体上に設けられ、選択ゲートとその上に設けられた第2の絶縁層とを有する第2の積層体と、前記第1の積層体を積層方向に貫通して形成された第1のホールの側壁に設けられたメモリ膜と、前記第1のホールと連通し、前記第2の積層体を積層方向に貫通して形成された第2のホールの側壁に設けられたゲート絶縁膜と、前記メモリ膜の内側および前記ゲート絶縁膜の内側に設けられたチャネルボディと、を備えている。そして、前記選択ゲートの側面と前記第2の絶縁層との間に段差部が形成され、前記チャネルボディの前記選択ゲートの上端近傍に位置する領域は、シリサイド化されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】小型化が可能な不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、基板と、メモリ部と、非メモリ部と、を備える。メモリ部は、基板上に設けられる。非メモリ部は、基板上に設けられ基板の主面に対して平行な面内でメモリ部と並ぶ。メモリ部は、積層体と、半導体層と、メモリ膜と、導電膜と、を含む。積層体は、主面に対して垂直な第1軸に沿って積層された複数の電極膜と、第1軸に沿って隣り合う2つの電極膜の間に設けられた電極間絶縁膜と、を含む。半導体層は、複数の電極膜の側面に対向する。メモリ膜は、複数の電極膜と半導体層との間に設けられる。導電膜は、積層体の上に設けられ、積層体と離間している。非メモリ部は、導電膜と同層の抵抗素子部を含む。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を歩留まり良く製造する技術を提供する。

【解決手段】基板上に設けられ、一対の不純物領域の間に設けられたチャネル形成領域を

含む島状の半導体層と、半導体層の側面に接して設けられた第1絶縁層と、チャネル形成

領域上に設けられ、半導体層を横断するように設けられたゲート電極と、チャネル形成領

域及びゲート電極の間に設けられた第2絶縁層と、半導体層及び前記ゲート電極上に形成

された第3絶縁層と、第3絶縁層を介して、不純物領域と電気的に接続される導電層と、

を有する。不純物領域はチャネル形成領域と比較して膜厚が大きい領域を有し、且つ該膜

厚が大きい領域で導電層が接続されている。第2絶縁層は、少なくともゲート電極が重畳

する領域の半導体層の側面に設けられた第1絶縁層を覆う。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】選択ゲートの閾値電圧の変動が抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、交互に積層された複数の電極層と複数の第1絶縁層とを有する第1積層体と、第1積層体を貫通する第1ホールの側壁に設けられたメモリ膜と、第1ホール内に設けられたメモリ膜の内側に設けられた第1チャネルボディ層と、第1積層体の上に設けられた層間絶縁膜と、層間絶縁膜の上に設けられた選択ゲート電極層と、選択ゲート電極層の上に設けられた第2絶縁層と、を有する第2の積層体と、第1ホールに連通し第2積層体および層間絶縁膜を貫通する第2ホールの側壁に設けられたゲート絶縁膜と、第2ホール内におけるゲート絶縁膜の内側に設けられ、第1チャネルボディ層とつながった第2チャネルボディ層と、を備える。選択ゲート電極層と第2絶縁層との界面における第2ホールの径は選択ゲート電極層と層間絶縁膜との界面における第2ホールの径よりも小さい。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの制御性を向上した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、構造体と、複数の半導体層と、メモリ膜と、接続部材と、導電部材と、を備える。前記構造体は、メモリ領域と非メモリ領域とを有する基板の前記メモリ領域の上に設けられる。前記構造体は、前記基板の主面に対して垂直な第1軸に沿って積層され複数の電極膜を含む。前記半導体層は、前記構造体を前記第1軸に沿って貫通する。前記メモリ膜は、前記複数の電極膜と前記半導体層との間に設けられる。前記接続部材は、前記基板と前記半導体層との間に設けられる。前記接続部材は、隣り合う2つの前記半導体層のそれぞれの端部と接続される。前記導電部材は、前記基板と前記接続部材との間で、前記メモリ領域から前記非メモリ領域に延在して設けられる。前記導電部材は、前記非メモリ領域の上に設けられた凹部を有する。前記凹部内には、第1シリサイド部が設けられる。

(もっと読む)

半導体装置およびその製造方法

【課題】 所望の深さを有し幅の狭い凹部を半導体基板に安定して形成することが可能な製造方法を提供すること。

【解決手段】 本発明は、半導体基板10の一部に酸素イオン注入を行うことで第1酸素含有領域24を形成する工程と、半導体基板10に熱処理を行い、第1酸素含有領域24に含まれる酸素を用いて第1酸素含有領域24を酸化させることで、第1酸素含有領域24を第1酸化領域26とする工程と、第1酸化領域26を除去することで半導体基板10に凹部16を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

半導体装置の製造方法

【課題】同一セル内に複数設けられたビットへの個々への書き込み動作が他ビットへの書き込み量に依存することなく正常に行われ、さらには、書き込み・読み出し特性を損なうことなくSONOS構造セルのいっそうの微細化を可能とする半導体装置およびその製造方法を提供する。

【解決手段】本発明による半導体装置は、一対の第1拡散領域を有する基板と、該基板上に形成された酸化膜および該酸化膜上に形成された電荷蓄積層とを有するゲート部とを有し、前記電荷蓄積層は当該電荷蓄積層中に離隔して位置する複数のビット領域を有する電気的絶縁膜である。また、酸化膜は、ビット領域に対応する部分がトンネル酸化膜として作用する膜厚の薄膜部およびビット領域間に位置する部分がトンネル効果による電荷輸送を抑制する膜厚の厚膜部を有している。

(もっと読む)

半導体素子及びその製造方法

【課題】フラッシュメモリ素子の安全性及び信頼性を改善することができる半導体素子及びその製造方法を提供する。

【解決手段】第1方向に沿って延長された活性領域を含む半導体基板と、半導体基板の上部に第1方向に交差する第2方向に沿って形成されたセレクトラインと、セレクトラインの間の前記活性領域それぞれに形成されて第1不純物を含む接合領域と、セレクトラインの間の空間を埋め込む多層の酸化膜と、接合領域の下部に繋がれて半導体基板の活性領域に形成されて第2不純物を含む接合領域延長部と、多層の酸化膜のうち少なくともいずれか一層を貫通して接合領域及び接合領域延長部に接触されたコンタクトプラグと、を含む。

(もっと読む)

半導体装置

【課題】不揮発性を有し、書き込み回数に制限のない新たな構造の半導体装置を提供する。

【解決手段】複数の記憶素子が直列に接続され、複数の記憶素子の一は、第1〜第3のゲート電極、第1〜第3のソース電極、および第1〜第3のドレイン電極を有する第1〜第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含んで構成され、第1のゲート電極と、第2のソース電極または第2のドレイン電極の一方とは、電気的に接続され、第1の配線と、第1のソース電極と、第3のソース電極とは、電気的に接続され、第2の配線と、第1のドレイン電極と、第3のドレイン電極とは、電気的に接続され、第3の配線と、第2のソース電極または第2のドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のゲート電極とは、電気的に接続され、第5の配線と、第3のゲート電極とは電気的に接続された半導体装置。

(もっと読む)

半導体装置

【課題】高速動作が可能であり、且つ消費電力の低減が可能な半導体装置を提供する。

【解決手段】酸化物半導体を有するトランジスタを備える半導体装置において、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜において、酸素濃度が異なる。代表的には、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と比較して、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜の酸素濃度が低い。

(もっと読む)

61 - 80 / 1,945

[ Back to top ]