Fターム[5F083JA04]の内容

半導体メモリ (164,393) | 材料 (39,186) | キャパシタ絶縁膜材料、ゲート絶縁膜材料 (10,102) | 酸化物系 (9,104) | 酸化膜を含む複合膜 (2,564) | シリコン酸化膜とシリコン窒化膜による複合膜 (1,945)

Fターム[5F083JA04]に分類される特許

81 - 100 / 1,945

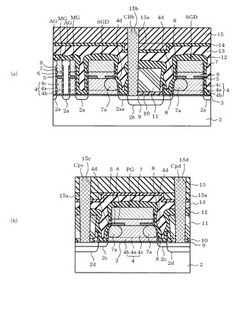

不揮発性半導体記憶装置およびその製造方法

【課題】選択ゲートトランジスタや周辺回路部のトランジスタの下部電極の抵抗値を低減し、しきい値電圧の増加も図れるようにする。

【解決手段】ゲート電極の加工時に、選択ゲートトランジスタのゲート電極SGD−SGD間の側壁部と、周辺回路部のトランジスタのゲート電極PGの両側壁とに、多結晶シリコン膜4の上部に段差形状を形成し、傾斜部4dを設ける。ゲート電極の多結晶シリコン膜6のシリサイド加工時に、多結晶シリコン膜4の傾斜部4dからもシリサイド化を進行させ、シリサイド膜7および7aを形成する。これにより、ゲート電極SGDおよびPGの下部電極においても低抵抗化を図ることができる。多結晶シリコン膜4に分断層4aを設けることで、シリサイド反応を停止させたり、設けないでゲート絶縁膜3の部分までシリサイド反応させてしきい値電圧を増加させたりできる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】シリサイド工程によるゲート絶縁膜の金属汚染や、メモリセルのショートチャネル効果を抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、半導体基板と、前記半導体基板上に順に形成された第1絶縁層、電荷蓄積層、第2絶縁層、および制御電極を有し、前記電荷蓄積層の側面が傾斜面を有する複数のメモリセルトランジスタとを備える。さらに、前記装置は、前記メモリセルトランジスタの側面と、前記メモリセルトランジスタ間の前記半導体基板の上面に形成された第1の絶縁膜部分と、前記メモリセルトランジスタ間のエアギャップ上と前記メモリセルトランジスタ上に連続して形成された第2の絶縁膜部分と、を有する1層以上の絶縁膜を備える。さらに、前記メモリセルトランジスタ間の前記半導体基板の上面から前記エアギャップの下端までの第1距離は、前記メモリセルトランジスタの側面に形成された前記絶縁膜の膜厚よりも大きい。

(もっと読む)

三次元集積回路を作製する方法

【課題】集積回路を作製する新規なタイプの方法を提供する。

【解決手段】少なくとも第3の層がその間に配置された、少なくとも半導体の第1および第2の層を備える基板を作製するステップと、少なくとも第1のMOSデバイスを作製するステップであって、その活性領域が半導体の第1の層の少なくとも一部に形成される、ステップと、少なくとも第2のMOSデバイスを作製するステップであって、その活性領域が半導体の第2の層の少なくとも一部に形成され、第2のMOSデバイスの活性領域が第2のMOSデバイスのゲートと第1のMOSデバイスの活性領域との間に配置される、ステップとを少なくとも含む、集積電子回路を作製する方法。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】メモリセルトランジスタのゲート電極間の空隙の形状を最適化し、高性能、高信頼性を実現する不揮発性半導体記憶装置の製造方法。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板上に、第1のゲート絶縁膜、第1のフローティングゲート電極、第1のゲート間絶縁膜、第1のコントロールゲート電極、第1のゲートマスク絶縁膜の積層構造を有する複数のメモリセルゲート電極を形成する。メモリセルゲート電極の側壁部に保護膜を形成し、その一部を第1のコントロールゲート電極の側壁部の一部が露出するよう除去する。金属膜を形成し、熱処理により、金属膜と第1のコントロールゲート電極を反応させ第1の金属半導体化合物層を形成する。メモリセルゲート電極間を埋め込み、内部に空隙を有する層間絶縁膜であって、第1のコントロールゲート電極の上面よりも半導体基板から離れた位置に空隙の上端が位置する層間絶縁膜を形成する。

(もっと読む)

不揮発性半導体記憶装置とその製造方法

【課題】書き込み特性を向上することが可能な不揮発性半導体記憶装置とその製造方法を提供する。

【解決手段】複数のゲート電極構造13は、半導体基板11上に形成されたゲート絶縁膜12、電荷蓄積層14、ゲート間絶縁膜15、第1制御ゲート16、及び前記第1制御ゲートより幅が広い第2制御ゲート電極17を有する。絶縁膜19は、制御ゲート電極17間及び制御ゲート電極より上方に形成された空隙19を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】高い信頼性を有し且つ安価な不揮発性半導体記憶装置を提供する。

【解決手段】この不揮発性半導体記憶装置において、メモリストリングスは、基板に対して垂直方向に延びる一対の柱状部、及び前記一対の柱状部の下部を連結させるように形成された連結部を有する半導体層と、前記柱状部の側面を取り囲むように形成された電荷蓄積層と、前記柱状部の側面及び前記電荷蓄積層を含む第1の絶縁膜と、前記柱状部の側面及び前記第1の絶縁膜を覆うように形成された第1導電層と、前記連結部の周囲に形成される第2の絶縁膜と、前記連結部に前記ゲート絶縁膜を介して形成される第2導電層とを備える。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてエネルギーギャップの異なる少なくとも2層の酸化物半導体層を含み、かつ積層された酸化物半導体層の間に混合領域を有する酸化物半導体積層を用いる。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】重畳する第1のトランジスタおよび第2のトランジスタからなる第1のインバータと、重畳する第3のトランジスタおよび第4のトランジスタからなる第2のインバータと、第1の選択トランジスタと、第2の選択トランジスタと、を有し、第1のインバータの出力端子、第2のインバータの入力端子および第1の選択トランジスタのソースおよびドレインの一方が接続され、第2のインバータの出力端子、第1のインバータの入力端子および第2の選択トランジスタのソースおよびドレインの一方が接続されることによって、微細化したSRAM回路を形成する。

(もっと読む)

導電性側壁スペーサを有する不揮発性メモリ装置及びその製造方法

【課題】従来の窒化膜側壁を電荷トラップ媒体に利用する場合の信頼性劣化を改善した不揮発性メモリ装置を提供する。

【解決手段】半導体基板21上のゲート絶縁膜22Aと、該ゲート絶縁膜上に順に積層して形成された第1電極膜23、第2電極膜24、及びハードマスク膜25を有するゲート100と、該ゲートの第1電極膜23及び第2電極膜24の両側壁に形成された一対の再酸化側壁スペーサ27と、該再酸化側壁スペーサ及びゲート100のハードマスク膜25の両側壁上に形成された一対の側壁スペーサ28Aと、一対の側壁スペーサ28A上に形成された、電荷を捕獲及び放出する一対の導電性側壁スペーサ29Bと、半導体基板21内に形成された一対のLDD領域26と、半導体基板21内に形成されたソース/ドレイン領域30とを備え、導電性側壁スペーサ29Bが、ゲート100及び側壁スペーサ28Aよりも低い高さを有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】高速で動作し得る不揮発性半導体記憶装置を提供する。

【解決手段】選択トランジスタとメモリセルトランジスタMTとを有するメモリセルMCがマトリクス状に配列されて成るメモリセルアレイ10と、ビット線BLの電位を制御する列デコーダ12と、第1のワード線WL1の電位を制御する電圧印加回路14と、第2のワード線WL2の電位を制御する第1の行デコーダ16と、ソース線SLの電位を制御する第2の行デコーダ18とを有し、列デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されており、第1の行デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されている。ビット線と第2のワード線とが高速で制御され得るため、メモリセルトランジスタに書き込まれた情報を高速で読み出すことができる。

(もっと読む)

半導体装置

【課題】トランジスタのしきい値電圧のばらつきの影響を緩和し、複数の状態(例えば3以上の状態)の区別を正確、かつ容易にした半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、ワード線と、ビット線とワード線に接続されたメモリセルと、入力されたアドレス信号によって指定されたメモリセルを選択するように、複数の第2信号線及び複数のワード線を駆動する、第2信号線およびワード線の駆動回路と、書き込み電位を第1信号線に出力する、書き込み回路と、指定されたメモリセルに接続されたビット線から入力されるビット線の電位と、複数の読み出し電位とを比較する読み出し回路と、ビット線の電位と複数の読み出し電位の比較結果に基づいて複数の補正電圧のいずれかを選択する制御回路と、書き込み電位及び複数の読み出し電位を生成して、書き込み回路及び読み出し回路に供給する、電位生成回路と、を有する半導体装置。

(もっと読む)

不揮発性半導体記憶装置

【課題】ビット線接続部の微細化を実現する不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、p型の半導体基板101と、半導体基板101内に形成され、メモリセルのビット線とセンスアンプ部を接続するビット線接続トランジスタHTkが形成されるp型の第1のPウェル102と、第1のPウェル102を囲み、第1のPウェル102を半導体基板101から電気的に分離するn型の第1のNウェル103と、を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】正確に書き込み動作を行うことができる不揮発性半導体記憶装置を提供する。

【解決手段】

複数の素子分離絶縁膜は、半導体層中に形成され、第1方向を長手方向とする。複数の素子形成領域は、素子分離絶縁膜により分離して形成される。素子形成領域にはメモリストリングが形成される。複数の素子形成領域群が素子形成領域により構成される。メモリセルアレイは、第1方向と直交する第2方向において、前記素子形成領域群の間隔が前記素子形成領域群の中の前記素子形成領域の間隔より大きくされている。制御回路は、前記メモリセルアレイに対する書き込み動作を、前記素子形成領域群ごとに実行する。

(もっと読む)

半導体装置の製造方法

【課題】ラインスペースパターンと幅の広いパターンが混在する場合であっても、両パターンを精度よく加工する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、被加工層上にハードマスク層を形成する。その上に第1のマスク層を形成し、第1のマスク層をパターニングする。第1のマスク層が除去された領域にカーボン層を形成しパターニングする。カーボン層を部分的にエッチングし、カーボン層のパターン幅を縮小する。第1のマスク層と同一材料の第2のマスク層を形成し、エッチングによりカーボン層のパターンの両側面に第2のマスク層を残存させる。第2のマスク層のパターンに挟まれるカーボン層を除去する。第1および第2のマスク層のパターンをマスクにハードマスク層をパターニングする。第1および第2のマスク層のパターンを除去する。ハードマスク層のパターンをマスクに被加工層をパターニングする。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択ゲートトランジスタのゲート電極間の間隔の縮小を実現する不揮発性半導体記憶装置を提供する。

【解決手段】実施の形態の不揮発性半導体記憶装置は、半導体基板と、第1の方向に伸長する複数の第1の素子領域と、第1の素子領域を互いに分離する第1の素子分離領域と、第1の方向に伸長する複数の第2の素子領域と、第2の素子領域を互いに分離する第2の素子分離領域と、第1の素子領域と第2の素子領域との間に設けられ、第1および第2の素子領域に接続され、第1の方向と直交する第2の方向に伸長する第3の素子領域と、第1および第3の素子領域上にまたがり、第2の方向に伸長する第1の選択ゲート電極と、第2および第3の素子領域上にまたがり、第1の選択ゲート電極に隣接して平行に配置される第2の選択ゲート電極と、第1および第2の選択ゲート電極間の第3の素子領域に接続されるコンタクト電極を有する。

(もっと読む)

半導体装置の製造方法

【課題】金属酸化膜の表面に形成される導電膜の基板面内における厚さばらつきを低減して、半導体装置の歩留まりを向上させることが可能であり、かつ導電膜の成長速度を向上させて、半導体装置の生産性を向上させることの可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に、金属酸化膜を含む誘電体膜5を形成する工程と、誘電体膜5において、表面5aに非晶質の金属酸化膜が露出した状態で、誘電体膜5の表面5aに導電膜6を形成する工程と、を含む。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高集積化に適した不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第3のフィン型積層構造Fin1〜Fin3を有する。第1乃至第3のフィン型積層構造Fin1〜Fin3は、第1の方向に積み重ねられる第1及び第2の半導体層Sm1,Sm2を備える。第1及び第2のアシストゲート電極AG1,AG2は、第3の方向に並んで配置され、第3のフィン型積層構造Fin3の第1の方向にある表面上で互いに分断される。第1のアシストゲートトランジスタAGT1は、第1及び第3のフィン型積層構造Fin1,Fin3内に形成され、第2のアシストゲートトランジスタAGT2は、第2及び第3のフィン型積層構造Fin2,Fin3内に形成される。

(もっと読む)

半導体記憶装置

【課題】 ビット線選択回路の小型化を図るとともにビット線の駆動時間を高速に行うことができる半導体記憶装置を提供する。

【解決手段】 フラッシュメモリ10は、セルユニットNUが行列状に複数配置されたメモリアレイ100と、セルユニットNUに接続されたビット線を選択するビット線選択回路200とを有する。ビット線選択回路200は、偶数ビット線GBL_e、奇数ビット線GBL_oをセンス回路に選択的に接続するための選択トランジスタSEL_e、SEL_o、BLSを含む第1の選択部210と、偶数ビット線GBL_eおよび奇数ビット線GBL_oに選択的にバイアス電圧を印加するためのバイアストランジスタYSEL_e、YSEL_oとを含む第2の選択部220とを有する。第2の選択部220のバイアストランジスタYSEL_e、YSEL_oは、記憶素子と共通のウエル内に形成される。

(もっと読む)

半導体装置の作製方法

【課題】トランジスタの微細化を達成し、電界緩和がなされた、酸化物半導体を用いた半導体装置を提供することを課題の一とする。

【解決手段】ゲート電極の線幅を微細化し、ソース電極層とドレイン電極層の間隔を短縮する。ゲート電極をマスクとして自己整合的に希ガスを添加し、チャネル形成領域に接する低抵抗領域を酸化物半導体層に設けることができるため、ゲート電極の幅、即ちゲート配線の線幅を小さく加工しても位置精度よく低抵抗領域を設けることができ、トランジスタの微細化を実現できる。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ微細化を達成した半導体装置の提供と、さらに、これらの微細化を達成した半導体装置の良好な特性を維持しつつ、3次元高集積化を図る。

【解決手段】絶縁層中に埋め込まれた配線と、絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極及びドレイン電極と、酸化物半導体層と重畳して設けられたゲート電極と、酸化物半導体層と、ゲート電極との間に設けられたゲート絶縁層と、を有し、絶縁層は、配線の上面の一部を露出するように形成され、配線は、その上面の一部が絶縁層の表面の一部より高い位置に存在し、且つ、絶縁層から露出した領域において、ソース電極またはドレイン電極と電気的に接続し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さが1nm以下である半導体装置である。

(もっと読む)

81 - 100 / 1,945

[ Back to top ]