Fターム[5F083JA37]の内容

半導体メモリ (164,393) | 材料 (39,186) | 電極材料、配線材料、バリア材料 (24,756) | Cu、Cu系合金 (2,136)

Fターム[5F083JA37]に分類される特許

141 - 160 / 2,136

半導体装置

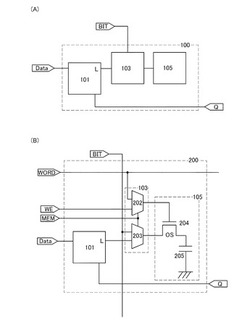

【課題】所望のタイミングでデータの評価、書き換えを行うことができる半導体装置を提供する。

【解決手段】フリップフロップ回路と、選択回路と、選択回路を介して前記フリップフロップ回路と電気的に接続する不揮発性記憶回路と、を含むレジスタ回路と、ビット線と、データ線と、を有し、データ線はフリップフロップ回路と電気的に接続し、ビット線は、選択回路を介して不揮発性記憶回路と電気的に接続し、選択回路は、データ線の電位またはビット線の電位に応じたデータを選択的に不揮発性記憶回路に格納する半導体装置。

(もっと読む)

記憶回路、信号処理回路、電子機器

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】酸化物半導体を用いて形成されたトランジスタと、該トランジスタのソース電極またはドレイン電極の一方と接続された容量素子を用いて、不揮発性の記憶回路を構成する。記憶回路に予めハイレベル電位を書き込んでおき、退避させるデータがハイレベル電位の場合は、そのままの状態を維持し、退避させるデータがローレベル電位の場合は、ローレベル電位を記憶回路に書き込むことで、書き込み速度を向上させた信号処理回路を実現できる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

記憶回路

【課題】短時間の電源停止により消費電力を抑えることができ、電源再開時において誤動作を引き起こすことなく初期化することのできる信号処理装置の記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性記憶部に記憶していたデータ信号を、不揮発性記憶部に保持する。不揮発性記憶部では、オフ電流が極めて小さいトランジスタを用いることによって、容量素子に保持されたデータ信号は長期間にわたり保持する。こうして、不揮発性記憶部は電源の供給が停止した間も論理状態を保持する。また電源停止時に容量素子で保持されたデータ信号は、電源再開時にはリセット回路を導通状態とすることで、誤動作を引き起こすことのない電位にする。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の占有面積を実質的に減少させる。

【解決手段】半導体装置は、第1の方向及びそれと交差する第2の方向に沿って半導体基板上に配列形成された複数の第1の接続領域と、複数の第1の接続領域を第1の方向に沿った列ごとに電気的に接続する複数の配線とを含む。複数の配線は、第2の方向に隣り合う2つの配線が互いに異なる配線層に配置され、かつ平面視において一部が重なってハニカム状に見えるように屈曲させてある。

(もっと読む)

半導体装置

【課題】酸化物半導体層を含むトランジスタを有する不揮発性メモリにおいて、保持された情報を容易に消去できる不揮発性メモリを提供する。

【解決手段】第1のトランジスタ及び第2のトランジスタを有するメモリセルを有し、第1のトランジスタは第1のチャネル、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有し、第2のトランジスタは酸化物半導体からなる第2のチャネル、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有し、第2のソース電極及び第2のドレイン電極の一方は第1のゲート電極と電気的に接続され、メモリセルへの情報の書き込み及び消去は、第2のソース電極及び第2のドレイン電極の一方と、第1のゲート電極との間のノードの電位を高くすることにより情報が書き込まれ、第2のチャネルに紫外線を照射して、ノードの電位を低くすることにより情報が消去される不揮発性メモリによって解決する。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1乃至第4のノードを有する論理回路と、第1のノード、第2のノード、及び第3のノードと接続された第1の制御回路と、第1のノード、第2のノード、及び第4のノードと接続された第2の制御回路と、第1のノード、第1の制御回路、及び第2の制御回路に接続された第1の記憶回路と、第2のノード、第1の制御回路、及び第2の制御回路に接続された第2の記憶回路と、を有する記憶装置である。

(もっと読む)

半導体装置およびその作製方法

【課題】同一基板上に酸化物半導体を用いたオフセットトランジスタとオフセットでないトランジスタを形成する。

【解決手段】酸化物半導体層202とゲート絶縁物203とゲート配線となる第1層配線204a、第1層配線204bを形成する。その後、オフセットトランジスタをレジスト206で覆い、酸化物半導体層に不純物を導入し、N型酸化物半導体領域207を形成する。その後、第2層配線209a、第2層配線209b、第2層配線209cを形成する。以上の工程により、オフセットトランジスタとそうでないトランジスタ(アラインドトランジスタ等)を形成することができる。

(もっと読む)

記憶装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な記憶装置、及び該記憶装置を有する半導体装置を提供する。

【解決手段】第1の入力端子、及び第1の入力端子の入力信号の反転信号が入力される第2の入力端子、並びに第1の信号が出力される第1の出力端子、及び第1の信号の反転信号が出力される第2の出力端子、を有するレベルシフタと、第1の信号が入力される第3の入力端子、及び第1の信号の反転信号が入力される第4の入力端子、並びに第3の出力端子を有する第1のバッファと、第1の信号の反転信号が入力される第5の入力端子、及び第1の信号が入力される第6の入力端子、並びに第4の出力端子を有する第2のバッファと、を有し、第1のバッファの第3の出力端子から出力される信号が、レベルシフタの第1の入力端子に入力され、第2のバッファの第4の出力端子から出力される信号が、レベルシフタの第2の入力端子に入力される。

(もっと読む)

3次元ダブルクロスポイントアレイを有する半導体メモリ素子及びその製造方法

【課題】単純な方式で集積度が向上し電気的特性が改善された3次元ダブルクロスポイントアレイを有する半導体メモリ素子及びその製造方法を提供する。

【解決手段】本発明の半導体メモリ素子は、互いに異なるレベルに配置され、2つの交差点を定義する第1、第2、及び第3導線と、2つの交差点の各々に配置される2つのメモリセルを備え、第1及び第2導線は互いに平行に延長され、第3導線は延長されて第1及び第2導線と交差し、第1及び第2導線は垂直断面で見た時に第3導線の長さに沿って交互に配列され、第3導線は第1及び第2導線から垂直に離隔される。

(もっと読む)

不揮発性半導体記憶装置

【課題】大量データを高速に一括で保存することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】ビット線BL0〜BL3とワード線WL0〜WL3との間に接続され、低抵抗状態から高抵抗状態へ遷移するリセット動作と、リセット動作と異なる極性の電圧を印加することにより高抵抗状態から低抵抗状態へ遷移するセット動作が行われ、リセット動作時に流れるリセット電流がセット動作時に流れるセット電流よりも1桁以上低い可変抵抗素子VRを含むメモリセルMCを複数備えたメモリセルアレイを有する。さらに、メモリセルMCに対してリセット動作及びセット動作を行い、リセット動作を低抵抗状態である第1の複数のメモリセルのうち、選択の第1の配線に接続され、かつ選択の第2の配線に接続される第2の複数のメモリセルに対して一括して行う制御回路を有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造において基板の金属汚染を抑える。

【解決手段】半導体素子が設けられた基板の、半導体素子形成面とは反対側の裏面および端部に保護膜を形成する工程と、前記半導体素子形成面に設けられた金属含有膜を加工する工程と、前記金属含有膜の加工後に前記保護膜を除去する工程と、を含む半導体装置の製造方法。

(もっと読む)

抵抗変化型メモリデバイスおよびその動作方法

【課題】ビット線側での素子電流による高い制御性を維持しながらも、低抵抗化動作の高速化を実現する抵抗変化型メモリデバイスを提供する。

【解決手段】ビット線BLに接続されて第1電流I1を流す初期電流駆動部55(N4)と、ビット線BLに対し初期電流駆動部55と並列に接続されて、第2電流I2を制御する素子電流制御部52とを有する。そして、初期電流駆動部55と素子電流制御部52の各NMOSトランジスタN4,N3を差動制御して、BL電流の値をI1からI2に切り替える。

(もっと読む)

半導体素子、記憶回路、集積回路、及び集積回路の駆動方法

【課題】回路規模の拡大に資する新規の半導体素子を提供する。

【解決手段】独立した2つの電気的スイッチを単体の酸化物半導体層を用いて構成することを要旨とする。例えば、当該半導体素子は、当該酸化物半導体層の下面(第1の面)近傍におけるチャネル(電流経路)の形成と、上面(第2の面)近傍におけるチャネルの形成とを独立して制御する。これにより、2つの電気的スイッチを別個に設ける場合(例えば、2つのトランジスタを別個に設ける場合)と比較して、回路面積を縮小することが可能となる。すなわち、当該半導体素子を用いて回路を構成することで、回路規模の拡大に伴う回路面積の拡大を抑制することが可能になる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

信号処理装置

【課題】消費電力を抑えることができる信号処理装置を提供する。

【解決手段】信号処理装置が有する記憶回路に、酸化物半導体にチャネルが形成されるトランジスタを適用することで、電力の供給を停止している間もデータの保持(記憶)を可能とする。記憶回路に記憶されているデータは、信号処理装置への電力の供給を停止している間も、破壊すること無く読み出すことができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、配線数を削減することによって高集積化が図られた半導体装置を提供することを目的とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込み用のワード線と読み出し用のワード線を共通化し、かつ書き込み用のビット線と読み出し用のビット線を共通化することにより配線数を削減し、更にソース線を削減することにより単位面積あたりの記憶容量を増加させる。

(もっと読む)

記憶装置

【課題】電力が供給されない状況でも記憶内容の保持が可能であり、記憶素子を構成するトランジスタをオンすることなく、記憶したデータを高速で読み出すことができる記憶装置を提供する。

【解決手段】記憶装置において、酸化物半導体層をチャネル領域として有するトランジスタ及び保持容量素子を有するメモリセルと、容量素子と、を電気的に接続させてノードを構成し、該ノードは保持容量素子を介した容量結合により保持データに応じて昇圧され、この電位を増幅回路によって読み出すことで、データの識別を行うことができる。

(もっと読む)

半導体装置

【課題】瞬断もしくは瞬時電圧低下等の極めて短時間の電源停止又は電源電圧低下の場合でさえ、揮発性メモリ内のデータが消失してしまう場合があった。そこで、高速データ処理のために揮発性メモリを用いた場合であっても、データの保持時間を延ばす。

【解決手段】容量素子及び酸化物半導体を用いたトランジスタを有するメモリに揮発性メモリのデータ内容をバックアップしておくことによって、データの保持時間を長くすることができる。

(もっと読む)

半導体装置

【課題】連想メモリは一つのメモリセル内の素子数が多く、一つのメモリセルの面積が大きくなりやすい。そこで、一つのメモリセルの面積を小さくする。

【解決手段】読み出し用のトランジスタのチャネル容量(ゲート電極とチャネル形成領域との間の容量)を用いて電荷の保持を行う。つまり、読み出し用のトランジスタを電荷保持用のトランジスタとして兼用する。また、読み出し用且つ電荷保持用のトランジスタのゲートに電荷供給用のトランジスタのソース又はドレインの一方を電気的に接続する。

(もっと読む)

141 - 160 / 2,136

[ Back to top ]