Fターム[5F083JA42]の内容

半導体メモリ (164,393) | 材料 (39,186) | 電極材料、配線材料、バリア材料 (24,756) | 酸化物導電体 (2,345)

Fターム[5F083JA42]の下位に属するFターム

白金族元素酸化物(PtOx、RuOx) (1,066)

複酸化物 (752)

ドープにより導電性を有するもの (18)

Fターム[5F083JA42]に分類される特許

141 - 160 / 509

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、少なくとも酸化物半導体膜中に希ガスイオンを注入する注入工程を行い、減圧下、窒素雰囲気下、又は希ガス雰囲気下において、希ガスイオンを注入した酸化物半導体膜に加熱工程を行って希ガスイオンを注入した酸化物半導体膜中に含まれる水素若しくは水を放出させ、酸化物半導体膜を高純度化する。

(もっと読む)

半導体装置の製造方法、強誘電体素子の製造方法および電子機器の製造方法

【課題】液体プロセスに採用し易い配向性の制御が可能な半導体装置や強誘電体素子の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、ソース電極およびドレイン電極と、前記ソース電極及び前記ドレイン電極との間に配置され、チャネル部を有する有機半導体膜と、ゲート電極と、前記チャネル部と前記ゲート電極との間に配置されたゲート絶縁膜と、を有する半導体装置の製造方法であって、前記チャネル部を第1の温度に加熱する工程と、前記第1の温度の前記有機半導体膜に、前記第1の温度よりも低い第2の温度の絶縁性ポリマーを含む液滴材料を配置し一定の方向に延ばす塗工工程により前記ゲート絶縁膜を形成する工程と、を有することを特徴とする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置の提供。

【解決手段】酸化物半導体材料を用いたトランジスタ162と、酸化物半導体以外の半導体材料を用いたトランジスタ160を組み合わせて用いることにより、書き込み回数にも制限が無く、長期間にわたる情報の保持ができる、新たな構造の半導体装置を実現することができる。さらに、酸化物半導体以外の半導体材料を用いたトランジスタと酸化物半導体材料を用いたトランジスタとを接続する接続電極130bを、当該接続電極と接続する酸化物半導体以外の半導体材料を用いたトランジスタの電極129より小さくすることにより、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体装置及びその作製方法

【課題】しきい値電圧の制御が困難な酸化物半導体を活性層に用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】一対の第1の領域、一対の第2の領域及び第3の領域を有する酸化物半導体膜と、酸化物半導体膜と接して設けられる一対の電極と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜を介し、一対の電極の間に設けられたゲート電極と、を有し、一対の第1の領域は一対の電極と重畳し、第3の領域はゲート電極と重畳し、一対の第2の領域は一対の第1の領域及び第3の領域の間に形成され、一対の第2の領域及び第3の領域には窒素、リン、または砒素のいずれかの元素が含まれており、該元素の濃度は、第3の領域より一対の第2の領域のほうが高い構成とする。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気的特性の良好なトランジスタ及びその作製方法を提供することを課題の一とする。

【解決手段】基板上に酸化物半導体膜及び絶縁膜を有し、酸化物半導体膜の端部は絶縁膜と接しており、酸化物半導体膜は、チャネル形成領域と、チャネル形成領域を挟んで形成されたドーパントを含む領域とを含み、酸化物半導体膜上に接して形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、サイドウォール絶縁膜を有するゲート電極と、サイドウォール絶縁膜、酸化物半導体膜、および絶縁膜に接して形成されたソース電極およびドレイン電極とを有する半導体装置である。

(もっと読む)

半導体記憶装置およびその作製方法

【課題】半導体記憶装置におけるデータ保持のためのリフレッシュ動作の回数を低減し、消費電力の小さい半導体記憶装置を提供する。また、三次元の形状を適用することで、集積度を高めても短チャネル効果の影響が低減され、かつ従来に比べてフォトリソグラフィ工程数の増加を抑えた半導体記憶装置を提供する。

【解決手段】溝部の設けられた絶縁膜103と、溝部を挟んで離間した一対の電極116と、溝部の側面および底面と接し、溝部の深さよりも厚さの薄い、一対の電極116と接する酸化物半導体膜106と、酸化物半導体膜106を覆うゲート絶縁膜112と、ゲート絶縁膜112を介して酸化物半導体膜106と重畳して設けられたゲート電極112と、を有するトランジスタ150と、キャパシタ160と、を有する半導体記憶装置である。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、見かけ上のチャネル長に対してチャネル長を長くする方法は、溝を掘るためにフォトリソグラフィ工程を余分に行う必要があり、コストや歩留まりの観点で問題があった。

【解決手段】ゲート電極または絶縁表面を有する構造物を利用し、三次元形状のチャネル領域を形成することにより、チャネル長が、上面から見たチャネル長に対して3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとする。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

強誘電体メモリ・デバイスの作製方法

【課題】タグ、ラベル又はパッケージの印刷プロセス、あるいは、パッケージング・プロセス自体に容易に採用できる再書き込み可能な不揮発性メモリ・デバイスを作製する簡易で安価な方法を提供する。

【解決手段】a)第1の印刷手段を用いて絶縁性基板上に第1の印刷インクで第1の電極層を印刷し、それによって第1の組の電極を形成するためと、b)第2の印刷手段を用いて第1の電極層上に第2の印刷インクでメモリ材料のパターニングされた、あるいは、パターニングされていない層を印刷し、c)第3の印刷手段を用いてメモリ層上に第3の印刷インクで第2の電極層を印刷し、それによって第2の組の電極を形成するための連続した工程を含み、それら単独又は組合せのいずれかで実行される作製方法を提供する。

(もっと読む)

半導体装置

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装

置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び

有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電

層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあ

わせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

キャパシタ、半導体装置及びそれらの製造方法

【課題】高い比誘電率を有する容量絶縁膜を使用して、静電容量を大きくし、しかもリーク電流を低減する。

【解決手段】容量絶縁膜として、c軸配向した結晶酸化ニオブを用い、特に成膜時の酸素含有量を、例えば、スパッタガスにおける酸素ガス比を調整することで制御して、a軸配向ピークを示さず、c軸配向ピークが優先した膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】チタン酸ストロンチウム膜を容量絶縁膜として用いたキャパシタにおいて、静電容量が大きく、リーク電流が小さいキャパシタを形成する。

【解決手段】半導体装置の製造方法は、下部電極を形成後、下部電極上に中間窒化チタン膜及び非晶質チタン酸ストロンチウム膜が互いに接するように積層された積層膜を形成する。次に、第1の熱処理を行うことにより、中間窒化チタン膜及び非晶質チタン酸ストロンチウム膜を結晶質チタン酸ストロンチウム膜に変換する。次に、結晶質チタン酸ストロンチウム膜上に上部電極を形成する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】 セル面積の縮小が可能であり、かつ、最小加工寸法がメモリセルを構成する材料の膜厚に制限されない半導体記憶装置を提供すること。

【解決手段】 半導体記憶装置において、Y方向に延伸する複数のワード線WL1nの上方に、ゲート絶縁膜104、X方向に延伸するチャネル106、X方向に延伸する抵抗変化素子108を順に形成し、複数のワード線のそれぞれの上方に、チャネルの一部および抵抗変化素子の一部を配置する(MC11n)。係る構成により、セル面積を縮小し、かつ、設計の自由度を担保しうる。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

半導体装置

【課題】不揮発型抵抗変化素子の低抵抗時の信頼性を向上させる。

【解決手段】少なくとも2つの論理回路15、16と、前段の論理回路15と後段の論理回路16との間を電気的に接続可能とする抵抗変化型不揮発素子14とを備え、抵抗変化型不揮発素子は、抵抗値が電気的に書き換え可能であり、抵抗値が高抵抗状態から低抵抗状態へ遷移するために必要な印加電圧もしくは電流の方向と、低抵抗状態から高抵抗状態へ遷移するために必要な印加電圧もしくは電流の方向とが逆の関係にあるような両極型の遷移特性を有し、前段の論理回路は、前段の論理回路から出力され抵抗変化型不揮発素子を介して流れる信号電流のピーク値が、抵抗変化型不揮発素子が低抵抗状態に遷移する方向に大きく逆方向に小さくなるような駆動能力を有するように構成される。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。または、良好な特性を維持しつつ微細化を達成した半導体装置を提供する。

【解決手段】半導体層を形成し、半導体層上に、単層でなる第1の導電層を形成し、第1の導電層上に、365nm以下の波長の光を用いて第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電層をエッチングして、凹部を有する第2の導電層とし、第1のレジストマスクを縮小させて第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電層をエッチングして、周縁に突出部を有し、且つ突出部はテーパ形状であるソース電極及びドレイン電極を形成し、ソース電極及びドレイン電極上に、半導体層の一部と接するゲート絶縁層を形成し、ゲート絶縁層上の半導体層と重畳する位置にゲート電極を形成する。

(もっと読む)

一時記憶回路、記憶装置、信号処理回路

【課題】トランジスタの数を少なくした構成の記憶素子を用いた一時記憶回路を提供する。

【解決手段】一時記憶回路は複数の記憶素子を有し、複数の記憶素子それぞれは、第1のトランジスタと、第2のトランジスタとを有し、第1のトランジスタはチャネルが酸化物半導体層に形成され、ゲートに入力される制御信号によってオン状態を選択された第1のトランジスタを介して、データに対応する信号電位を第2のトランジスタのゲートに入力し、ゲートに入力される制御信号によって第1のトランジスタをオフ状態とすることによって、第2のトランジスタのゲートに当該信号電位を保持し、第2のトランジスタのソース及びドレインの一方を第1の電位としたとき、第2のトランジスタのソースとドレイン間の状態を検出することによってデータを読み出す。

(もっと読む)

記憶装置

【課題】誤書込みを防止することが可能な記憶装置を提供する。

【解決手段】複数のメモリセルが直列に接続されたNANDセルユニットと、NANDセルユニットの一方の端子に接続する第1の選択トランジスタと、NANDセルユニットの他方の端子に接続する第2の選択トランジスタと、第1の選択トランジスタと接続するソース線と、該ソース線と交差し、且つ第2の選択トランジスタと接続するビット線とを有し、第1の選択トランジスタ及び第2の選択トランジスタは、チャネル領域が酸化物半導体層で形成されたトランジスタである。

(もっと読む)

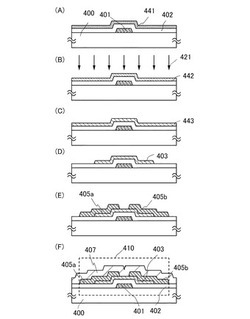

半導体装置の作製方法

【課題】オフ電流の極めて小さい酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを適用することで、消費電力の極めて小さい半導体装置を提供する。

【解決手段】基板上に加熱処理により酸素を放出する下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、基板を加熱処理する。次に、第1の酸化物半導体膜上に導電膜を形成し、該導電膜を加工してソース電極およびドレイン電極を形成する。次に、第1の酸化物半導体膜を加工して第2の酸化物半導体膜を形成した直後にソース電極、ドレイン電極および第2の酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極を形成する。

(もっと読む)

141 - 160 / 509

[ Back to top ]