Fターム[5F083KA05]の内容

Fターム[5F083KA05]の下位に属するFターム

階層型ビット線 (163)

基板埋込型ビット線 (91)

拡散層で形成されたビット線 (218)

Fターム[5F083KA05]に分類される特許

201 - 220 / 1,029

半導体装置および半導体装置の製造方法

【課題】ロジック回路のコンタクト抵抗の増加を抑制しつつ、メモリ回路のキャパシタ容量を最大限に高めることが実現される半導体装置の構造およびその製造方法を提供する。

【解決手段】半導体装置においては、ロジック回路を構成する配線を有する配線層の層数をMとし、メモリ回路を構成する配線を有する配線層の層数をNとしたとき(MおよびNは自然数であって、M>N)、(M−N)層あるいは(M−N+1)層の配線層にわたって、容量素子150が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】3次元的に形成したトランジスタやサイリスタのリーク電流を低減する半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板10の主面に対してほぼ垂直に形成されたシリコンピラー12と、シリコンピラー12の下部及び上部にそれぞれ設けられた第1及び第2の不純物拡散層14,16と、シリコンピラー12を水平方向に貫いて設けられたゲート電極18と、ゲート電極18とシリコンピラー12との間に設けられたゲート絶縁膜20と、シリコンピラー12に隣接して設けられたバックゲート電極48と、バックゲート電極48とシリコンピラー12との間に設けられたバックゲート絶縁膜46とを備える。

(もっと読む)

不揮発性メモリ装置およびその動作方法と、それを含むメモリシステム

【課題】本発明は少ない消去単位を有する不揮発性メモリ装置の動作方法を提供する。

【解決手段】本発明の不揮発性メモリ装置の動作方法は、ビットラインに接続された第1ストリングの接地選択ラインをフローティングし、ビットラインに接続された第2ストリングの接地選択ラインに消去禁止電圧を印加し、そして第1及び第2ストリング等に消去動作電圧を印加する。

(もっと読む)

半導体装置の製造方法

【課題】レジスト膜のスリミング時にその膜厚の消費を抑制する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基体11上に複数の絶縁層25と複数の導電層WLとを交互に積層して積層体を形成する工程と、積層体上にレジスト膜50を形成する工程と、レジスト膜50をマスクにして絶縁層25及び導電層WLをプラズマエッチングする工程と、ホウ素、リン及びヒ素の少なくとも1つを含むガスを用いたプラズマ処理により、レジスト膜50の上面に、ホウ素、リン及びヒ素の少なくとも1つを含む硬化層51を形成する工程と、レジスト膜50の上面に硬化層51が形成された状態で、酸素を含むガスを用いたプラズマ処理によりレジスト膜50の平面サイズをスリミングする工程と、を備えた。

(もっと読む)

記憶装置及びその製造方法

【課題】シリコンダイオードと電極膜との間のコンタクト抵抗が低い記憶装置及びその製造方法を提供する。

【解決手段】少なくとも上層部分が不純物が導入されシリコンを含有する半導体材料からなるシリコンダイオードを形成し、このシリコンダイオード上に、金属からなる金属層を堆積させる。次に、この金属層上に、金属の窒化物からなる金属窒化物層を堆積させ、次に、抵抗変化膜を形成する。その後、熱処理を施すことにより、シリコンダイオード、金属層及び金属窒化物層を反応させて、金属、シリコン及び窒素を含有する電極膜を形成する。これにより、記憶装置を製造する。

(もっと読む)

不揮発性半導体記憶装置

【課題】集積度が高い不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置において、それぞれ複数の絶縁膜及び電極膜14が交互に積層された積層体と、この積層体内に埋設され、絶縁膜及び電極膜14の積層方向に延びるシリコンピラー31と、電極膜14とシリコンピラー31との間に設けられた電荷蓄積層26と、を設ける。そして、電極膜14を、それぞれが電荷蓄積層26を挟んでシリコンピラー31に対向する複数の制御ゲート電極CGa及びCGbに分割する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体OSを用い、オフ状態でのソースとドレイン間のリーク電流(オフ電流)が少ない書き込み用トランジスタ162、書き込み用トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルを有する半導体装置において、メモリセルへの情報の書き込みは、書き込み用トランジスタ162のソース電極またはドレイン電極の一方と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードFGに電位を供給し、ノードFGに所定量の電荷を保持させることで行う。書き込みを1×109回行う前後において、メモリセルのメモリウィンドウ幅の変化量は2%以内である。

(もっと読む)

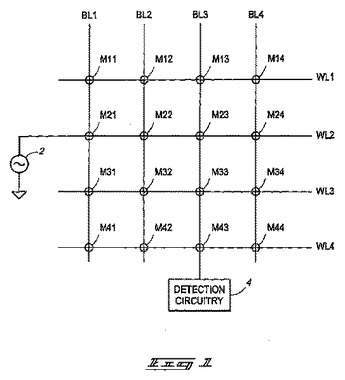

クロスポイントメモリセル、不揮発性メモリアレイ、メモリセルの読み出し方法、メモリセルのプログラミング方法、メモリセルへの書き込み方法およびメモリセルからの読み出し方法、ならびにコンピュータシステム。

クロスポイントメモリセル、不揮発性メモリアレイ、メモリセルを読み出す方法、メモリセルをプログラミングする方法、メモリセルへの書き込み方法およびメモリセルからの読み出し方法が記述される。一実施形態においては、クロスポイントメモリセルは、第一の方向に伸長するワード線と、第一の方向とは異なる第二の方向に伸長するビット線とを含み、ビット線およびワード線は、お互いに物理的に接触することなく交差する。クロスポイントメモリセルは、そのように交差する位置でワード線およびビット線の間に形成されるキャパシタを含む。キャパシタは、ワード線からビット線へと流れる直流電流およびビット線からワード線へと流れる直流電流を妨げるように構成された誘電体材料を含む。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の駆動方法

【課題】隣接セル間の干渉の影響を抑制し、データリテンション特性の向上を図ること。

【解決手段】本発明は、メモリ部と、制御部と、を備え、制御部は、複数の記憶領域MEの全てに消去の情報を設定し、メモリセルトランジスタTrの全てについて消去の閾値に設定した後、記憶領域MEにn(nは2以上の整数)値の情報を書き込み、記憶領域MEに設けられたメモリセルトランジスタTrをn値の情報に応じた閾値に設定した状態で、情報の書き込み済みの記憶領域MEに隣接する少なくとも1つの書き込み前の記憶領域MEの情報が、メモリセルトランジスタTrの閾値として、消去の閾値よりも、n値の情報に応じた閾値に近い値になるよう制御する。

(もっと読む)

半導体装置

【課題】チップ面積を縮小しつつ、高信頼性を実現する半導体装置を提供する。

【解決手段】半導体装置は、第1、第2配線S1,S2を有する第1回路部210と、第3、第4配線S3、S4を有する第2回路部220と、それらの間に設けられ、第1回路部210から第2回路部220に向かう方向に直交する方向に沿って隣接する第1、第2トランジスタTR1、TR2を有する中間部230と、を備え、第1トランジスタTR1の一方の拡散層DA1の第1接続領CA1内の高濃度領域CAI1は第1配線S1に、他方の拡散層DB1は第3配線S3に接続される。第1接続領域CA1とゲートG01との距離は、第2接続領域CA2とゲートG02との距離よりも長い。第1トランジスタTR1の一方の拡散層DA1の第1接続領域CA1とゲートG01との間には、第1接続領域CA1よりも幅が狭い延在領域EA1が設けられる。

(もっと読む)

不揮発性記憶装置及びその製造方法

【課題】安定した動作が可能な不揮発性記憶装置及びその製造方法を提供する。

【解決手段】第1主面110fと、第1主面とは反対側の第2主面110mと、を有する第1導電層110と、第1主面に対向し、第1主面に対して平行な平面を含む第3主面120fと、第3主面の第1主面とは反対の側に設けられた第4主面120mと、第3主面と第4主面とに接する側面120sと、第3主面と側面との間に設けられ、第3主面よりも曲率が高い角部120cと、を有する第2導電層120と、第1導電層と第2導電層との間に設けられ、印加される電界及び通電される電流の少なくともいずれかによって電気抵抗が変化する抵抗変化層130と、第1導電層の第2主面に対向して設けられた整流素子70と、を備えた不揮発性記憶装置が提供される。第3主面の面積は、第2主面の面積よりも小さい。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】裏打ち領域におけるコンタクトホール形成領域を最適化することにより、記憶密度が向上された不揮発性半導体記憶装置及びその製造方法を提供すること。

【解決手段】本発明は、裏打ち領域2と、X方向に並ぶ2つのメモリセル領域1に挟まれる裏打ち領域2を有する。メモリセル領域1はメモリセル50が配置される。メモリセル50はY方向に離間された2つのメモリゲート12と、これらのサイドウォールである2つの選択ゲート17と、を有する。裏打ち領域2は、メモリセル領域1でX方向に並ぶメモリセル50の選択ゲート17のそれぞれと接続される、2本の選択ゲート線6を有する。それぞれ選択ゲート線6は、他方に向かって突出するコンタクトホール形成領域6aを有する。それぞれのコンタクトホール形成領域6aはX方向に離間されて形成されている。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】安定した動作を実行可能な不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】メモリストリングMSは、メモリ柱状半導体層36と、メモリ柱状半導体層36の側面を取り囲むように形成された電荷蓄積層を含むメモリゲート絶縁層35と、メモリゲート絶縁層35を取り囲むように形成された4層のワード線導電層31a〜31dと、ワード線導電層31a〜31dの上部を保護する2層の保護層33a、33bとを備える。ワード線導電層31a〜31dは、その端部の位置が異なるように階段状に形成された階段部STを構成する。下から2段目のステップST2は、その上面を2層の保護層33a、33bにて覆われ、下から1段目のステップST1は、その上面を1層の保護層33aにて覆われている。

(もっと読む)

抵抗変化メモリ

【課題】ドライバ領域の増加を最小限に抑え、抵抗変化メモリの三次元化を実現する。

【解決手段】本発明の抵抗変化メモリは、半導体基板11上に、第1導電線、第1可変抵抗素子、第2導電線、第2可変抵抗素子、…第n導電線、第n可変抵抗素子、及び、第(n+1)導電線の順番で、積み重ねられる積層構造(但し、nは、2以上の自然数)と、第1乃至第(n+1)導電線L1(1),L2(1),…L(n+1)(1)を駆動する第1乃至第(n+1)ドライバDr1(1),Dr2(1)とを備える。第1乃至第(n+1)ドライバDr1(1),Dr2(1)のサイズは、第1ドライバから第(n+1)ドライバに向かって次第に大きくなる。

(もっと読む)

半導体装置及びその製造方法

【課題】DRAM素子のような半導体装置において、周辺回路領域に配置する回路の占有面積が削減でき、チップサイズの小さな半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に、不純物をドープして形成したメモリセル拡散層72を含むメモリセル領域7と、周辺回路拡散層82とゲート電極4を含む周辺回路領域8を備え、メモリセル領域7ではメモリセル拡散層72に接続されるビット配線10Aとして設けられ、周辺回路領域8では周辺回路拡散層82あるいはゲート電極42の何れかに接続する第1中間配線層10Bとして設けられる第1配線と、メモリセル領域7ではメモリセル拡散層72と接続されるキャパシタ用容量パッド20Aとして設けられ、周辺回路領域8では、コンタクトプラグの積層構造を介して周辺回路拡散層82あるいはゲート電極42の何れか一方に接続する第2中間配線層20Bとして設けられる第2配線20とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】3次元的に形成したDRAM用のトランジスタやサイリスタのリーク電流を低減する半導体装置及びその製造方法を提供する。

【解決手段】基板10の主面に対してほぼ垂直に形成されたシリコンピラー12と、シリコンピラー12の下部及び上部にそれぞれ設けられた第1及び第2の不純物拡散層14,16と、シリコンピラー12を水平方向に貫いて設けられたゲート電極18と、ゲート電極18とシリコンピラー12との間に設けられたゲート絶縁膜20とを備える。これによれば、シリコンピラー12の体積が小さくなるので、シリコンピラー12内に形成されるトランジスタやサイリスタのリーク電流を低減できる。

(もっと読む)

炭素/トンネル障壁/炭素・ダイオード

炭素/トンネル障壁/炭素・ダイオード及び炭素/トンネル障壁/炭素・ダイオードの形成方法を開示する。炭素/トンネル障壁/炭素はメモリアレイ内でステアリング素子として用いられてもよい。メモリアレイ内の各メモリセルは可逆的抵抗性スイッチング素子、及びステアリング素子として炭素/トンネル障壁/炭素・ダイオードを含んでいてもよい。トンネル障壁は半導体又は絶縁体を含んでいてもよい。従って、ダイオードは炭素/半導体/炭素・ダイオードであってもよい。ダイオード内の半導体は真性であってもよいし、ドープされていてもよい。ダイオードが平衡状態にある場合は、半導体が空乏化されることがある。例えば、空乏領域が半導体領域の一端から他端まで延びるように、半導体が低濃度にドープされてもよい。ダイオードは炭素/絶縁体/炭素・ダイオードであってもよい。 (もっと読む)

半導体記憶装置

【課題】周囲の不要なセルから受ける影響を低減出来る半導体記憶装置を提供する。

【解決手段】第1信号線と、第2信号線と、前記第1信号線に隣接しつつ形成された第1ダミー配線FAT_DMY_BLと、前記第2信号線に隣接しつつ形成された第2ダミー配線FAT_DMY_WLと、前記第1信号線と前記第2信号線とが交差する第1領域に設けられ、前記第1信号線と前記第2信号線によって電圧が印加されるメモリセルMCと、前記第1ダミー配線と前記第2ダミー配線とが交差する第2領域に設けられ、前記第1ダミー配線と前記第2ダミー配線とによって電圧が印加される第1ダミーセルと、前記第1、第2信号線に電圧印加可能なデコーダとを具備し、前記第1、第2ダミー配線の電位は、前記第1ダミーセルに逆バイアスが生じるように固定される。

(もっと読む)

不揮発性メモリ

【課題】酸化物半導体層を含むトランジスタを有する不揮発性メモリにおいて、保持された情報を容易に消去できる不揮発性メモリを提供する。

【解決手段】不揮発性メモリは、第1のトランジスタ20及び第2のトランジスタ21を有するメモリセルを有し、第1のトランジスタ20は第1のチャネル、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有し、第2のトランジスタ21は酸化物半導体からなる第2のチャネル、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有し、第2のソース電極及び第2のドレイン電極の一方は第1のゲート電極と電気的に接続され、メモリセルへの情報の書き込み及び消去は、第2のソース電極及び第2のドレイン電極の一方と、第1のゲート電極との間のノードの電位を高くすることにより情報が書き込まれ、第2のチャネルに紫外線を照射して、ノードの電位を低くすることにより情報が消去される。

(もっと読む)

半導体装置の製造方法

【課題】強誘電体キャパシタのキャパシタ誘電体膜がダメージを受けるのを抑制する半導体装置の製造方法を提供する。

【解決手段】シリコン基板1の上方に第1の絶縁膜を形成する工程と、第1の絶縁膜の上に、第1の導電膜20、強誘電体膜21、及び第2の導電膜を形成する工程と、第2の導電膜の上にハードマスク23aを形成する工程と、ハードマス23aをマスクにし、第2の導電膜をエッチングして上部電極22aにする工程と、強誘電体膜21をパターニングしてキャパシタ誘電体膜にする工程と、第1の導電膜20をエッチングして下部電極にする工程とを有し、第2の導電膜をエッチングする工程において、上部電極22aの横に強誘電体膜21が露出したときに、エッチング雰囲気が、酸素ガスを含み且つハロゲンを含まない雰囲気となっている。

(もっと読む)

201 - 220 / 1,029

[ Back to top ]