Fターム[5F083KA05]の内容

Fターム[5F083KA05]の下位に属するFターム

階層型ビット線 (163)

基板埋込型ビット線 (91)

拡散層で形成されたビット線 (218)

Fターム[5F083KA05]に分類される特許

141 - 160 / 1,029

半導体装置及びその製造方法

【課題】本発明は、トランジスタを容易にOn(オン)させることが可能で、かつ良好なデータ保持特性を実現することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板12に形成され、第1の方向に延在する第1の素子分離用51、及び第1の素子分離用溝51を埋め込む第1の素子分離用絶縁膜53よりなり、複数の素子形成領域Rを有した活性領域16を区画する第1の素子分離領域14と、半導体基板12に、第1の方向と交差する第2の方向(Y方向)に延在するように形成され、第1の素子分離領域14の一部を分断する第2の素子分離用溝54、及び第2の素子分離用溝54を埋め込む第2の素子分離用絶縁膜56よりなり、複数の素子形成領域Rを区画する第2の素子分離領域17と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

半導体装置

【課題】コンタクトパッドを含む所定領域内に形成できる配線数を増加させることができ、設計レイアウトの自由度を向上させることができるパターンレイアウトを有する半導体装置を提供する。

【解決手段】第1方向に所定ピッチでラインとスペースが交互に配列された第1配線パターンと、第1配線パターンのライン間に配置され、所定ピッチの3倍の幅を有するコンタクトパッド30Bとを有する。第1配線パターンのラインとコンタクトパッドとの間隔は所定ピッチであり、所定ピッチは100nm以下である。

(もっと読む)

半導体装置

【課題】配線の引き出し性が向上されているとともに、配線間の短絡などの電気的問題が生じるおそれが抑制されており、かつ、配線が形成される領域の省スペース化が図られた半導体装置を提供する。

【解決手段】半導体装置1が備える基板4上の所定の層内に、第1の配線3が複数本並べられて設けられている。各第1の配線3は、それらの並べられた方向に沿って一方の側から他方の側へ向かうに連れて長く延ばされて形成されているか、あるいは短く縮められて形成されている。それとともに、各第1の配線3は、隣接するそれぞれの一端部3aが並べられた方向と直交する方向において互いにずれた位置に配置されている。

(もっと読む)

3次元半導体記憶素子

【課題】優れた信頼性を有し、高集積化のために最適化された3次元半導体記憶素子が提供される。

【解決手段】本発明の素子によれば、積層構造体が基板上に配置されて第1の方向に延長される。積層構造体は交互に反復的に積層されたゲートパターン及び絶縁パターンを含む。垂直形活性パターンが積層構造体を貫通する。積層構造体は第1の部分及び第2の部分を含み、積層構造体の第2の部分は第1の方向と垂直である第2の方向に第1の部分より小さい幅を有する。積層構造体の第2の部分の横にストラッピングコンタクトプラグが配置されて、共通ソース領域と接触される。

(もっと読む)

半導体装置

【課題】導電性ブリッジの消去動作時の消去時間のばらつきの最大値を抑えて、メモリ素子の書き換え時間を短縮する。

【解決手段】半導体装置は、第1の面から厚み方向の内側に向かって形成された孔部を有する第1絶縁膜と、第1絶縁膜上に設けられ第1イオン伝導体を含む抵抗変化層と、孔部内壁の側面及び底面を覆うと共に凹部を有するように孔部内に形成され上端を介して抵抗変化層に接する第1電極と、第1電極の凹部内に埋め込まれると共に第1電極よりも大きい電子抵抗を有する埋め込み層と、抵抗変化層上に第1電極の上端及び埋め込み層と共に抵抗変化層を挟むように形成された第2電極とを有する半導体素子、を備える。半導体素子は、抵抗変化層内において、第1電極の上端と第2電極の間に導電性架橋を可逆的に形成することにより第1電極と前記第2電極の間の電子抵抗を変化させる。

(もっと読む)

半導体装置の製造方法

【課題】 半導体記憶装置に係り、特に、高集積化されたDRAMを、少ない工程数で、且つ微細なセル面積で実現できる半導体記憶装置及びその製造方法を提供する。

【解決手段】 半導体基板10に形成されたメモリセルトランジスタと、メモリセルトランジスタのゲート電極20の上面及び側面を覆う絶縁膜42と、ソース拡散層24上に開口したスルーホール40と、ドレイン拡散層26上に開口したスルーホール38とが形成された層間絶縁膜36と、スルーホール40内壁及び底部に形成され、ソース拡散24層に接続されたキャパシタ蓄積電極46と、キャパシタ蓄積電極46を覆うキャパシタ誘電体膜48と、キャパシタ誘電体膜48を覆うキャパシタ対向電極54とを有するキャパシタと、スルーホール38の内壁及び底部に形成され、ドレイン拡散層と接続されたコンタクト用導電膜44とにより構成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去状態におけるセル電流の値の変動を抑制可能な不揮発性半導体記憶装置の提供。

【解決手段】基板の主面に平行な第1の方向に延びるよう区画された複数の素子領域111と、前記素子領域上に形成された複数のメモリセルを含むメモリセルアレイ領域121と、前記第1の方向に延びるよう形成された複数のビット線131とを備え、前記複数のビット線の同じ側の端部に電気的に接続されたセンスアンプ回路141と、前記素子領域上に、前記素子領域と前記ビット線とを電気的に接続するよう形成された複数のビット線コンタクトCBとを備える。前記メモリセルアレイ領域は、第1から第Nの領域(N≧2)を含み、第Kの領域(2≦K≦N)は、第K−1の領域よりも前記センスアンプ回路から遠い位置に位置し、前記第Kの領域内の前記ビット線コンタクトのコンタクト抵抗は、前記第K−1の領域内の前記ビット線コンタクトのコンタクト抵抗よりも低い。

(もっと読む)

結晶性酸化物半導体膜の作製方法

【課題】優れた結晶性を有する酸化物半導体膜を作製する。

【解決手段】酸化物半導体の膜を形成するに際し、基板を第1の温度以上第2の温度未満に加熱しつつ、基板の、典型的な長さが1nm乃至1μmの部分だけ、第2の温度以上の温度に加熱する。ここで、第1の温度とは、何らかの刺激があれば結晶化する温度であり、第2の温度とは、刺激がなくとも自発的に結晶化する温度である。また、典型的な長さとは、その部分の面積を円周率で除したものの平方根である。

(もっと読む)

半導体装置

【課題】半導体装置の省スペース化を実現する。

【解決手段】半導体基板5に、センスアンプが備えられた周辺回路領域Sとメモリセル領域Mとが区画形成され、メモリセル領域Mにおいて、半導体基板5の一面に形成されたトレンチ溝内に、ゲート絶縁膜を介しゲート電極を含む埋込ワード線9とその上に位置する埋込絶縁膜とが埋め込まれ、前記トレンチ溝に隣接する半導体基板5一面の表面領域に不純物拡散層が形成され、前記不純物拡散層が形成された領域上にはビット配線15が形成されており、ビット配線15が周辺回路領域Sまで延長され、周辺回路領域Sにおいてビット配線15が前記センスアンプを構成するMOSトランジスタのゲート電極Gとされていることを特徴とする半導体装置を採用する。

(もっと読む)

半導体装置

【課題】小型化が可能な不揮発性メモリを備えた半導体装置を提供する。

【解決手段】基板901上に画素と不揮発性メモリとを備え、不揮発性メモリは、基板901上に形成される半導体活性層と、半導体活性層上に形成される絶縁膜923と、絶縁膜923上に形成されるフローティングゲイト電極907と、フローティングゲイト電極907を酸化して得られる酸化膜908,915,922と、酸化膜908,915,922に接して形成されるコントロールゲイト電極929と、を備え、画素と不揮発性メモリとは、基板901上に一体形成される。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】不揮発性記憶装置およびその製造方法に関し、抵抗変化材料を利用したメモリの信頼性の向上を実現する。

【解決手段】積半導体素子を形成する基板の上方に、第1方向に延伸するように複数の金属配線層2を設け、金属配線層2のさら上方に、前記第1方向に直交する第2方向に延伸するように複数の金属配線層3を設ける。また、金属配線層2と金属配線層3とが交差する空間のそれぞれにメモリセルを設ける。前記メモリセルは、選択素子と相変化材料層7とが並列接続された構成とする。ここで、前記選択素子の前記第1方向の寸法が、相変化材料層7の前記第1方向の寸法よりも大きくなるように加工する。

(もっと読む)

半導体記憶装置

【課題】SRAMのゲート配線形成にあたって、ゲート形状を複雑に変形させることなく転写及び加工マージンを確保する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1組及び第2組のドライバトランジスタ11、ロードトランジスタ12及びアクセストランジスタ13とを備えたメモリセルが半導体基板上に2次元配列されたメモリセルアレーと、複数のワードラインと、複数のビットラインと、第1組のドライバトランジスタ11とロードトランジスタ12とを接続し、直線状の側辺を有する長方形状の第1ゲート配線3aと、アクセストランジスタ13と接続され、直線状の側辺を有する長方形状の第2ゲート配線3cと、第1ゲート配線3aと、第2組のドライバトランジスタ11とロードトランジスタ12とを接続する第1コネクタ5aと、第2ゲート配線3cとワードラインとを接続する第2コネクタ5cとを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】高速動作が可能な半導体装置を提供する。

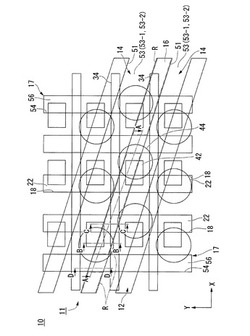

【解決手段】本発明に係る半導体装置は、第1の方向に平行に延在する第1素子分離溝部とそれに交差する方向に延在する第2素子分離溝部とが交互に連なってなる素子分離溝に第1絶縁膜を埋め込んで形成された素子分離領域を複数備え、素子分離領域間に第1素子形成部と第2素子形成部とが交互に連なってなる素子形成領域を複数備え、各第1素子形成部は所定数の第1半導体ピラーを備え、各第2素子形成部は第2半導体ピラーを備え、各素子形成領域はピラーの下部に不純物拡散層からなる第1のビット線を備え、ピラーの上部に上部不純物拡散層を備え、各素子形成領域の第2半導体ピラーの上部不純物拡散層に電気的に接続する第1のビット線より低抵抗の第2のビット線を備え、ピラーの下部側壁に第2絶縁膜を介して第2の方向に延在するワード線を備えることを特徴とする。

(もっと読む)

半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな駆動方法を提供する。また、新たな駆動方法により、メモリ素子への書き込み電位のばらつきを低減し、信頼性を向上させる。

【解決手段】半導体装置の駆動方法において、書き込み電位を段階的に上昇させて、同時に読み出し電流を確認し、読み出し電流の結果を書き込み電位に利用して書き込みを行う。つまり、正しい電位で書き込みが行われたか確認しながら書き込みを行うことで、信頼性の高い書き込みを行うことが可能である。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】1つの実施形態は、絶縁膜に形成された溝に導電物質を容易に埋め込むことができる半導体装置の製造方法、及びそのような製造方法に適した半導体装置を提供する。

【解決手段】1つの実施形態によれば、コンタクトプラグを形成し、コンタクトプラグを覆うエッチングストッパー膜を形成し、エッチングストッパー膜を覆う絶縁膜を形成し、絶縁膜及びエッチングストッパー膜にコンタクトプラグの表面を露出する溝を形成し、エッチングストッパー膜のエッチングレートに対し絶縁膜のエッチングレートの方が高くなる条件で、コンタクトプラグとコンタクトプラグの周辺とを含む領域を選択的にエッチバックし、エッチバックを行った後に溝に導電物質を埋め込んでラインパターンを形成する。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】より低抵抗な配線層を有する不揮発性記憶装置を提供する。

【解決手段】実施形態の不揮発性記憶装置は、書き替え可能な複数の不揮発性メモリセルと、前記複数のメモリセルのそれぞれに電気的に接続可能な配線層と、を備えた不揮発性半導体記憶装置である。前記配線層は、絶縁層に設けられたトレンチ内に設けられ、前記配線層は、第1導電層と、前記第1導電層の上に設けられた第2導電層と、を有し、前記配線層が充填されていない前記トレンチに対する前記第1導電層の埋め込み性は、前記配線層が充填されていない前記トレンチに対する前記第2導電層の埋め込み性よりも高く、前記第2導電層の比抵抗は、前記第1導電層の比抵抗よりも低い。

(もっと読む)

半導体装置の製造方法

【課題】隣接する活性領域の間で横方向に成長するシリコン膜が連結されることを防ぎつつ、活性領域上に十分な厚みのシリコン膜を形成可能とした半導体装置の製造方法を提供する。

【解決手段】ゲート電極6aを挟んだ両側の活性領域5上に第1のシリコン膜12aを選択的にエピタキシャル成長させる工程と、複数のワード配線層WLの各間に第1のシリコン膜12aを覆うのに十分な厚みでマスク絶縁膜を埋め込んだ後、このマスク絶縁膜を第1のシリコン膜12aの表面が露出するまでエッチングにより除去する工程と、第1のシリコン膜12a上に第2のシリコン膜12bを選択的にエピタキシャル成長させる工程とを含む。

(もっと読む)

論理回路とそれを使用するメモリ

【課題】

低い電源電圧でも動作可能な論理回路を提供する。

【解決手段】

論理回路は,電源電圧側に接続された第1導電型の第1のMOSFETと,基準電圧側に接続されゲートに入力信号が供給される第1導電型の第2のMOSFETと,第1,第2のMOSFETの電流端子の接続ノードに接続された出力端子と,第1のMOSFETのゲートとソース間に設けられたカップリングキャパシタと,第1のMOSFETのゲートと電源電圧との間に設けられた抵抗とを有する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】信頼性が高い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、電極膜及び絶縁膜が交互に積層され、端部の形状が前記電極膜毎にステップが設けられた階段状である積層体と、前記端部の上方から前記電極膜に接続されたコンタクトと、前記積層体の前記端部以外の部分に設けられ、前記積層体を積層方向に貫く半導体部材と、前記電極膜と前記半導体部材との間に設けられた電荷蓄積層と、前記端部を前記積層方向に貫く貫通部材と、を備える。そして、前記貫通部材には、前記電荷蓄積層を形成する材料と同種の材料が含まれていない。

(もっと読む)

141 - 160 / 1,029

[ Back to top ]