Fターム[5F083KA05]の内容

Fターム[5F083KA05]の下位に属するFターム

階層型ビット線 (163)

基板埋込型ビット線 (91)

拡散層で形成されたビット線 (218)

Fターム[5F083KA05]に分類される特許

81 - 100 / 1,029

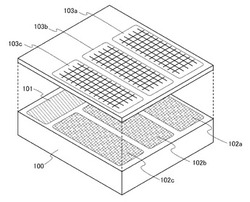

記憶装置及び半導体装置

【課題】データの保持期間を確保しつつ、単位面積あたりの記憶容量を高めることができる記憶装置を提供する。

【解決手段】複数のビット線を幾つかのグループに分割し、複数のワード線も幾つかのグループに分割する。そして、一のグループに属するビット線に接続されたメモリセルには、一のグループに属するワード線が接続されるようにする。さらに、複数のビット線は、複数のビット線駆動回路102a,102b,102cによってグループごとにその駆動が制御されるようにする。加えて、複数のビット線駆動回路102a,102b,102cと、ワード線駆動回路101とを含めた駆動回路上に、セルアレイ103a,103b,103cを形成する。駆動回路とセルアレイ103a,103b,103cが重なるように三次元化することで、ビット線駆動回路が複数設けられていても、記憶装置の占有面積を小さくすることができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

半導体記憶装置

【課題】記憶素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保しつつ、ユニットセルのレイアウト面積が従来よりも小さい半導体記憶装置を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板と、半導体基板に形成されたアクティブエリアを備える。複数のセルトランジスタがアクティブエリアに形成されている。第1のビット線および第2のビット線は、互いに対をなす。複数のワード線は第1および第2のビット線と交差する。複数の記憶素子の一端がセルトランジスタのソースまたはドレインに電気的に接続され、他端が第1または第2のビット線に接続されている。第1および第2のビット線は、両方とも同一のアクティブエリアに対して記憶素子を介して接続されている。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

記憶装置、及び半導体装置

【課題】高速動作を実現できる記憶装置、或いは、リフレッシュ動作の頻度が低減できる記憶装置を提供する。

【解決手段】セルアレイ101の内部において、メモリセル100に接続された配線に、駆動回路102から電位の供給が行われる。さらに、駆動回路102上にセルアレイ101が設けられており、セルアレイ101が有する複数の各メモリセル100は、スイッチング素子と、スイッチング素子により電荷の供給、保持、放出が制御される容量素子とを有する。そして、スイッチング素子として用いられるトランジスタは、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体を、チャネル形成領域に含んでいる。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の低抵抗化を図る。

【解決手段】本実施形態の半導体装置は、半導体基板10を覆う第1の層間絶縁膜上に設けられる配線60と、配線60の上面上に設けられるキャップ層68と、配線60と第2の層間絶縁膜との間に設けられるバリア膜62と、を含む。配線60は高融点導電層を含み、配線60の配線幅W1は、キャップ層68の幅W2よりも小さい。バリア膜62は、高融点導電層60が含む元素の化合物からなり、配線60を覆う層間絶縁膜69,70に起因する不純物が配線60内に拡散するのを抑制する。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

半導体記憶装置のデータ記録方法

【課題】電流切り替え用スイッチと相変化膜とが電気的に並列に形成されたメモリビットの複数個を電気的に直列に配置したメモリアレイ構造を持つ相変化メモリにおいて、転送速度性能の向上と信頼性の向上とを共に実現する。

【解決手段】パルス電流源により生成されたパルス電流の発生期間内に、直列に接続された複数のメモリビットのそれぞれの電流切り替え用スイッチを逐次的にON/OFFさせ、複数のメモリビットのうちの少なくとも一つのメモリビットの相変化膜に前記パルス電流の発生期間よりも短い期間の電流を流すことにより、前記複数のメモリビットに逐次的にデータを書き込む。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート電極用溝18の底部に設けられた第1の不純物拡散領域27と、第1の側面18aに配置されたゲート絶縁膜21の上部21Aを覆うように、半導体基板13に設けられた第2の不純物拡散領域28と、少なくとも第2の側面18bに配置されたゲート絶縁膜21を覆うように半導体基板13に設けられ、第1の不純物拡散領域27と接合された第3の不純物拡散領域29と、を有する。

(もっと読む)

半導体装置

【課題】SRAMのメモリセルにおける配線を確実に形成することがきて、電気的な接続が良好に行われる半導体装置を提供する。

【解決手段】半導体装置におけるSRAMのメモリセルでは、アクセストランジスタT1のゲート配線部GHA1に電気的に接続されるコンタクトプラグCPS1に対して、ワード線としての第3配線M32に電気的に接続されることになるヴィアVS1が直接接続されている。また、アクセストランジスタT2のゲート配線部GHA2に電気的に接続されるコンタクトプラグCPS2に対して、ワード線としての第3配線M32に電気的に接続されることになるヴィアVS2が直接接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ビット線コンタクトの抵抗が低減された半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、第1の方向に延在する半導体基板1に複数の第1の溝3aと該溝よりも幅狭でかつ平行に延在する複数の第2の溝3bとを第1の方向に直交する第2の方向に交互に離間して有し、第1の溝内にワード線7aが形成され、第2の溝には素子分離用導電層7cが埋設され、第1の溝の底面3Aから下方の領域に延在する下部拡散領域5を有し、ワード線7aは第1の溝内の第2の方向に平行でかつ対向する側壁のそれぞれに第2の絶縁膜6a、6bを介して形成されてなると共に第3の絶縁膜8で覆われており、素子分離用導電層7cはワード線と同じ材料でなり、底面3Aに下部拡散領域5に導通すると共に第3の絶縁膜8によってワード線7aと絶縁された半導体選択成長層10を備え、その層10上にビット線コンタクトを備えている、ことを特徴とする。

(もっと読む)

混合原子価導電性酸化物を用いたメモリ

【課題】混合原子価導電性酸化物を用いたメモリを提供する。

【解決手段】酸化されていない状態で導電性を有し、酸素欠乏状態で導電性が下がる混合原子価導電性酸化物酸素リザーバ635と、酸素に対する電解質であり、酸素イオンの移動を引き起こすのに有効な電場を促進する電解質トンネル障壁505と、を備える。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

半導体装置及びその製造方法

【課題】微細配線を簡易に低抵抗化する。

【解決手段】実施形態に係わる半導体装置は、第1の方向に積み重ねられる第1乃至第3の半導体層3a,3b,3cを有し、第2の方向に延びるフィン型積層構造を有する。第1のレイヤーセレクトトランジスタTaは、第1のゲート電極10aを有し、第1の半導体層3aでノーマリオン状態である。第2のレイヤーセレクトトランジスタTbは、第2のゲート電極10bを有し、第2の半導体層3bでノーマリオン状態である。第3のレイヤーセレクトトランジスタTcは、第3のゲート電極10cを有し、第3の半導体層3cでノーマリオン状態である。第1の半導体層3aのうちの第1のゲート電極10aにより覆われた領域、第2の半導体層3bのうちの第2のゲート電極10bにより覆われた領域及び第3の半導体層3cのうちの第3のゲート電極10cにより覆われた領域は、それぞれ金属シリサイド化される。

(もっと読む)

半導体装置

【課題】不揮発性であって、作製が簡単であり、追記が可能な記憶回路を有する半導体装置の提供を課題とする。

【解決手段】本発明の半導体装置は、複数のトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記複数のトランジスタのうちの1つの上に設けられた記憶素子及びアンテナとして機能する導電層とを有し、前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、アンテナとして機能する前記導電層と前記複数のトランジスタのソース配線又はドレイン配線として機能する導電層とは、同じ層上に設けられていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】ワードライン間の素子分離を行い、メモリセルの微細化が可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10内に形成されたビットライン14と、ビットライン14上にビットライン14の長手方向に連続して設けられた絶縁膜ライン18と、ビットライン14間の半導体基板10上に設けられたゲート電極16と、ゲート電極16上に接して設けられ、ビットライン14の幅方向に延在したワードライン20と、ビットライン14間でありワードライン20間の半導体基板に形成されたトレンチ部22と、を具備する。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】配線幅若しくは配線間隔の縮小に伴い、加工限界の制約を受けるために微細な配線形成が困難になりつつある。

【解決手段】絶縁層(第1の絶縁層12及び第2の絶縁層13)に溝15を形成し、導体膜(バリア膜16及び金属膜17)を溝15を埋設しない膜厚で形成し、続いて導体膜をエッチバックすることで溝15の側壁にサイドウォール状の配線18を形成することで、配線幅は導体膜の膜厚で制御できるために加工限界の制約を受けず、配線抵抗は配線高さを高くすることにより所定の配線抵抗を維持することができる。

(もっと読む)

不揮発性メモリ装置

【課題】 パストランジスタ間の空間確保が可能な不揮発性メモリ装置を提供する

【解決手段】 不揮発性メモリ装置100が備える行デコーダ120は、パストランジスタ部123_L、123_Rを含む。パストランジスタ部123_L、123_Rは、メモリブロック110の左右に配列される。ブロック選択信号BLKWL1によって共通ゲートを形成するパストランジスタ端Pass TR 0とパストランジスタ端Pass TR 8とは、選択的に活性化される第1駆動信号ラインSI1及び第2駆動信号ラインSI2によって独立して駆動される。互に異なるブロック選択信号BLKWLによって駆動されるパストランジスタは、1つの活性領域の上に形成され得る。これにより、1つの活性領域の上に2つのパストランジスタを形成する場合、パストランジスタ部123_L、123_Rのチャンネル方向の大きさを減らすことができる。

(もっと読む)

半導体装置

【課題】キャパシタの配列におけるデッドスペースをなるべくなくし、個々のキャパシタの形状をなるべく拡大した半導体装置を提供する。

【解決手段】半導体装置は、互いに隣接して平行に線状に延びる第1および第2トランスファーゲート2と、これらの間の間隙に配列され、それぞれ上方に延びる棒状の導電体からなる第1および第2ストレージノードコンタクト9と、第1の電極と第2の電極とが絶縁膜を介して対向配置されてなる第1キャパシタ14と、第3の電極と第4の電極とが絶縁膜を介して対向配置されてなる第2キャパシタ14とを備え、平面視において、第1の電極の第1トランスファーゲート側の一部のみに第1ストレージノードコンタクト9の上面が接続され、第3の電極の第2トランスファーゲート側の一部のみに第2ストレージノードコンタクト9の上面が接続されている。

(もっと読む)

半導体装置

【課題】製造時以外にデータの追記が可能であり、書き換えによる偽造等を防止可能な不揮発の記憶装置及びそれを有する半導体装置を提供することを課題とする。また、信頼性が高く、安価な不揮発の記憶装置及び半導体装置の提供を課題とする。

【解決手段】絶縁表面上に形成される第1の導電層と、第2の導電層と、第1の導電層及び第2の導電層に挟持される第1の絶縁層と、第1の導電層の一部を覆う第2の絶縁層とを有し、第1の絶縁層は第1の導電層の端部、絶縁表面、及び第2の絶縁層を覆うことを特徴とする記憶装置である。

(もっと読む)

81 - 100 / 1,029

[ Back to top ]