Fターム[5F083LA03]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | センスアンプ (769)

Fターム[5F083LA03]に分類される特許

41 - 60 / 769

不揮発性半導体記憶装置

【課題】正確に書き込み動作を行うことができる不揮発性半導体記憶装置を提供する。

【解決手段】

複数の素子分離絶縁膜は、半導体層中に形成され、第1方向を長手方向とする。複数の素子形成領域は、素子分離絶縁膜により分離して形成される。素子形成領域にはメモリストリングが形成される。複数の素子形成領域群が素子形成領域により構成される。メモリセルアレイは、第1方向と直交する第2方向において、前記素子形成領域群の間隔が前記素子形成領域群の中の前記素子形成領域の間隔より大きくされている。制御回路は、前記メモリセルアレイに対する書き込み動作を、前記素子形成領域群ごとに実行する。

(もっと読む)

半導体装置

【課題】補償容量としてのキャパシタを備えた補償容量領域において、その容量値を上げずにその面積を大きくして、製造工程時のキャパシタの剥がれを防止する。

【解決手段】第1の領域AR1に設けられたキャパシタ23の下部電極の各々には、端子A(M1)からVPERI電圧が供給されている。第2の領域AR2に設けられたキャパシタ23の下部電極の各々には、端子B(M1)からVSS電圧が供給されている。第3の領域AR3に設けられたキャパシタ23の下部電極の各々は、端子C(M1)から1/2VPERI電圧が供給されている。プレート24は、1/2VPERI電圧を第1〜3の領域AR1〜AR3のキャパシタ23の各上部電極に共通に供給している。第3の領域AR3は、各々の下部電極及び上部電極に同一電圧(1/2VPERI)が供給されるため容量に電荷が溜まることがない。

(もっと読む)

半導体記憶装置

【課題】 ビット線選択回路の小型化を図るとともにビット線の駆動時間を高速に行うことができる半導体記憶装置を提供する。

【解決手段】 フラッシュメモリ10は、セルユニットNUが行列状に複数配置されたメモリアレイ100と、セルユニットNUに接続されたビット線を選択するビット線選択回路200とを有する。ビット線選択回路200は、偶数ビット線GBL_e、奇数ビット線GBL_oをセンス回路に選択的に接続するための選択トランジスタSEL_e、SEL_o、BLSを含む第1の選択部210と、偶数ビット線GBL_eおよび奇数ビット線GBL_oに選択的にバイアス電圧を印加するためのバイアストランジスタYSEL_e、YSEL_oとを含む第2の選択部220とを有する。第2の選択部220のバイアストランジスタYSEL_e、YSEL_oは、記憶素子と共通のウエル内に形成される。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

メモリ回路

【課題】電源投入時における誤書き込みが発生しにくいメモリ回路を提供する。

【解決手段】メモリ回路10は、書き込み時のみにソース・ドレイン間に電圧を印加されて書き込まれる、書き込み用のPチャネル型不揮発性メモリ素子15と、コントロールゲート及びフローティングゲートがPチャネル型不揮発性メモリ素子15のコントロールゲート及びフローティングゲートとそれぞれ共通にされ、読み出し時のみにソース・ドレイン間に電圧を印加されて読み出される、読み出し用のNチャネル型不揮発性メモリ素子16と、を備える。

(もっと読む)

半導体記憶装置

【課題】メモリセルアレイと入出力バッファ間の遅延の最大値を抑制し高速に入出力動作が行える半導体記憶装置を提供する。

【解決手段】複数のメモリセルアレイが配置されたメモリセルアレイ部と、外部入出力回路が配置された周辺回路部と、複数のメモリセルアレイと周辺回路部とを接続する内部バス4と、を備え、周辺回路部は、複数の外部入出力バッファ23と、メモリセルアレイとの間で内部バスを並列に入出力するデータと複数の外部入出力バッファを直列に入出力するデータとを相互に変換する複数のバスインターフェース回路24と、を備え、複数のバスインターフェース回路間の距離d1が、複数の外部入出力バッファ間の距離d2及び内部バスの配線幅の最大値d3より狭くなるように、複数のバスインターフェース回路24は、内部バス4と複数の外部入出力バッファとの間にまとめて配置されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】PRAMの高集積化を行うこと。

【解決手段】第1層間絶縁膜のホールの内壁面を覆うサイドウォール絶縁膜と、ホール内においてサイドウォール絶縁膜を介して埋め込まれたコンタクトプラグと、第1層間絶縁膜上の所定の領域にてコンタクトプラグに接続されるように配された下部電極と、下部電極を含む前記第1層間絶縁膜上を覆う第2層間絶縁膜と、第2層間絶縁膜を貫通し、下部電極の側端面の一部が表れ、かつ、第1層間絶縁膜の所定深さまで形成された開口部と、開口部を含む前記第2層間絶縁膜上の所定の領域に配されるとともに、前記開口部にて前記下部電極の側端面の一部と接続された相変化材料層と、相変化材料層上に配された上部電極と、を備える。

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い半導体装置及び、信頼性の高い半導体装置の作製方法を提供する。また、消費電力が低い半導体装置及び消費電力が低い半導体装置の作製方法を提供する。また、量産性の高い半導体装置及び量産性の高い半導体装置の作製方法を提供する。

【解決手段】酸素欠損を生じることなく酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すればよい。具体的には、酸化物半導体層に酸素を添加した後に加熱処理を施し、不純物を除去して使用すればよい。特に酸素の添加方法としては、高エネルギーの酸素をイオン注入法またはイオンドーピング法などを用いて添加する方法が好ましい。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

半導体装置

【課題】複数の回路ブロックの特性を正確に一致させる。

【解決手段】例えば、端子31A,31Bと、これら端子間に設けられた回路110A,110Bを備える。回路110Aは端子31Aに接続され、端子31Aから端子31Bへ向かって配置されたセル120A,130A,140Aを含む。回路110Bは端子31Bに接続され、端子31Bから端子31Aへ向かって配置されたセル120B,130B,140Bを含む。セル120A,120Bのレイアウトは、形状、サイズ及び向きがトランジスタレベルで同一である。セル130A,130B及びセル140A,140Bのレイアウトは、形状及びサイズが同一であり、トランジスタの向きが180°相違している。これにより各セルを対称配置しつつ、センシティブなセル120A,120Bにおいては電流方向の違いによる特性差が生じない。

(もっと読む)

半導体記憶装置

【課題】3次元型の半導体記憶装置のパフォーマンスを向上させる。

【解決手段】実施形態によれば、半導体記憶装置は、半導体基板と、半導体基板上に設けられ、積層された複数のメモリセルを含む複数のメモリユニットと、カラム方向に配列された複数のメモリユニット上に複数本形成されたビット線とを備え、複数のビット線のロウ方向の配列ピッチは、メモリユニットのロウ方向の配列ピッチよりも小さく、カラム方向に配列された各メモリユニットの端部は、複数本形成されたビット線のいずれか1つに接続される。

(もっと読む)

記憶装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な記憶装置、及び該記憶装置を有する半導体装置を提供する。

【解決手段】第1の入力端子、及び第1の入力端子の入力信号の反転信号が入力される第2の入力端子、並びに第1の信号が出力される第1の出力端子、及び第1の信号の反転信号が出力される第2の出力端子、を有するレベルシフタと、第1の信号が入力される第3の入力端子、及び第1の信号の反転信号が入力される第4の入力端子、並びに第3の出力端子を有する第1のバッファと、第1の信号の反転信号が入力される第5の入力端子、及び第1の信号が入力される第6の入力端子、並びに第4の出力端子を有する第2のバッファと、を有し、第1のバッファの第3の出力端子から出力される信号が、レベルシフタの第1の入力端子に入力され、第2のバッファの第4の出力端子から出力される信号が、レベルシフタの第2の入力端子に入力される。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

半導体記憶装置

【課題】データの読み出し速度を向上する。

【解決手段】半導体記憶装置1は、メモリセルアレー1aと、コラム線1bと、第1および第2のデータ線1d,1eと、データの読み出し時には、コラム線1bに第1および第2のデータ線1d,1eの一方を選択して接続し、データの書き込み時には、コラム線1bに第1および第2のデータ線1d,1eを接続するスイッチ1cと、第1および第2のデータ線1d,1eに接続された読み出し回路1fと、第1および第2のデータ線1d,1eに接続された書き込み回路1gと、を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】誤書込みを抑制した不揮発性半導体記憶装置を提供する。

【解決手段】制御回路は、書込み動作時、複数のビット線中の書込み禁止ビット線の電圧を第1電圧まで上げた後、書込み禁止ビット線をフローティング状態とする。続いて、制御回路は、書込み禁止ビット線以外の書込みビット線の電圧を第2電圧まで上げ、これに伴うカップリングにより書込み禁止ビット線の電圧を上げる。これにより、制御回路は、書込み禁止ビット線に対応するメモリストリング内のメモリトランジスタに対して書込み動作を禁止する。一方、制御回路は、書込みビット線に対応するメモリストリング内のメモリトランジスタに対して書込み動作を実行する。

(もっと読む)

半導体記憶装置

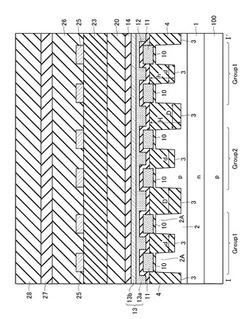

【課題】半導体記憶装置の集積化を図る。

【解決手段】実施形態によれば、半導体記憶装置は、半導体基板と半導体基板上に設けられ、積層された複数のメモリセルを含むメモリセルアレイと、複数のメモリセルと電気的に接続されて平行に配列された複数のビット線と、ビット線接続配線を介してビット線と接続された複数のセンスアンプとを備える。ビット線接続配線は、隣接するN(Nは2以上の整数)本ごとに1つのグループとする。センスアンプは、ビット線接続配線が延びる第1方向にはNよりも小さい数で、且つ前記第1方向と交差する第2方向には前記グループ間のピッチよりも小さいピッチで配列されている。

(もっと読む)

半導体記憶装置

【課題】積層型の半導体記憶装置のパフォーマンスを向上させる。

【解決手段】実施形態によれば、半導体記憶装置は、半導体基板と、半導体基板に対して垂直方向に延び複数のメモリセルを直列接続してなる柱状に形成された複数のメモリユニットを、半導体基板に沿って二次元配列してなるメモリセルアレイと、メモリセルアレイの各メモリユニットの端部に接続される複数のビット線とを備える。複数のメモリユニットは、カラム方向に隣接する前記メモリユニット同士がメモリユニットのロウ方向の配列ピッチ内でロウ方向に変位することにより千鳥状に配列される。

(もっと読む)

記憶装置、及び半導体装置

【課題】プロセスを複雑化させることなく、単位面積あたりの記憶容量を高めることができる記憶装置を提案する。

【解決手段】複数のメモリセルと、複数のワード線と、複数のビット線とを有し、複数のメモリセルは、スイッチング素子と、第1の電極及び第2の電極を有する容量素子と、をそれぞれ有し、複数のメモリセルの少なくとも1つにおいて、複数のワード線のうち一のワード線に与えられる電位に従って、スイッチング素子が複数のビット線のうち一のビット線と第1の電極の接続を制御し、なおかつ、第2の電極が複数のワード線のうち一のワード線とは異なる一のワード線に接続されている記憶装置。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

半導体記憶装置

【課題】記憶素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保しつつ、ユニットセルのレイアウト面積が従来よりも小さい半導体記憶装置を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板と、半導体基板に形成されたアクティブエリアを備える。複数のセルトランジスタがアクティブエリアに形成されている。第1のビット線および第2のビット線は、互いに対をなす。複数のワード線は第1および第2のビット線と交差する。複数の記憶素子の一端がセルトランジスタのソースまたはドレインに電気的に接続され、他端が第1または第2のビット線に接続されている。第1および第2のビット線は、両方とも同一のアクティブエリアに対して記憶素子を介して接続されている。

(もっと読む)

41 - 60 / 769

[ Back to top ]