Fターム[5F083LA03]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | センスアンプ (769)

Fターム[5F083LA03]に分類される特許

21 - 40 / 769

半導体装置

【課題】

実施形態は、解析が簡便な半導体装置を提供する。

【解決手段】

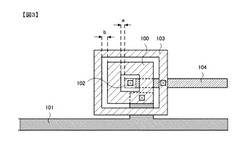

本実施形態の半導体装置は、内部信号を伝送可能な第1配線101と、第1配線101

と電気的に接続された測定電極100と、測定電極100と隣接するように配置され、内

部信号を計測するときに接地電位VSSが印加され、内部信号を計測する以外のときに所

望の電圧が印加されたダミー電極102,103とを備える。

例えば、測定電極100は、環状に形成されており、ダミー電極は、第1電極102と

第2電極103とを有し、第1電極102は、測定電極100の内側に形成された空間に

隣接するように配置され、第2電極103は、測定電極100の外側に隣接するように配

置される。

(もっと読む)

半導体装置

【課題】頻繁なリフレッシュ動作が不要で、正常な読み出しを行うことのできる2トランジスタ型のDRAMを備えた半導体装置を提供する。

【解決手段】本実施形態の半導体装置は、ゲートが第1配線に接続され、第1ソース/ドレインの一方が第2配線に接続された第1トランジスタと、ゲート絶縁膜、ゲート電極、および前記ゲート絶縁膜と前記ゲート電極との間に設けられしきい値を変調するしきい値変調膜を有するゲート構造と、第2ソース/ドレインとを備え、前記ゲート電極が前記第1トランジスタの前記第1ソース/ドレインの他方に接続され、前記第2ソース/ドレインの一方が第3配線に接続され、前記第2ソース/ドレインの他方が第4配線に接続された第2トランジスタと、を備えている。

(もっと読む)

半導体装置

【課題】残渣による配線間のショートの発生を防ぐ。

【解決手段】本発明の半導体装置は、高誘電率材料を含む第1のゲート絶縁膜4と第1のゲート絶縁膜4上に形成された第1のメタルゲート電極5とを備える第1のトランジスタが形成される半導体基板上の第1の領域と、高誘電率材料を含む第2のゲート絶縁膜4と第2のゲート絶縁膜上に形成された第2のメタルゲート電極12とを備え、第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される半導体基板上の第1の領域に並ぶ第2の領域と、電位の異なる第1および第2の配線と、を有し、第1の領域と第2の領域との境界が、第1および第2の配線の少なくとも一方としか重ならない。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ビット当たりの単価を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1方向に沿う第1部分(11a)と第2方向に沿いかつ第1部分と接続された第2部分(11b)とを有し、第2部分において半導体材料を含み、第1方向および第2方向からなる第1平面と交わる方向に沿って離れて並ぶ少なくとも2つの第1配線(11)を含む。可変抵抗膜(15)は、第1配線の第2部分に接続された第1面を有し、相違する抵抗値を示す複数の状態を取り得る。第2配線(12)は、可変抵抗膜の第1面と対向する第2面と接続されている。制御線(13)は、第1平面と交わる方向に沿い、少なくとも2つの第1配線の第2部分の半導体材料を含む部分と絶縁膜を介して接し、第1配線の第2部分の半導体材料を含む部分および絶縁膜とともにトランジスタを構成する。

(もっと読む)

半導体装置

【課題】高集積化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、一方向を長手方向とした第1アクティブエリアと、前記一方向を長手方向とした第2アクティブエリアと、前記第1アクティブエリアにおける前記一方向の一方の端部に形成され、第1導電形である第1ウェルコンタクト層と、前記第1アクティブエリアにおいて前記一方向に沿って断続的に形成され、第2導電形である複数の第1ソース・ドレイン層と、前記第2アクティブエリアにおける前記一方向の一方の端部に形成され、第2導電形である第2ウェルコンタクト層と、前記第2アクティブエリアにおいて前記一方向に沿って断続的に形成され、第1導電形である複数の第2ソース・ドレイン層と、を備える。各前記第1アクティブエリア及び各前記第2アクティブエリアにおける前記一方の端部は、相互に同じ側である。

(もっと読む)

半導体記憶装置及びデータ読み出し方法

【課題】レイアウト面積の増大を抑制することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置1は、2つのメモリセルアレイ10U,10Dと、それら2つのメモリセルアレイ10U,10Dで共有されるセンスアンプ30と、メモリセルアレイ10U,10Dからのデータ読み出しを制御する制御回路50とを有している。メモリセルアレイ10Uは、m本のワード線WL0U〜WLmUと、n本のビット線BL0U〜BL15Uと、これらワード線WL0U〜WLmUとビット線BL0U〜BL15Uの交差点に設けられたメモリセルMCと、ビット線BL0U〜BL15Uとダミーワード線DWLUとの交差点に設けられたダミーセルDMCとを有している。制御回路50は、一方のメモリセルアレイからデータを読み出す場合に、他方のメモリセルアレイのダミーワード線を活性化してダミーセルによりセンスアンプ30のリファレンスレベルを生成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】容量素子が占有する回路面積の増大を抑制する。

【解決手段】メモリストリングは、複数の第1導電層、メモリゲート絶縁層、及び半導体層を有する。複数の第1導電層は、半導体基板に対して実質的に垂直方向に所定ピッチをもって配列され、メモリトランジスタのゲートとして機能する。半導体層は、複数の第1導電層と共にメモリゲート絶縁層を一方の側面で挟み、半導体基板に対して実質的に垂直方向に延び、メモリトランジスタのボディとして機能する。第1キャパシタは、複数の第2導電層を有する。複数の第2導電層は、半導体基板に対して実質的に垂直方向に所定ピッチをもって配列され、第1キャパシタの電極として機能する。制御回路は、複数の第1導電層に印加される電圧に応じて、複数の第2導電層の各々に印加する電圧を制御し、これにより第1キャパシタの容量を変化させる。

(もっと読む)

半導体装置

【課題】オン電流が少ないトランジスタを含むメモリセルと積層方向に延びるビット線により、低い製造コストで高速動作を実現可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、例えば、記憶素子とその読み出し電流経路に挿入される第1のトランジスタとを含むメモリセルMCと、このメモリセルMCの一端に直接接続され、記憶素子の情報を伝送する第1のビット線LBLと、第2のトランジスタを含み第1のビット線LBLを介して伝送される記憶素子の情報を増幅する第1のアンプLSAとを備えている。第1のアンプLSAは基板L0に形成され、メモリセルMCは基板L0の上部の第1の層L1〜L8に形成され、第1のビット線LBLは積層方向に延びる配線構造を含んで形成される。第1のトランジスタのチャネル中のキャリアの移動度は、第2のトランジスタのチャネル中のキャリアの移動度よりも低い。

(もっと読む)

半導体記憶装置

【課題】比較的小振幅な信号が伝送される第1の信号線対で発生するカップリングノイズを低減しつつ、該第1の信号線対と直交する方向に異なる配線層で配置される、第1の信号線対よりも振幅が大きい信号が伝送される第2の信号線毎の信号遅延量の差異を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、メモリアレイ上で配線される第1の振幅信号が伝送される複数の第1の信号線対と、該第1の信号線対と直交する方向に異なる配線層で配置される複数の第2の信号線とを有する。第1の信号線対は、メモリマットの列毎に配置され、メモリマットの列方向において、それぞれ所定の一定間隔で交差される。また、第1の信号線対の交差部位は第2の信号線の配線方向におけるメモリマットの列毎にずらして配置される。

(もっと読む)

半導体メモリ

【課題】素子間リークを低減できる半導体メモリを提供する。

【解決手段】本実施形態の半導体装置は、第1のゲート絶縁膜上の電荷蓄積層と、第1の絶縁体を介して電荷蓄積層上に設けられる制御ゲート電極とを含むメモリセルと、アクティブ領域AAH上の第2のゲート絶縁膜20Hと、第2のゲート絶縁膜上の第1の電極層21Hと、を含むトランジスタHTと、素子分離絶縁膜15H上に設けられるシールドゲート電極SIGと、を有する。シールドゲート電極SIGの底部は、素子分離絶縁膜15Hの最も高い上面より半導体基板10の底部側に位置している。

(もっと読む)

半導体記憶装置

【課題】4個のトランジスタと2個のMTJ素子からなり、電源を印加しないでも不揮発性メモリとして動作するSRAMからなる半導体記憶装置を提供する。

【解決手段】第1及び第2のインバータ2,4と第1及び第2の転送用MOSFET3,5とを含むメモリセル1からなるSRAMにおいて、第1及び第2のインバータ2,4はスピン注入型のMTJ素子6,8と駆動用MOSFET7,9とからなり、これらのインバータ2,4からフリップフロップ回路が構成され、第1及び第2のインバータ2,4の出力端子は、それぞれ第1及び第2の転送用MOSFET3,5を介してビットライン及びビットラインバーに接続され、第1及び第2の転送用MOSFET3,5のゲートは、同一のワードラインに接続される。従来のSRAMに比較してメモリセルの面積が小さく、高速で低消費電力の不揮発性メモリが得られる。

(もっと読む)

半導体メモリ及びその製造方法

【課題】素子分離絶縁膜の応力に起因する素子特性の劣化を低減する。

【解決手段】本実施形態の半導体メモリは、第1のゲート絶縁膜上の電荷蓄積層と電荷蓄積層上に積層される制御ゲート電極とを含む第1のアクティブ領域AA内のメモリセルMCと、第2のゲート絶縁膜20L上の第1の電極層21Lと、を含む、第2のアクティブ領域AAL内の第1のトランジスタLTとを具備する。第2のアクティブ領域AALを定義する第2の素子分離絶縁膜19Xは、第1の膜190と、第1の膜190と第2のアクティブ領域AALとの間の第2の膜195とを含み、第1の膜190の上面は、第2の膜195の上面よりも、半導体基板10の底部側に位置している。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

抵抗変化型不揮発性記憶素子の書き込み方法および抵抗変化型不揮発性記憶装置

【課題】書き込み動作の安定性および信頼性を向上した抵抗変化型不揮発性記憶素子の書き込み方法を提供する。

【解決手段】抵抗変化素子を含むメモリセルに対して電圧パルスを印加することにより、抵抗変化素子を、印加される電圧パルスの極性によって第1の抵抗状態と第2の抵抗状態とを可逆的に変化させる書き込み方法であって、抵抗変化素子を第2の抵抗状態から第1の抵抗状態に変化せしめる時に、抵抗変化素子に対して、第2の電圧パルス(VL)よりも電圧の絶対値が小さく、かつ、第1の電圧パルス(VH)と極性が異なる第1の抵抗化プレ電圧パルス(VLpr)を印加する第1ステップと、その後、第1の電圧パルス(VH)を印加する第2ステップとを含む第1の抵抗状態化ステップを含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】円筒型MONOSメモリセルで電荷保持特性の向上を図る。

【解決手段】不揮発性半導体記憶装置は、半導体基板と、前記半導体基板上に形成され、上面から下面まで達する円筒状の貫通ホールを有するコントロールゲートCGと、前記貫通ホール内における前記コントロールゲートの側面上に形成されたブロック絶縁膜150と、前記貫通ホール内における前記ブロック絶縁膜の側面上に形成された電荷蓄積膜151と、前記貫通ホール内における前記電荷蓄積膜の側面上に形成されたトンネル絶縁膜152と、前記貫通ホール内における前記トンネル絶縁膜の側面上に形成された半導体層SPと、を具備し、前記トンネル絶縁膜は、SiO2を母材とし、添加することで前記母材のバンドギャップを低下させる元素を含む第1絶縁膜を含み、前記元素の濃度および濃度勾配は、前記半導体層側から前記電荷蓄積膜側に向かって単調に増加する。

(もっと読む)

抵抗変化型メモリデバイスおよびその駆動方法

【課題】リファレンスセルの抵抗状態に応じて、読み出し電流を設定する構成で、誤書き込みによる抵抗の変化が発生することなく、より信頼性の高いリファレンス電流を得ることが可能な抵抗変化型メモリデバイスおよびその駆動方法を提供する。

【解決手段】素子両端に極性の異なる信号を印加することで可逆的に記憶素子の抵抗値が変化するメインメモリセルを含むメモリアレイ部と、素子両端に極性の異なる信号を印加することで可逆的に抵抗値が変化する記憶素子を含み、メインメモリセルのデータを識別するために必要な参照電流を発生させるリファレンスセルを含むリファレンスセル部と、を有し、リファレンスセルの抵抗状態に応じた参照電流の印加電流の向きが設定されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】高い信頼性を有し且つ安価な不揮発性半導体記憶装置を提供する。

【解決手段】この不揮発性半導体記憶装置において、メモリストリングスは、基板に対して垂直方向に延びる一対の柱状部、及び前記一対の柱状部の下部を連結させるように形成された連結部を有する半導体層と、前記柱状部の側面を取り囲むように形成された電荷蓄積層と、前記柱状部の側面及び前記電荷蓄積層を含む第1の絶縁膜と、前記柱状部の側面及び前記第1の絶縁膜を覆うように形成された第1導電層と、前記連結部の周囲に形成される第2の絶縁膜と、前記連結部に前記ゲート絶縁膜を介して形成される第2導電層とを備える。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

半導体装置

【課題】トランジスタのしきい値電圧のばらつきの影響を緩和し、複数の状態(例えば3以上の状態)の区別を正確、かつ容易にした半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、ワード線と、ビット線とワード線に接続されたメモリセルと、入力されたアドレス信号によって指定されたメモリセルを選択するように、複数の第2信号線及び複数のワード線を駆動する、第2信号線およびワード線の駆動回路と、書き込み電位を第1信号線に出力する、書き込み回路と、指定されたメモリセルに接続されたビット線から入力されるビット線の電位と、複数の読み出し電位とを比較する読み出し回路と、ビット線の電位と複数の読み出し電位の比較結果に基づいて複数の補正電圧のいずれかを選択する制御回路と、書き込み電位及び複数の読み出し電位を生成して、書き込み回路及び読み出し回路に供給する、電位生成回路と、を有する半導体装置。

(もっと読む)

不揮発性メモリセルおよび不揮発性メモリ

【課題】 スタティックノイズマージンを損なうことなく、揮発性記憶部および不揮発性記憶部間のストアとリコールを行える不揮発性メモリセルを提供する。

【解決手段】 不揮発性記憶部12は、揮発性記憶部11のノードV1とバイアス供給ノードNSとの間に直列に介挿されたNチャネルトランジスタTw1および抵抗変化型素子R1と、揮発性記憶部11のノードV2とバイアス供給ノードNSとの間に直列に介挿されたNチャネルトランジスタTw2および抵抗変化型素子R2を有する。ストア時、NチャネルトランジスタTw1およびTw2はONとされ、抵抗変化型素子R1およびR2は、ノードV1(V2)からバイアス供給ノードNSに向かう電流を通過させたときに高抵抗となり、逆方向の電流を通過させたときに低抵抗となる。リコール時は、揮発性記憶部11のフリップフロップに対する電源電圧を立ち上げる。

(もっと読む)

21 - 40 / 769

[ Back to top ]