Fターム[5F083LA21]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | コンタクトの配置レイアウト (1,397)

Fターム[5F083LA21]に分類される特許

201 - 220 / 1,397

半導体集積回路

【課題】電荷転送効率が高い転送トランジスタを備える半導体集積回路を提供することを目的とする。

【解決手段】実施形態に係る半導体集積回路は、ゲート電極を有し、当該ゲート電極及び一の拡散層が第1配線でダイオード接続された転送トランジスタと、クロック信号が供給されるクロック信号線とを備え、前記クロック信号線の一部である第1部分クロック信号線の少なくとも一部が前記ゲート電極上に形成されていることを特徴とする。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、容量素子と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、信号線及びワード線に接続された第2のトランジスタと、ワード線、に接続された容量素子とを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方とが接続された、半導体装置。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果を抑制しつつ微細化を達成した半導体装置およびその作製方法を提供することを目的の一とする。

【解決手段】絶縁層にトレンチを形成し、トレンチの上端コーナー部と接する酸化物半導体膜に不純物を添加し、ソース領域およびドレイン領域を形成する。上記構造にすることで微細化することが可能である。また、トレンチを有することで、ソース電極層とドレイン電極層との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果を抑制することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】オフ電流を増加させることなく電源供給配線の電気抵抗を下降させることが可能な、TFTを有する半導体装置を提供することである。

【解決手段】表面を有する絶縁膜II4と、絶縁膜II4の表面上に形成され、かつチャネル領域TP2と、チャネル領域TP2を挟む1対のソース/ドレイン領域TP1,TP4とを含む半導体層と、ソース領域TP1に電源を供給するための電源供給配線TP1とを備えている。上記絶縁膜II4の表面には凹部TRが形成されている。上記電源供給配線TP1は、半導体層と同一の層から形成された層を含み、かつ絶縁膜II4の表面上に形成された第1の部分TP1Aと、凹部内に形成された第2の部分TP1Bとを有している。上記第2の部分TP1Bの底面全体が絶縁体II4で覆われている。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極用溝18の底部18cから活性領域の一部が突き出すように形成されたフィン部15と、ゲート電極用溝18及びフィン部15の表面を覆うゲート絶縁膜21と、ゲート電極用溝18の下部に埋め込まれ、ゲート絶縁膜21を介してフィン部15を跨ぐように形成されたゲート電極22と、第1の不純物拡散領域28と、第2の不純物拡散領域29と、フィン部15の表面に設けられた準位形成領域30と、を備える半導体装置10を選択する。

(もっと読む)

ルチル結晶構造を備えた酸化チタン膜の製造方法

【課題】高温のアニールを必要とせずに、誘電率の高いルチル結晶構造の酸化チタン膜を形成する。

【解決手段】非晶質の酸化ジルコニウム膜上に、チタンプリカーサとしてメチルシクロペンタジエニルトリスジメチルアミノチタンを用いてALD法により非晶質の酸化チタン膜を形成し、300℃以上の温度でアニールして結晶化することでルチル結晶構造を有する酸化チタン膜が得られる。

(もっと読む)

半導体デバイスの製造方法

【課題】チャネル領域となる領域の直下だけに熱拡散によってビット線となる拡散層を形成することができる半導体デバイスの製造方法を提供する。

【解決手段】半導体基板の法線方向に複数の半導体ピラーを形成する工程、前記半導体ピラーで挟まれた溝の側面を覆うように絶縁膜を形成する工程、前記溝の内部全体を覆うように第1のポリシリコン膜を形成する工程、前記第1のポリシリコン膜上に前記半導体基板内へ拡散させる不純物で構成された不純物層を形成する工程、前記不純物層上に第2のポリシリコン膜を形成する工程、前記第2のポリシリコン膜上に前記不純物の外方拡散を防止する第1の拡散防止膜を形成する工程を経た後、前記不純物を前記溝の底部において前記半導体ピラー内に熱拡散させてビット線となる拡散層を形成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 メモリセルにおける絶縁特性が向上する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】 実施形態に係る不揮発性半導体記憶装置は、半導体領域を持つ。前記半導体領域の表面には金属元素を含む界面領域が設けられる。前記界面領域の表面にはトンネル絶縁膜が設けられる。前記トンネル絶縁膜の表面には電荷蓄積絶縁膜が設けられる。前記電荷蓄積絶縁膜の表面にはブロック絶縁膜が設けられる。前記ブロック絶縁膜の表面には制御ゲート電極が設けられる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】微細化による信頼性低下が小さい半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、半導体基板上に浮遊ゲートと制御ゲートを有する複数の電気的書き換え可能な不揮発性メモリセルを備えたNANDセルユニットを有する。NANDセルユニットは、不揮発性メモリセルの互いのソース領域及びドレイン領域を共有し、不揮発性メモリセルが直列接続されている。不揮発性メモリセルのソース領域及びドレイン領域は、シリサイドを用いて形成される。

(もっと読む)

半導体装置

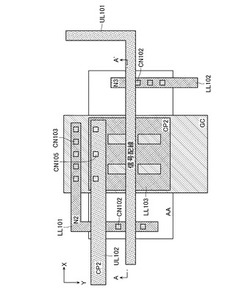

【課題】SRAMのメモリセルにおける配線を確実に形成することがきて、電気的な接続が良好に行われる半導体装置を提供する。

【解決手段】半導体装置におけるSRAMのメモリセルでは、アクセストランジスタT1のゲート配線部GHA1に電気的に接続されるコンタクトプラグCPS1に対して、ワード線としての第3配線M32に電気的に接続されることになるヴィアVS1が直接接続されている。また、アクセストランジスタT2のゲート配線部GHA2に電気的に接続されるコンタクトプラグCPS2に対して、ワード線としての第3配線M32に電気的に接続されることになるヴィアVS2が直接接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリおよび容量素子を有する半導体装置の性能を向上させる。

【解決手段】同一の半導体基板1上に、不揮発性メモリのメモリセルMCと容量素子とが形成されている。メモリセルMCは、半導体基板の上部に絶縁膜3を介して形成された制御ゲート電極CGと、半導体基板1の上部に形成されて制御ゲート電極CGと隣合うメモリゲート電極MGと、メモリゲート電極MGと半導体基板1との間および制御ゲート電極CGとメモリゲート電極MGとの間に形成されて内部に電荷蓄積部を有する絶縁膜5とを有している。容量素子は、制御ゲート電極CGと同層のシリコン膜で形成された下部電極と、絶縁膜5と同層の絶縁膜で形成された容量絶縁膜と、メモリゲート電極MGと同層のシリコン膜で形成された上部電極とを有している。そして、上部電極の不純物濃度は、メモリゲート電極MGの不純物濃度よりも高くなっている。

(もっと読む)

不揮発性記憶素子及びその製造方法並びに不揮発性記憶装置

【課題】不揮発性記憶素子の初期化電圧のばらつきの発生を抑えつつ、従来に比べて初期化電圧の低減を図ることができる抵抗変化型の不揮発性記憶素子を提供する。

【解決手段】第1の層間絶縁層102、下部電極105、上部電極107及び抵抗変化領域106を備え、抵抗変化領域106は積層された第1の抵抗変化領域106bと第2の抵抗変化領域106aを有し、第1の抵抗変化領域106bは第1の遷移金属酸化物で構成され、第2の抵抗変化領域106aは第2の遷移金属酸化物で構成され、第2の遷移金属酸化物の酸素不足度は第1の遷移金属酸化物の酸素不足度より小さく、抵抗変化領域106の上面は上部電極107と接し、抵抗変化領域106の底面は下部電極105及び第1の層間絶縁層102と接し、抵抗変化領域106の底面と下部電極105の接する面の面積は抵抗変化領域106の上面と上部電極107の接する面の面積より小さい。

(もっと読む)

半導体装置

【課題】半導体集積回路の微細化に伴い非常に短くなったゲート長を有するトランジスタにおいて、ゲート絶縁膜におけるリーク電流の発生を抑制し、トランジスタとしての機能を高めることが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面に形成された1対のソース/ドレイン領域と、1対のソース/ドレイン領域に挟まれる領域上であって、主表面に接するように形成されたゲート絶縁膜AFEと、ゲート絶縁膜AFEの上面に接するように形成されたゲート電極POとを備える。上記1対のソース/ドレイン領域の一方から他方へ向かう方向のゲート電極POの長さは45nm未満である。ゲート絶縁膜AFEは反強誘電体膜を有する。

(もっと読む)

半導体不揮発性記憶装置およびその製造方法

【課題】高い信頼性で書き込み・消去・読み出しが可能な低コストの半導体不揮発性記憶装置およびその製造方法を提供する。

【解決手段】実施形態の半導体不揮発性記憶装置は、基体Sと、第1の電極2と、機能膜10と、第2の電極50と、を持つ。前記第1の電極2は、前記基体S上に設けられる。前記機能膜10は、前記第1の電極2上に成膜されて記憶媒体をなす。前記第2の電極50は、上面に凸の曲面を有するように、前記機能膜10上または前記機能膜10内に設けられる。

(もっと読む)

ダイオードストラッピングを備えた熱アシストフラッシュメモリ

【課題】フラッシュメモリの動作速度及び耐久性を向上させる技術の提供。

【解決手段】メモリが、行及び列を含むメモリセルのアレイを有している。該メモリは、アレイ内の単数又は複数のワード線上の第1の離隔位置のセットに第1のバイアス電圧を印加するとともに、単数又は複数のワード線上の第2の離隔位置のセットに第1のバイアス電圧とは異なる第2のバイアス電圧を印加する、ワード線に結合された回路部を有し、第1の離隔位置のセットにおける位置は、第2の離隔位置のセットの位置の間に介在しており、それにより、第1の離隔位置のセットにおける位置と第2の離隔位置のセットにおける位置との間に、単数又は複数のワード線の加熱をもたらす電流の流れが誘導される。

(もっと読む)

パターン形成方法

【課題】微細なパターンと比較的サイズが大きめのパターンとを有するパターン形成方法で、サイズが大きめのパターンを従来に比して精度良く形成することができるパターン形成方法を提供する。

【解決手段】実施形態によれば、加工対象上の芯材膜31に開口を形成した後、マスク膜32をコンフォーマルに形成する。マスク膜32をエッチバックして芯材膜31の側面に第1の幅のマスク膜32を残す。開口の形成領域以外の領域にレジストパターン35aを形成し、これをマスクに芯材膜31をエッチングする。さらに、芯材膜31をスリミングして第1の幅より小さい第2の幅のラインアンドスペース状のパターンを形成する。側壁膜をコンフォーマルに形成した後、エッチバックし、さらに芯材膜31を除去して、加工対象上に側壁膜からなる側壁パターンを形成する。そして側壁パターンで加工対象をエッチングする。

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供すること。また、安定した電気的特性が付与された、信頼性の高い半導体装置を提供すること。

【解決手段】絶縁層に凸状構造体を形成し、該凸状構造体に接して酸化物半導体層のチャネル形成領域を設けることで、チャネル形成領域を3次元方向(基板垂直方向)に延長させる。これによって、トランジスタの微細化を達成しつつ、実効的なチャネル長を延長させることができる。また、凸状構造体の上面と側面とが交わる上端コーナー部に曲面を形成し、酸化物半導体層が当該曲面に垂直なc軸を有する結晶を含むように形成する。これによって、酸化物半導体層の可視光や紫外光の照射による電気的特性の変化を抑制することができる。

(もっと読む)

半導体装置

【課題】微細化が可能であるメモリセル構造を備える半導体装置を提供する。

【解決手段】ワード線と、ビット線と、電源ノードと、ビット線と電源ノードとの間にPN結合を成す第1及び第2の領域並びに第2の領域とPN結合を成す第3の領域を少なくとも有するメモリ素子と、メモリ素子の第2の領域とは独立して設けられてメモリ素子の第2の領域と電気的に接続された第1の電極及び前記ワード線に接続された第2の電極を有するキャパシタと、を備える。

(もっと読む)

半導体装置

【課題】不揮発性であって、作製が簡単であり、追記が可能な記憶回路を有する半導体装置の提供を課題とする。

【解決手段】本発明の半導体装置は、複数のトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記複数のトランジスタのうちの1つの上に設けられた記憶素子及びアンテナとして機能する導電層とを有し、前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、アンテナとして機能する前記導電層と前記複数のトランジスタのソース配線又はドレイン配線として機能する導電層とは、同じ層上に設けられていることを特徴とする。

(もっと読む)

半導体装置

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置において、安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタ(半導体装置)において、酸化物半導体膜を、絶縁層に設けられたトレンチ(溝)に設ける。トレンチは曲率半径が20nm以上60nm以下の曲面状の下端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも下端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

201 - 220 / 1,397

[ Back to top ]