Fターム[5F083LA21]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | コンタクトの配置レイアウト (1,397)

Fターム[5F083LA21]に分類される特許

161 - 180 / 1,397

相変化メモリセル及びそれを利用した相変化メモリデバイス

【課題】本発明は、相変化メモリセル及びそれを利用した相変化メモリデバイスに関するものである。

【解決手段】本発明の相変化メモリセルは、書き込み回路及び読み出し回路を含む。前記書き込み回路は、第一電極と、カーボンナノチューブ構造体と、第二電極と、を含む。前記第一電極、前記カーボンナノチューブ構造体及び前記第二電極は、相互に直列接続される。前記書き込み回路は、相変化メモリセルにデータを書き込む。前記読み出し回路は、第三電極と、相変化層と、第四電極と、を含む。前記第三電極、前記相変化層及び前記第四電極は、相互に直列接続される。少なくとも一部の前記相変化層及び少なくとも一部の前記カーボンナノチューブ構造体は、相互に積層して設置される。前記読み出し回路は、前記相変化メモリセルからデータを読み出す。

(もっと読む)

半導体装置の駆動方法

【課題】半導体装置の駆動方法を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用のトランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態として、書き込み用トランジスタのソース電極と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態として、ノードに所定量の電位を保持させることで行う。メモリセルの読み出しは、ビット線にプリチャージ電位を供給した後ビット線への電位の供給を止め、ビット線の電位がプリチャージ電位に保たれるか、または電位が下がるか、により行う。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

SRAM装置

【課題】低消費電力でより安定して動作することが可能なSRAM装置を提供する。

【解決手段】SRAM装置100は、非反転出力端子Qおよび反転出力端子/Qを有するフリップフロップ回路FFを備える。非反転出力端子と第1のビット線bitとの間に、非反転出力端子側から第1のビット線側への方向に電流が流れる第1のトンネルトランジスタT1を備える。非反転出力端子と第1のビット線との間で、第1のビット線側から非反転出力端子側への方向に電流が流れる第2のトンネルトランジスタT2を備える。反転出力端子と第2のビット線bitbとの間に、反転出力端子側から第2のビット線側への方向に電流が流れる第3のトンネルトランジスタt3を備える。反転出力端子と第2のビット線との間で、第2のビット線側から反転出力端子側への方向に電流が流れる第4のトンネルトランジスタt4を備える。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】STIの形成によるウェル拡散層の不純物濃度の変化を抑制し、かつ、ウェル拡散層のドーズロスを抑制した半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。メモリセル領域には、複数のメモリセルが半導体基板上に形成されている。周辺回路領域には、複数のメモリ素子を制御する複数の半導体素子が形成されている。素子分離領域は、複数のメモリセル間を分離し、あるいは、複数の半導体素子間を分離する。周辺回路領域において半導体素子が形成されているアクティブエリアの不純物濃度は、半導体基板の表面に対して水平方向に素子分離領域の側面からアクティブエリアの内部へ向かって低下している。

(もっと読む)

半導体装置

【課題】貫通電極を用いた積層型の半導体装置において不良のある信号経路を救済する。

【解決手段】インターフェースチップIFと、互いに積層されたコアチップCC0〜CC7と、コアチップCC0〜CC7を貫通する複数の貫通電極TSV3により構成され、コアチップCC0〜CC7をインターフェースチップIFにそれぞれ個別に接続する複数の第1の信号経路と、コアチップCC0〜CC7を貫通する複数の貫通電極TSV1により構成され、コアチップCC0〜CC7をインターフェースチップIFに共通接続する第2の信号経路と、複数の第1の信号経路のいずれかを第2の信号経路に置換する切り替え回路110とを備える。本発明によれば、貫通電極の全てに切り替え回路を設ける必要がなくなる。また、救済のために追加する貫通電極の数も最小限に抑えられることから、チップ面積の増大を抑制することも可能となる。

(もっと読む)

半導体記憶装置

【課題】低電圧化を可能にする。

【解決手段】実施形態は、第1の配線と、その上に積層されたメモリセルと、その上に第1の配線と交差するように形成された第2の配線とを有するセルアレイ層を備え、メモリセルが極性の異なる電気信号が印加されることにより電気的書き換えが可能な可変抵抗素子及び可変抵抗素子に双方向の電流を流す電流制御素子を直列に接続してなる。電流制御素子は、i型半導体とその両側に接する第1及び第2導電型半導体とを有する。第2導電型半導体中の第2の不純物の拡散長は第1導電型半導体中の第1の不純物の拡散長より長く、第1導電型半導体とi型半導体との接合部に、第2導電型半導体とi型半導体との接合部よりも多くのインパクトイオンを発生させるインパクトイオン化促進部が形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】大量データを高速に一括で保存することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】ビット線BL0〜BL3とワード線WL0〜WL3との間に接続され、低抵抗状態から高抵抗状態へ遷移するリセット動作と、リセット動作と異なる極性の電圧を印加することにより高抵抗状態から低抵抗状態へ遷移するセット動作が行われ、リセット動作時に流れるリセット電流がセット動作時に流れるセット電流よりも1桁以上低い可変抵抗素子VRを含むメモリセルMCを複数備えたメモリセルアレイを有する。さらに、メモリセルMCに対してリセット動作及びセット動作を行い、リセット動作を低抵抗状態である第1の複数のメモリセルのうち、選択の第1の配線に接続され、かつ選択の第2の配線に接続される第2の複数のメモリセルに対して一括して行う制御回路を有する。

(もっと読む)

半導体記憶装置

【課題】積層型の半導体記憶装置のパフォーマンスを向上させる。

【解決手段】実施形態によれば、半導体記憶装置は、半導体基板と、半導体基板に対して垂直方向に延び複数のメモリセルを直列接続してなる柱状に形成された複数のメモリユニットを、半導体基板に沿って二次元配列してなるメモリセルアレイと、メモリセルアレイの各メモリユニットの端部に接続される複数のビット線とを備える。複数のメモリユニットは、カラム方向に隣接する前記メモリユニット同士がメモリユニットのロウ方向の配列ピッチ内でロウ方向に変位することにより千鳥状に配列される。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置の集積化を図る。

【解決手段】実施形態によれば、半導体記憶装置は、半導体基板と半導体基板上に設けられ、積層された複数のメモリセルを含むメモリセルアレイと、複数のメモリセルと電気的に接続されて平行に配列された複数のビット線と、ビット線接続配線を介してビット線と接続された複数のセンスアンプとを備える。ビット線接続配線は、隣接するN(Nは2以上の整数)本ごとに1つのグループとする。センスアンプは、ビット線接続配線が延びる第1方向にはNよりも小さい数で、且つ前記第1方向と交差する第2方向には前記グループ間のピッチよりも小さいピッチで配列されている。

(もっと読む)

セルの配置構造、半導体集積回路、及び回路素子セルの配置方法

【課題】セルベース設計において複数の記憶素子セルが配置される構成において、効率的に且つ確実に複数ビットのソフトエラーの発生を抑制することが可能なセルの配置構造を提供する。

【解決手段】回路素子セルの配置構造は、第1の方向に延展するセル配置列上に並べられた複数の記憶素子セルと、複数の記憶素子セルの各々の領域において第1の方向に垂直な第2の方向に並べられた第1のNウェル及び第1のPウェルと、複数の記憶素子セルのうち少なくとも2つの互いに隣接する記憶素子セルの間に設けられ、セル配置列の幅に亘る長さを各々が有する第2のNウェル及び第2のPウェルとを含み、第1のNウェルと第2のNウェルとは一体であり、第1のPウェルと第2のPウェルとは一体である。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】微細化によっても順方向電流が減少することが無いようにする。

【解決手段】実施形態は、第1の配線と、その上に積層されたメモリセルと、その上に形成された第2の配線とを有するセルアレイ層を備え、メモリセルが、電流制御素子、可変抵抗素子及びこれらの間に配置されたシリサイド用金属層を有する。第1の配線又は第1の配線層を形成し、その上に電流制御素子を形成する半導体層、シリサイド用金属層及び可変抵抗素子を形成する可変抵抗素子層を順次形成する。可変抵抗素子層及びシリサイド用金属層を半導体層に達するまで第1のエッチングにより選択的に除去し、少なくとも露出したシリサイド用金属層の側面を覆うように第1の保護層を形成し、選択的に除去した部分に対応する半導体層の部分を第2のエッチングにより選択的に除去し、可変抵抗素子、シリサイド用金属層及び半導体層を覆うように第2の保護層を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性半導体装置の高集積化を図ることのできる技術を提供する。

【解決手段】スイッチ用nMIS(Qs)のスイッチゲート電極SGと、スイッチ用nMIS(Qs)にワード線に対して交差する方向に沿って隣接するメモリ用nMIS(Qm)のメモリゲート電極MGとの間に、スイッチ用nMIS(Qs)のソース/ドレイン領域SDHとして機能し、同時にメモリ用nMIS(Qm)のドレイン領域Dとして機能する半導体領域を形成し、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)側のソース/ドレイン領域SDHを構成する半導体領域の形状と、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)と反対側(ビット線側)のソース/ドレイン領域SDLを構成する半導体領域の形状とを非対称とする。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去動作の実行単位を小さくすると共に正確な読出動作を実現可能な不揮発性半導体記憶装置を提供する。

【解決手段】一態様に係る不揮発性半導体記憶装置は、複数のメモリストリング、複数のメモリブロック、複数のソース線、及び制御回路を有する。複数のメモリストリングは、積層された複数のメモリトランジスタを含む。複数のメモリブロックは、複数のメモリストリングを含む。複数のソース線は、複数のメモリストリングそれぞれに接続される。制御回路は、複数のソース線に供給する信号を制御する。複数のメモリストリングは、各々、半導体層、電荷蓄積層、及び導電層を有する。制御回路は、メモリトランジスタに対する動作の種類に基づいて、複数のソース線を電気的に共通接続するか否かを切り替える。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】記憶回路におけるデータの保持期間を長くする。また、消費電力を低減する。また、回路面積を小さくする。また、1回のデータの書き込みに対する該データの読み出し可能回数を増やす。

【解決手段】記憶回路を具備し、記憶回路は、ソース及びドレインの一方にデータ信号が入力される第1の電界効果トランジスタと、ゲートが第1の電界効果トランジスタのソース及びドレインの他方に電気的に接続される第2の電界効果トランジスタと、ソース及びドレインの一方が第2の電界効果トランジスタのソース又はドレインに電気的に接続される第3の電界効果トランジスタと、を備える。

(もっと読む)

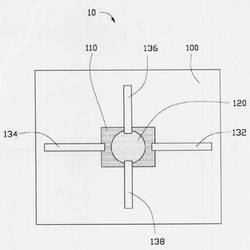

相変化メモリ及び相変化メモリの製造方法

【課題】信頼性の高い相変化メモリを低コストで提供する。

【解決手段】基板上に形成された絶縁膜と、前記絶縁膜内に設けられた一方の極の電極層及び他方の極の電極層と、前記絶縁膜の上部に設けられた底部が略正方形または略長方形の形状となる開口部と、前記開口部の底部の各々の辺に沿って前記基板面と略平行な面に形成された相変化部と、前記開口部の底部の4隅のうち、対向する2つの隅において前記相変化部と各々接続される一方の極の接続電極と、他の対向する2つの隅において前記相変化部と各々接続される他方の極の接続電極と、を有し、前記一方の極の接続電極は、前記一方の極の電極層と接続されているダイオード部と前記相変化部とを各々接続するものであって、前記他方の極の接続電極は、前記相変化部と前記他方の極の電極層とを各々接続するものであることを特徴とする相変化メモリを提供することにより上記課題を解決する。

(もっと読む)

半導体装置及びその駆動方法

【課題】信号処理回路に対する電源電圧の供給及び遮断を選択することができるスイッチとして機能する回路(電源供給制御回路)として好ましい回路を提供する。

【解決手段】信号処理回路に対する電源電位の供給を担う第1の配線と、電源電位を供給する第2の配線との電気的な接続を制御するトランジスタ、及び、信号処理回路に対する電源電位の供給を担う第1の配線を接地させるか否かを制御するトランジスタとを設け、当該2つのトランジスタの少なくとも一方として、チャネルが酸化物半導体層に形成されるトランジスタを適用する。これにより、2つのトランジスタの少なくとも一のカットオフ電流に起因する消費電力を低減することが可能となる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

メモリセル

【課題】拡散層等のバルクが固定であってメタル層、コンタクト層の少なくとも何れか1層を変更して複数の仕様に対応可能なメモリセルを提供すること。

【解決手段】メモリユニットが列方向に沿って鏡面対称に行方向に沿って並置されて、2行2列に配置されメモリセルを構成する。メモリユニットは、行方向に沿って並置され列方向に伸長される第1〜第4拡散層を備え一対の記憶ノードが構成される。第1および第2ワード線は第1〜第4拡散層の両端部外方に配置される。第1及び第2ワード線の間に行方向に沿って第1のメタル配線領域が確保され、第1メタル層が配線可能とされる。列方向に隣接配置されるメモリユニットの境界領域でありは第3、第4拡散層が配置される列方向の位置には列方向に沿って第2のメタル配線領域が確保され、第2メタル層が配線可能とされる。

(もっと読む)

半導体記憶装置およびその作製方法

【課題】電力の供給がない状況でもデータの保持が可能、かつ書き込み回数にも制限がない、新たな構造の半導体記憶装置を提供する。また、単位面積あたりの記憶容量を増加させる。

【解決手段】一対の電極と、一対の電極の側壁と接して設けられた絶縁膜と、該絶縁膜を介して一対の電極間に設けられ、一対の電極の上面の高さよりも上面の高さの低い第1のゲート電極と、第1のゲート電極上に設けられた第1のゲート絶縁膜と、第1のゲート絶縁膜および一対の電極と接して設けられた酸化物半導体膜と、少なくとも酸化物半導体膜上に設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜上に設けられた第2のゲート電極と、を有する第1のトランジスタと、一対の電極の一方を介して第1のトランジスタと接続されるキャパシタと、を有し、該キャパシタに保持される電位に応じてデータが記憶されるメモリセルからなる半導体記憶装置である。

(もっと読む)

161 - 180 / 1,397

[ Back to top ]