Fターム[5F083MA19]の内容

Fターム[5F083MA19]の下位に属するFターム

拡散層とビット線 (1,521)

Fターム[5F083MA19]に分類される特許

121 - 140 / 2,373

半導体記憶装置およびその製造方法

【課題】微細化されても、MTJ素子がコンタクトプラグ内のシームまたはボイドの影響を受けることなく、MTJ素子の特性の劣化を抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。複数のセルトランジスタは、半導体基板上に設けられている。コンタクトプラグは、隣接するセルトランジスタ間に埋め込まれ、該隣接するセルトランジスタ間にある拡散層に電気的に接続されている。層間絶縁膜は、複数のコンタクトプラグ間を埋め込む。記憶素子は、コンタクトプラグの上方に設けられておらず、層間絶縁膜の上方に設けられている。側壁膜は、記憶素子の側面の少なくとも一部を被覆し、半導体基板の表面上方から見たときに、コンタクトプラグに重複するように設けられている。下部電極は、記憶素子の底面と層間絶縁膜との間、および、側壁膜とコンタクトプラグとの間に設けられ、記憶素子とコンタクトプラグとを電気的に接続する。

(もっと読む)

記憶装置及び半導体装置

【課題】消費電力を抑えることができる記憶装置を提供する。

【解決手段】第1クロック信号に従って、データを含む信号の電位の極性を反転させることで、出力電位を生成する第1論理素子と、第1論理素子が生成する出力電位を保持する第2論理素子及び第3論理素子と、トランジスタを用いたスイッチング素子と、第2論理素子及び第3論理素子において保持される第1論理素子の出力電位が、スイッチング素子を介して与えられることで、データを記憶する容量素子と、を有し、第2論理素子は、第1クロック信号とは異なる系統の第2クロック信号に従って、第3論理素子の出力電位の極性を反転させることで、第2論理素子の出力電位を生成し、第3論理素子は、第2論理素子の出力電位の極性を反転させることで、第3論理素子の出力電位を生成する記憶装置。

(もっと読む)

半導体装置の作製方法

【課題】本発明の一態様は、酸化物半導体を用いたデバイスにおいて高い移動度を達成し

、信頼性の高い表示装置を提供する。

【解決手段】表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層を形

成し、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加熱処理を行うことによ

り、酸化物半導体層に酸素を供給し、酸化物絶縁層上に、水素を含む窒化物絶縁層を形成

し、第4の加熱処理を行うことにより、少なくとも酸化物半導体層と酸化物絶縁層の界面

に水素を供給する。

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】消費電力の増大を抑制し且つ微細化を達成した半導体装置および当該半導体装置の作製方法を提供する。また、安定した電気的特性が付与された、信頼性の高い半導体装置および当該半導体装置の作製方法を提供する。

【解決手段】酸化物半導体膜に電界で加速されたイオンを照射して、当該酸化物半導体膜の表面の平均面粗さを低減することにより、トランジスタのリーク電流の増大および消費電力の増大を抑制することができる。さらに、加熱処理を行って、酸化物半導体膜が当該酸化物半導体膜表面に垂直なc軸を有する結晶を含むように形成することにより、酸化物半導体膜の可視光や紫外光の照射による電気的特性の変化を抑制することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の一部にメタルゲート電極を有するMISEFTにおいて、メタルゲート電極を構成するグレインの配向性のばらつきに起因するMISFETのしきい値電圧のばらつきを小さくする。

【解決手段】メタルゲート電極4a、4bに炭素(C)を導入することにより、メタルゲート電極4a、4b内のグレインの粒径が大きくなることを防ぎ、メタルゲート電極4a、4bの中に多数の小さいグレインを形成することにより、グレインの配向性を均一化し、ゲート電極の仕事関数のばらつきを低減する。

(もっと読む)

半導体装置の製造方法

【課題】充分なキャパシタ容量を有する半導体装置を提供する。

【解決手段】半導体装置100の製造方法は、次の工程を含む。まず、基板(半導体基板102)上に下部電極152を形成する。次いで、下部電極152を第1結晶化処理する。次いで、第1結晶化処理後の下部電極152の上に容量絶縁層154を形成する。次いで、容量絶縁層154を第2結晶化処理する。この後、容量絶縁層154上に上部電極156を形成する。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲートトランジスタのゲート電極間の間隔の縮小を実現する不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板に、複数の第1の素子領域と、素子分離領域と、第2の素子領域を形成する。第1の素子領域上に、メモリセルゲート電極、2本の選択ゲート電極を形成し、第2の素子領域に周辺ゲート電極を形成する。第1の絶縁膜を形成し、周辺ゲート電極の側壁部上が開口される第1のレジストパターンを形成し、第1のエッチング処理を行い、側壁絶縁膜を形成する。第2のレジストパターンを形成し、第2のエッチング処理を行い、選択ゲート電極側壁部の第1の絶縁膜を除去する。第2の絶縁膜を堆積し、第3の絶縁膜を堆積する。2本の選択ゲート電極間上が開口される第3のレジストパターンを形成し、第3のエッチングおよび第4のエッチング処理を行い、コンタクトホールを形成する。

(もっと読む)

半導体装置の製造方法

【課題】スループットを低下させずに異なるメモリセルの誘電体膜とキャパシタの誘電体膜を同時に形成するための半導体装置の製造方法を提供する。

【解決手段】第1酸化膜18、窒化膜19、第2酸化膜20を順に形成した第1の誘電体膜を第1の半導体膜16上に形成する工程と、第1領域I内の第1の誘電体膜21をエッチングする工程と、第1領域Iの半導体基板1の表面に第3酸化膜25を形成する工程と、第1領域VI及び第2領域IIIに開口部28a、28bを有し、さらに第3領域II内の第1の誘電体膜21を覆う形状を有するマスク28を半導体基板1の上方に形成する工程と、マスク28の開口部28a、28bを通して、第1領域VI内の前記第3酸化膜25と前記第2領域III内の第1の誘電体膜21の第2酸化膜20を同時にエッチングする工程を含む。

(もっと読む)

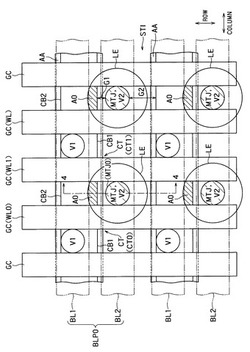

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

記憶素子およびその製造方法ならびに記憶装置

【課題】低電流動作に優れると共に良好な保持特性を有する記憶素子および記憶装置を提供する。

【解決手段】本開示の記憶素子は、第1電極、記憶層および第2電極をこの順に有し、記憶層は、酸化物を含むと共に、第1電極側に設けられた抵抗変化層と、テルル(Te),硫黄(S)およびセレン(Se)のうちの少なくとも1種のカルコゲン元素および記憶層内の移動が容易な移動容易元素を含み、第1電極から第2電極に向かって移動容易元素の濃度分布を有する第1層と、記憶層内を移動しにくい移動困難元素を含む第2層とからなる単位イオン源層が少なくとも2層積層され、第2電極側に設けられたイオン源層とを備える。

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い半導体装置及び、信頼性の高い半導体装置の作製方法を提供する。また、消費電力が低い半導体装置及び消費電力が低い半導体装置の作製方法を提供する。また、量産性の高い半導体装置及び量産性の高い半導体装置の作製方法を提供する。

【解決手段】酸素欠損を生じることなく酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すればよい。具体的には、酸化物半導体層に酸素を添加した後に加熱処理を施し、不純物を除去して使用すればよい。特に酸素の添加方法としては、高エネルギーの酸素をイオン注入法またはイオンドーピング法などを用いて添加する方法が好ましい。

(もっと読む)

半導体メモリ装置

【課題】酸化物半導体のようなバンドギャップが大きな半導体を用いたメモリ装置の保持特性を高める。

【解決手段】ビット線の一端にバックゲートを有するトランジスタ(バックゲートトランジスタ)を直列に挿入し、そのバックゲートの電位は常に十分な負の値となるようにする。また、ビット線の最低電位はワード線の最低電位よりも高くなるようにする。電源が切れた際には、ビット線はバックゲートトランジスタによって遮断され、ビット線に蓄積された電荷が流出することが十分に抑制される。この際、セルトランジスタのゲートの電位は0Vであり、一方で、そのソースやドレイン(ビット線)の電位は、ゲートよりも十分に高いので、セルトランジスタは十分なオフ状態であり、データを保持できる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】PRAMの高集積化を行うこと。

【解決手段】第1層間絶縁膜のホールの内壁面を覆うサイドウォール絶縁膜と、ホール内においてサイドウォール絶縁膜を介して埋め込まれたコンタクトプラグと、第1層間絶縁膜上の所定の領域にてコンタクトプラグに接続されるように配された下部電極と、下部電極を含む前記第1層間絶縁膜上を覆う第2層間絶縁膜と、第2層間絶縁膜を貫通し、下部電極の側端面の一部が表れ、かつ、第1層間絶縁膜の所定深さまで形成された開口部と、開口部を含む前記第2層間絶縁膜上の所定の領域に配されるとともに、前記開口部にて前記下部電極の側端面の一部と接続された相変化材料層と、相変化材料層上に配された上部電極と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】容量絶縁膜の絶縁性の劣化が生じにくく、かつ容量プレート電極の厚みが薄い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、互いに異なる平面面積を持つメモリセル部と補償容量部とを単一の基板上に備える。メモリセル部と補償容量部とは、同一構成の容量プレート電極を含む。容量プレート電極は、ボロンドープシリコンゲルマニウム膜と金属膜とを含む積層構造を有している。

(もっと読む)

半導体装置およびその製造方法

【課題】活性領域における上記プラグと、活性領域の外部における上記プラグとの双方を有する、微細化された半導体装置において、枠付け絶縁膜を確実に形成し、かつ導電性などの機能を最適化することが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に形成される活性領域と、平面視における活性領域の周辺に形成されるゲート接続領域と、活性領域上に形成される複数の第1のトランジスタTGに挟まれる領域に形成される、第1のトランジスタTGと第1のトランジスタTGよりも上側の層とを電気的に接続するための第1の接続層CTと、ゲート接続領域上に形成される第2のトランジスタTGと、第2のトランジスタTGよりも上側の層とを電気的に接続するための第2の接続層とを備えている。上記第1の接続層CTには第1の導電部PP1aと第2の導電部PP2aとを含み、第2の接続層SNCには第3の導電部PP2bを含む。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

記憶素子およびその製造方法ならびに記憶装置

【課題】低電流動作に優れると共に良好な保持特性を有する記憶素子および記憶装置を提供する。

【解決手段】本開示の記憶素子は、第1電極、記憶層および第2電極をこの順に有し、記憶層は、第1電極側に設けられた抵抗変化層と、少なくとも1種の金属元素を含むと共に、第2電極側に設けられたイオン源層とを備え、イオン源層は、テルル(Te),硫黄(S)およびセレン(Se)のうちの少なくとも1種のカルコゲン元素を含むと共に、抵抗変化層側に設けられた第1イオン源層と、第1イオン源層とはカルコゲン元素の含有量が異なると共に、第2電極側に設けられた第2イオン源層とからなる。

(もっと読む)

半導体装置

【課題】浮遊状態の配線と洗浄水との間において高い密度で電荷が移動することに起因する配線の高抵抗化を防ぐ。

【解決手段】半導体製造装置の製造工程中において、半導体基板1Sなどと絶縁された浮遊状態となる銅配線である第1層配線L1の上面に、電気的に機能する接続ビアPL2と電気的に機能しないダミービアDP2とを接続させて形成する。これにより、第1層配線L1の上面に接続ビアPL2を形成するためのビアホールを形成した後の洗浄工程中に、第1層配線L1に溜まった電荷が洗浄水中に移動する際、前記電荷をダミービアDP2形成用のビアホールにも分散させることで、接続ビアPL2形成用のビアホールの底部のみに前記電荷が集中することを防ぐ。

(もっと読む)

半導体装置

【課題】酸化物半導体のようなバンドギャップが大きな半導体を用いたメモリ装置の保持特性を高める。

【解決手段】ビット線にビット線制御トランジスタを直列に挿入し、そのゲートの最低電位は十分な負の値となるようにする。ビット線制御トランジスタのゲートは電池等に接続するビット線制御回路に接続される。ビット線の最低電位はワード線の最低電位よりも高くなるようにする。外部からの電源が切れた際には、ビット線はビット線制御トランジスタによって遮断され、ビット線に蓄積された電荷が流出することが十分に抑制される。この際、セルトランジスタのゲートの電位は0Vであり、一方で、そのソースやドレイン(ビット線)の電位は、ゲートよりも十分に高いので、セルトランジスタは十分なオフ状態であり、データを保持できる。あるいは外部電源遮断時にワード線の電位を十分な負の電位とできるような回路を設けてもよい。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

121 - 140 / 2,373

[ Back to top ]