Fターム[5F083MA19]の内容

Fターム[5F083MA19]の下位に属するFターム

拡散層とビット線 (1,521)

Fターム[5F083MA19]に分類される特許

201 - 220 / 2,373

ダイオードストラッピングを備えた熱アシストフラッシュメモリ

【課題】フラッシュメモリの動作速度及び耐久性を向上させる技術の提供。

【解決手段】メモリが、行及び列を含むメモリセルのアレイを有している。該メモリは、アレイ内の単数又は複数のワード線上の第1の離隔位置のセットに第1のバイアス電圧を印加するとともに、単数又は複数のワード線上の第2の離隔位置のセットに第1のバイアス電圧とは異なる第2のバイアス電圧を印加する、ワード線に結合された回路部を有し、第1の離隔位置のセットにおける位置は、第2の離隔位置のセットの位置の間に介在しており、それにより、第1の離隔位置のセットにおける位置と第2の離隔位置のセットにおける位置との間に、単数又は複数のワード線の加熱をもたらす電流の流れが誘導される。

(もっと読む)

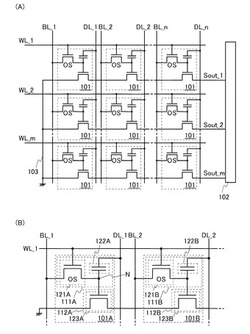

半導体記憶装置

【課題】不揮発性の記憶装置を有するCAMとする際に、メモリセルの低消費電力化を図ることのできる半導体記憶装置を提供することを課題の一とする。また、データの書き込みを繰り返し行う際の劣化をなくすことができる半導体記憶装置を提供することを課題の一とする。また、メモリセルの高密度化が可能な不揮発性の記憶装置を提供する。

【解決手段】酸化物半導体を半導体層に有する第1のトランジスタ及び当該第1のトランジスタをオフ状態とすることで書き込んだデータに対応する電位を保持できる容量素子を有するメモリ回路と、書き込んだ電位を参照するための参照回路を有し、参照回路を構成する第2のトランジスタの導通状態を検出することで、整合するデータのアドレスを取得し、高速な検索機能を可能にした半導体記憶装置である。

(もっと読む)

半導体装置

【課題】抵抗素子を有する半導体装置に関し、集積度を低下することなく低消費電力化と高い回路精度とを実現しうる半導体装置を提供する。

【解決手段】半導体材料により形成された複数の抵抗素子と、複数の抵抗素子の近傍に配置された加熱用抵抗素子と、対向する2つの接続ノード間に加熱用抵抗素子が接続され、対向する他の2つの接続ノード間に電源線が接続された抵抗ブリッジ回路とを有する。

(もっと読む)

多値ROMセル及び半導体装置

【課題】集積度が高く、製造ばらつきの影響が小さく、製造歩留まりの高い多値ROMセルを提供する。

【解決手段】多値ROMセルは、ROMセルトランジスタTrと、複数のビット線BT1〜BT3と、第1金属配線31〜44とを具備している。ROMセルトランジスタTrは、基板表面の領域に設けられている。複数のビット線BT1〜BT3は、基板表面の上方に設けられ、Y方向に伸び、Z方向に並んで配置されている。第1金属配線31〜44は、ROMセルトランジスタTrのソース・ドレイン22の一方に接続され、複数のビット線BT1〜BT3の各々の近傍にまで連なる。第1金属配線31〜44は、複数のビット線BT1〜BT3のうちのいずれかに接続されているか、又は、いずれにも接続されていない。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させる。

【解決手段】ゲート電極GE1,GE2、ソース・ドレイン用のn+型半導体領域SD1及びp+型半導体領域SD2を形成してから、半導体基板1上にNi−Pt合金膜を形成し、第1の熱処理を行って合金膜とゲート電極GE1,GE2、n+型半導体領域SD1及びp+型半導体領域SD2とを反応させることで、(Ni1−yPty)2Si相の金属シリサイド層13aを形成する。この際、Niの拡散係数よりもPtの拡散係数の方が大きくなる熱処理温度で、かつ、金属シリサイド層13a上に合金膜の未反応部分が残存するように、第1の熱処理を行う。その後、未反応の合金膜を除去してから、第2の熱処理を行って金属シリサイド層13aを更に反応させることで、Ni1−yPtySi相の金属シリサイド層13bを形成する。第2の熱処理の熱処理温度は580℃以上で、800℃以下とする。

(もっと読む)

半導体素子及びその製造方法

【課題】干渉現象を減らしてゲートラインの抵抗を減らすことができる半導体素子の製造方法を提供する。

【解決手段】最上部層が金属シリサイド層からなり、第1間隔で半導体基板上に配列される第1ゲートラインと、最上部層が金属シリサイド層からなり、前記第1間隔より広い第2間隔で前記半導体基板上に配列される第2ゲートラインと、前記第1ゲートラインの間の前記半導体基板上に形成されてエアギャップを含む第1絶縁膜と、前記第2ゲートラインの対向する側壁上に形成された第2絶縁膜と、前記第2絶縁膜の側壁に形成されたエッチング停止膜と、前記第1ゲートラインの間の空間と前記第2ゲートラインとの間の空間が満たされるように全体構造上に形成された第3絶縁膜と、前記第3絶縁膜の上部に形成されたキャッピング膜と、前記キャッピング膜及び前記第3絶縁膜を貫通して前記第2ゲートラインの間の前記半導体基板に形成された接合領域と繋がれるコンタクトプラグと、を含む。

(もっと読む)

半導体装置

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置において、安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタ(半導体装置)において、酸化物半導体膜を、絶縁層に設けられたトレンチ(溝)に設ける。トレンチは曲率半径が20nm以上60nm以下の曲面状の下端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも下端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置

【課題】微細化が可能であるメモリセル構造を備える半導体装置を提供する。

【解決手段】ワード線と、ビット線と、電源ノードと、ビット線と電源ノードとの間にPN結合を成す第1及び第2の領域並びに第2の領域とPN結合を成す第3の領域を少なくとも有するメモリ素子と、メモリ素子の第2の領域とは独立して設けられてメモリ素子の第2の領域と電気的に接続された第1の電極及び前記ワード線に接続された第2の電極を有するキャパシタと、を備える。

(もっと読む)

半導体装置

【課題】不揮発性であって、作製が簡単であり、追記が可能な記憶回路を有する半導体装置の提供を課題とする。

【解決手段】本発明の半導体装置は、複数のトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記複数のトランジスタのうちの1つの上に設けられた記憶素子及びアンテナとして機能する導電層とを有し、前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、アンテナとして機能する前記導電層と前記複数のトランジスタのソース配線又はドレイン配線として機能する導電層とは、同じ層上に設けられていることを特徴とする。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置、及び半導体装置の作製工程において、安定した電気的特性を付与し、高信頼性化する。また、上記半導体装置の作製工程において、不良を抑制し、歩留まりよく作製する技術を提供する。

【解決手段】酸化物半導体層を含むトランジスタを有する半導体装置において、酸化物半導体膜を、絶縁層に設けられたトレンチに設ける。トレンチは下端コーナ部及び曲率半径が20nm以上60nm以下の曲面状の上端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、上端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも上端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を提供する。また、不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】トレンチを有する絶縁層に接して、ソース領域またはドレイン領域として機能する領域の膜厚が、チャネル形成領域として機能する領域の膜厚よりも厚い酸化物半導体層を形成する。該酸化物半導体層を用いたトランジスタは、ソース抵抗またはドレイン抵抗を低減することができると共に、しきい値のバラツキ、電気特性の劣化、ノーマリーオン化を抑制することができ、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体デバイス及びその製造方法

【課題】エッチング選択比の高い非晶質炭素膜を用いたシリンダ型キャパシタを有する半導体デバイスでは、非晶質炭素膜を除去する際に、キャパシタの下部電極に変形が生じやすい。

【解決手段】非晶質炭素膜及び層間絶縁膜をメモリセル領域及び周辺回路領域にそれぞれ形成し、非晶質炭素膜及び層間絶縁膜上に絶縁膜を形成し、非晶質炭素膜上のキャパシタに対応した部分における絶縁膜を除去して、キャパシタの下部電極を両側から支持すると共に、メモリセル領域から周辺回路領域まで連続的に覆う絶縁膜パターンを形成する。続いて、非晶質炭素膜を用いたキャパシタを形成した後、絶縁膜パターン下部の非晶質炭素膜を除去する。

(もっと読む)

半導体装置

【課題】先端プロセスでは、MOSのゲートトンネルリーク電流が増大し、低リーク電流での待機が必要となる半導体装置では問題となる。

【解決手段】電源線とソース線との電位差である複数のスタティック型メモリセルの電源電圧を制御する電源電圧制御回路を具備する。負荷型P型MOS及び駆動型N型MOSのゲート絶縁膜厚は、4nm以下である。電源電圧制御回路は、動作状態では前記電源電圧を第1電圧とし、待機状態では前記電源電圧を前記第1電圧よりも小さい第2電圧とするように制御して、オフ状態での負荷型P型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流、及び、駆動型N型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流を動作状態に対し待機状態の方を小さくする。

(もっと読む)

半導体装置

【課題】隣接するメモリセル間およびメモリセルと選択トランジスタとの間に間隙を設け

つつ、選択トランジスタおよび周辺回路における短絡を抑制する。

【解決手段】本実施形態による半導体記憶装置は、ゲートを有する複数のメモリセルが直

列に接続されたメモリセルストリングを備える。選択トランジスタが、メモリセルストリ

ングの一端にある端部メモリセルに接続されている。側壁膜が、端部メモリセルと選択ト

ランジスタとの間において、端部メモリセルのゲートの側面および選択トランジスタのゲ

ートの側面を被覆する。端部メモリセルの側壁膜と選択トランジスタの側壁膜との間に空

隙がある。

(もっと読む)

半導体基板、半導体装置及びその製造方法

【課題】キャリア移動度(チャネル移動度)を増加させて、オン電流を増加させること。

【解決手段】トランジスタを形成するための半導体基板(10)は、主面(11a)を持つシリコン基板(11)と、このシリコン基板(11)の主面(11a)上に形成された歪緩和SiGe層(12)と、この歪緩和SiGe層(12)上に形成された歪Si層(13)と、を含む。

(もっと読む)

記憶素子および信号処理回路

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路を提供する。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、アモルファスシリコン、ポリシリコン、微結晶シリコン、あるいは酸化物半導体等の化合物半導体をチャネル形成領域に含み、そのチャネル長が最小加工線幅の10倍以上あるいは、1μm以上であるトランジスタを用いる。上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】埋め込みビットライン型不揮発メモリの微細化に適した製造方法を提供し、かつコンタクトの位置ずれに起因するビットライン間ショートを生じ難い構造を提供する。

【解決手段】導電体膜が埋め込まれたシャロートレンチ溝内にビットライン拡散層を設けてSONOS構造セルとする。これにより、ビットライン拡散層の半導体基板主面上での面積を大きくせずにビットライン拡散層の抵抗を低くすることができ、セル面積を増大させることなく安定した電気的特性の半導体記憶装置が得られる。また、Si3N4のサイドウォールを設けてイオン注入することでビットラインを形成する。これにより、メモリセルの微細化が可能となる。

(もっと読む)

不揮発性半導体記憶装置とその製造方法

【課題】メモリセルが3次元的に積層された不揮発性半導体記憶装置で、メモリセルの投影面積を小さくすることができ、従来の平面型のフローティングゲート構造と類似の構造の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、シート状のチャネル半導体膜111の高さ方向に複数のメモリセルMCを有するメモリストリングが基板上にほぼ垂直に配置される。フローティングゲート電極膜109は、第2の方向に延在し、トンネル誘電体膜110を介してチャネル半導体膜111の第1の主面上に形成される。制御ゲート電極膜103は、第1の方向に延在する共通接続部1031と、共通接続部1031から第2の方向に突出し、フローティングゲート電極膜109の上部または下部に電極間絶縁膜108を介してメモリセルMCごとに設けられる電極構成部1032と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ウェル給電領域の面積を縮小して、半導体装置の微細化を行う。素子形成領域間のウェル電位のばらつきを抑制する。分離部の幅を細くする。

【解決手段】半導体装置は、半導体基板の表面に形成され、底部がウェル領域内に位置する溝状の分離部を有する。分離部は、ウェル領域と電気的に接続された導体配線と、底部に導体配線を埋め込む絶縁膜とを有する。分離部に囲まれるようにして区画されたウェル領域の一部は素子形成領域を形成し、素子形成領域には半導体素子が配置される。

(もっと読む)

201 - 220 / 2,373

[ Back to top ]