Fターム[5F083PR23]の内容

Fターム[5F083PR23]に分類される特許

101 - 120 / 646

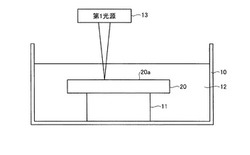

薄膜製造方法および薄膜素子

【課題】低コストで安定した品質の薄膜を製造することができる薄膜製造方法を提供する。

【解決手段】薄膜製造方法であって、基板20上に形成させる薄膜の原料溶液中に、基板20を配置する配置工程と、基板20の第1主面20aに光を照射することにより、第1主面20a上に薄膜を形成する形成工程とを有する。

(もっと読む)

半導体装置

【課題】従来のメモリ素子とは異なり、軟化又は溶融といった状態変化を利用したメモリ素子を提供し、メモリ容量が増大されたメモリ装置を提供することを課題とする。

【解決手段】一対の電極間に、ガラス転移温度が異なる複数のメモリ材料層を積層させたメモリ素子である。ガラス転移温度は10℃以上の差があると好ましい。このようなメモリ素子に電圧を印加することで、複数のメモリ材料層を一つずつ軟化又は溶融させる。このような構成により、メモリ容量が3値以上となり増大される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】縦型MOSトランジスタを備えた半導体装置を形成する際のゲート電極とコンタクトプラグとの短絡を防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、前記半導体基板上にシリコン窒化膜(SiN膜)からなるマスク窒化膜のパターンを形成したのちに、溝および半導体ピラーを前記半導体基板に形成する第一工程と、前記マスク窒化膜を残存させたまま、前記溝を覆うゲート絶縁膜を形成したのちに前記半導体ピラーよりも低い高さのゲート電極を形成する第二工程と、前記溝を覆うように、シリコン酸窒化膜(SiON膜)からなるライナー膜を形成したのちに、前記ライナー膜上を覆い、かつ、前記溝内を充填するように層間膜(SOD膜)を形成する第三工程と、前記マスク窒化膜をエッチングにより選択的に除去する第四工程と、を採用する。

(もっと読む)

半導体装置の作製方法

【課題】不揮発性であって、作成が簡単であり、追記が可能な記憶回路を有する半導体装

置及びその作製方法の提供を課題とする。

【解決手段】一対の導電層間に有機化合物層が挟まれた単純な構造の記憶素子を有する半

導体装置及びその作製方法を提供する。また、不揮発性であり、作製が簡単であり、追記

が可能な記憶回路を有する半導体装置及びその作製方法を提供する。絶縁層上に設けられ

た複数の電界効果トランジスタと、複数の電界効果トランジスタ上に設けられた複数の記

憶素子とを有する。複数の電界効果トランジスタは、単結晶半導体層をチャネル部とした

電界効果トランジスタである。複数の記憶素子の各々は、第1の導電層と、有機化合物層

と、第2の導電層が順に積層された素子である。

(もっと読む)

液体噴射ヘッド、液体噴射装置及び圧電素子並びに圧電材料

【課題】鉛を含有せず、歪み量が大きい圧電素子を有する液体噴射ヘッド、液体噴射装置及び圧電素子並びに圧電材料を提供する。

【解決手段】ノズル開口21に連通する圧力発生室12と、第1電極60と、第1電極60上に形成された圧電体層70と、圧電体層70上に形成された第2電極80と、を備えた圧電素子300と、を具備し、圧電体層70は、Bi、La、Fe及びMnを含むペロブスカイト型複合酸化物からなり、電界誘起相転移を示す液体噴射ヘッドとする。

(もっと読む)

製造装置および製造方法

【課題】簡便な方法で、良好な強誘電体膜を所定の厚さで形成する。

【解決手段】誘電体膜を有する基板を製造する製造装置であって、複合酸化物を含む原材料体が塗布された基板を、大気圧以上の圧力に加圧した、体積比20%以上の酸素を含む雰囲気中で熱処理して結晶化させる熱処理装置を備える製造装置および製造方法を提供する。当該製造装置は、光制御デバイスとして用いられる強誘電体膜を有する基板を製造してもよい。熱処理装置は、原材料が塗布された基板を雰囲気中に保持するチャンバと、熱処理中における予め定められた期間の間、チャンバ内の雰囲気の圧力を予め定められた圧力に調整する圧力調整部と、を有してもよい。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】消費電力を抑制することにより特性を向上させる不揮発性メモリおよび不揮発性メモリの製造方法を提供する。

【解決手段】第1の配線10と第2の配線11とに接続された記憶セル80aを備え、前記記憶セル80aは、複数の層を有し、前記複数の層は、記憶層である抵抗変化膜24と、前記記憶層に接し複数のカーボンナノチューブ23cを含むカーボンナノチューブ含有層23とを有し、カーボンナノチューブ23cが抵抗変化膜24の電極として機能する。

(もっと読む)

抵抗変化型メモリとその製造方法

【課題】従来技術に比較して高い再現性で確実に抵抗のヒステリシス特性及びメモリ特性を発現させることができる抵抗変化型メモリとその製造方法を提供する。

【解決手段】PrxCa1−xMnO3にてなるPCMO層を下部電極と上部電極とにより挟設してなる抵抗変化型メモリにおいて、上記PCMO層と上記上部電極もしくは下部電極との間に金属酸化物層を挿入形成した。ここで、上記金属酸化物は上記上部電極の金属の酸化物であり、上記上部電極と下部電極の少なくとも一方はタングステン(W)、モリブデン(Mo)、クロム(Cr)、アルミニウム(Al)、銀(Ag)のうちのいずれかにてなる。

(もっと読む)

不揮発性メモリセル及びその製造方法

【課題】同一の基板上に形成されたメモリトランジスタ及び駆動トランジスタを備える透明不揮発性メモリセル及びその製造方法を提供する。

【解決手段】本発明による不揮発性メモリセルは、基板上に形成された半導体膜、バッファー膜、有機強誘電体膜及びゲート電極を含むメモリトランジスタと;前記基板上に形成された前記半導体膜、前記バッファー膜、ゲート絶縁膜及び前記ゲート電極を含む駆動トランジスタと;を備える。本発明によれば、同一の基板上に形成されたメモリトランジスタ及び駆動トランジスタを備え、可視光領域で透明な不揮発性メモリセルを提供することができる。

(もっと読む)

不揮発性メモリ装置及びその製造方法

【課題】上下部電極間の短絡を防止しながら、高密度記録と動作電流低減を実現する不揮発性メモリ装置及びその製造方法を提供する。

【解決手段】不揮発性メモリ装置は、基板20と、前記基板20上に形成された下部電極21と、前記下部電極21上に形成された導電性ナノマテリアルを含む抵抗変化層23と、前記抵抗変化層23上に形成された上部電極24と、前記下部電極21と前記抵抗変化層23の間に形成された、前記下部電極21と前記抵抗変化層23の間の電気的導通を確保する導電材22bを分散させた絶縁性バッファ層22と、を有する。

(もっと読む)

半導体記憶素子の製造方法

【課題】金属ナノ結晶からなる離散的フローティングゲートを、移流集積法により形成する半導体記憶素子の製造方法を提供する。

【解決手段】製造方法は、シリコン基板1と、シリコン基板1上に形成されたトンネル絶縁膜に対向するように配置された第2の基板21との間に、金属ナノ粒子が分散された粒子分散液22を充填する充填工程と、トンネル絶縁膜の表面に沿った方向に、第2の基板21をシリコン基板1に対して相対的に移動させることにより、トンネル絶縁膜の表面における第2の基板21から露出した領域に形成される粒子分散液22のメニスカス領域23において、粒子分散液22の溶媒を蒸発させることにより、トンネル絶縁膜上に金属ナノ粒子を離散的に配置する。

(もっと読む)

強誘電体膜、電子部品及び強誘電体膜の製造方法

【課題】結晶化しようとする強誘電体膜の配向を変換して任意に制御した強誘電体膜を提供する。

【解決手段】本発明の一態様に係る強誘電体膜は、基板上に形成された(111)配向したPt膜4と、前記Pt膜上に形成されたPZT膜6と、を具備し、前記PZT膜は、(111)+(001)、(001)、(001)+(110)及び(110)のいずれかに配向されていることを特徴とする。

(もっと読む)

強誘電体キャパシタ及び強誘電体メモリ装置

【課題】 強誘電体キャパシタ及び強誘電体メモリ装置に関し、PZTより大きな残留分極量を有する(111)配向性に優れた強誘電体薄膜を得る。

【解決手段】 正方晶Pb(ZrxTi1−x)O3 に、前記正方晶Pb(ZrxTi1−x)O3 よりc軸/a軸比が大きい正方晶ペロブスカイト構造を有する材料を添加して(111)優先配向した強誘電体膜と、前記強誘電体膜を挟む下部電極と上部電極とを設ける。

(もっと読む)

PZT膜、電子部品、酸化物材料膜の製造方法及び水蒸気加圧急速加熱装置

【課題】酸化物材料膜の結晶化温度を低温化できる水蒸気加圧急速加熱装置を提供する。

【解決手段】本発明の一態様に係る水蒸気加圧急速加熱装置は、処理室34内に配置された、基板35を載置する載置台36と、前記載置台に載置された基板を加熱する加熱機構38と、前記処理室内を加圧する加圧機構43と、前記処理室内に加熱及び加圧された水蒸気を供給する水蒸気供給機構と、前記処理室内を真空排気する真空排気機構56と、前記処理室内に加熱及び加圧された酸素ガスを供給する酸素ガス供給機構と、を具備する。

(もっと読む)

ナノ構造ベースNANDフラッシュセルおよびその周辺回路の形成方法

ナノ構造に基づく電荷蓄積領域は、不揮発性メモリ装置に備えられており、選択ゲートおよび周辺回路の製造と一体に製造される。1つ以上のナノ構造コーティングは、メモリアレイ領域および周辺回路領域の基板に塗布される。選択ゲートや周辺トランジスタについての目標領域などの基板の不要な領域から、ナノ構造コーティングを除去するための様々な工程が、行われる。一例では、基盤のアクティブ領域にナノ構造を選択的に形成するために、自己組織化に基づく工程を用いて、1つ以上のナノ構造コーティングが形成される。自己組織化によって、ナノ構造コーティングのパターニングやエッチングを行うことなく、互いに電気的に分離されているナノ構造の個別のライン群を形成することができる。  (もっと読む)

(もっと読む)

強誘電体薄膜の製造方法

【課題】基板の外周端部の膜をクラックや局部剥がれを生じることなく除去して、パーティクルの発生を防止する。

【解決手段】強誘電体薄膜形成用の有機金属化合物を含有するCSD溶液を基板2に塗布してゲル状塗膜1を形成する工程と、基板2を回転させながら外周端部に水Wを噴射又は滴下して、ゲル状塗膜1の外周端部を除去する工程と、外周端部について除去された後のゲル状塗膜1を加熱処理して強誘電体薄膜を形成する工程とを有する。

(もっと読む)

半導体装置およびNAND型フラッシュメモリの製造方法

【課題】素子間を確実に絶縁可能な半導体装置およびNAND型フラッシュメモリの製造方法を提供する。

【解決手段】アスペクト比が高いSTI用の溝6に対しては、塗布材料8を充填した後に酸素イオン等を注入し、その後に酸化処理を行うため、溝6の底部にまでSiO2膜16を形成できる。一方、アスペクト比が小さい溝6に対しては、高密度プラズマCVD法やTEOS/O3法を用いるため、SiO2膜16より絶縁性の高い絶縁膜SiO2膜15を形成できる。以上のように、溝6のアスペクト比に応じて、最適な手法で絶縁膜を形成するため、素子分離領域のアスペクト比によらず、半導体装置の素子間を確実に絶縁することができる。

(もっと読む)

切替え可能な電子デバイスおよびそのデバイスの切替え方法

切替え可能な電子デバイスは、第1の電極(1)と第2の電極(4)との間にホールブロッキング層(2)および導電性材料を含む層(3)を備え、電流密度が100Acm−2以下である電流を流すと、切替え前のデバイスの導電率の100分の1以下の導電率までデバイスの導電率を不可逆的に切り替えることができる。導電性材料は、ドープされ、任意選択で置換されているポリ(エチレンジオキシチオフェン)などのドープ有機材料である。ホールブロッキング層(2)は微粒子層、特に、ナノ粒子層を備えることができる。 (もっと読む)

情報記録素子及び情報記録装置並びにその製造方法

【課題】構造が簡単な印刷法で形成が可能な情報記録部材を提供すること。

【解決手段】基板102と、前記基板上に設けられた一つ以上の下部配線103と、前記下部配線上に印刷法で設けられた複数の導電性バンプ104と、前記基板と前記下部配線と前記導電性バンプとを覆うように設けられた絶縁層105と、前記下部配線と交差し前記導電性バンプに重なるように前記絶縁層上に設けられた一つ以上の上部配線106とを備えることを特徴とする情報記録装置。

(もっと読む)

半導体装置とその製造方法

【課題】1つのチップに圧電素子と強誘電体素子とを混載させ、得られる半導体装置の小型化を図ることが可能な半導体装置とその製造方法を提供する。

【解決手段】本発明の半導体装置1は、圧電素子3と、強誘電体素子2と、を同一基板上に備える半導体装置1において、強誘電体素子2を構成する強誘電体膜15bが、圧電素子3を構成する圧電体膜4の少なくとも一部と同じ材料から形成されていることを特徴とする。

(もっと読む)

101 - 120 / 646

[ Back to top ]