Fターム[5F083ZA07]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリセルと周辺回路の関係 (1,873) | MOSFETの構造が異なるもの (1,090) | ゲート絶縁膜が異なるもの (403)

Fターム[5F083ZA07]に分類される特許

221 - 240 / 403

半導体記憶装置およびその製造方法

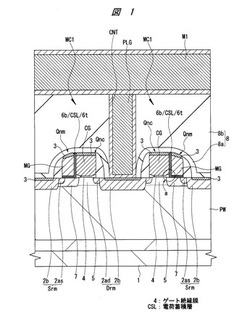

【課題】スプリットゲート型MONOSメモリセルにおいて、SSI方式による書込み時のディスターブ耐性を向上させることのできる技術を提供する。

【解決手段】選択用nMISQncと、選択用nMISQncの側面に絶縁膜6b、6tおよび電荷蓄積層CSLを介して形成されたメモリ用nMISQnmとを含むメモリセルMC1において、選択ゲート電極CGのゲート長方向端部下のゲート絶縁膜4の厚さが、ゲート長方向中央部下のゲート絶縁膜4の厚さよりも厚く形成され、選択ゲート電極CGと電荷蓄積層CSLとの間に位置し、かつ半導体基板1に最も近い下層の絶縁膜6bの厚さが、半導体基板1と電荷蓄積層CSLとの間に位置する下層の絶縁膜6bの厚さの1.5倍以下に形成される。

(もっと読む)

不揮発性記憶トランジスタおよびその製造方法

【課題】標準CMOSプロセスを用いて効率的なキャリア注入が可能な不揮発性記憶トランジスタを提供する。

【解決手段】サイドスペーサに電荷を注入してしきい値電圧を変化させることにより、データを記憶するN型の不揮発性記憶トランジスタを、ゲート絶縁膜の膜厚がI/Oトランジスタのゲート絶縁膜の膜厚と同じであり、チャンネル領域の不純物濃度がコアトランジスタと同じまたはそれよりも濃く、ドレイン側のLDD領域にチャンネル領域よりも濃度の濃いP型領域が形成され、且つ、ゲート電極用ポリシリコンがP型ポリシリコンであるトランジスタで構成した。

(もっと読む)

半導体記憶装置の製造方法

【課題】動作特性を向上させる半導体記憶装置の製造方法を提供すること。

【解決手段】半導体基板10の第1領域上に、第1ゲート絶縁膜14を介在して第1ゲート電極を形成する工程と、前記半導体基板10の第2領域上に、第2ゲート絶縁膜33を介在して第2ゲート電極を形成する工程と、絶縁膜18を形成する工程と、前記半導体基板上10にフォトレジストを塗布して前記第2領域を被覆しつつ、前記第1領域を露出させる工程と、前記フォトレジスト、前記第1ゲート電極、及び前記絶縁膜18をマスクに用いて、前記第1領域中に不純物を注入する工程と、ウェットエッチングにより、前記フォトレジストを除去する工程とを具備し、前記絶縁膜18は、前記フォトレジストに対して1:100以上のエッチング選択比を有する材料を用いて形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧トランジスタと低耐圧トランジスタが混在する構成の半導体装置の加工工程で、高耐圧用の厚い膜厚のゲート絶縁膜を除去するための工程をなくす。

【解決手段】シリコン基板1に高耐圧トランジスタ2のゲート電極GHを形成する領域にあらかじめリセス7を形成し、ここに高耐圧用の厚いゲート絶縁膜となるシリコン酸化膜8を形成する。ソース/ドレイン領域および低耐圧トランジスタ3に対応する部分には薄いゲート絶縁膜となるシリコン酸化膜9を形成する。これにより、厚いシリコン酸化膜を除去する工程を不要とし、さらにコンタクトホールの形成時においても低耐圧トランジスタと同時にコンタクトホールを形成する加工も行うことができ、工程を簡略化することができると共に、加工性の向上を図ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜の膜厚が異なる複数種のトランジスタを形成する場合であっても、良好な電気的特性を実現し得るフラッシュメモリ等の半導体装置及びその製造方法を提供する。

【解決手段】第1の領域6内に形成された第1の素子分離領域14cと、第2の領域8内に形成された第2の素子分離領域14dと、第1の素子領域16c上に第1のゲート絶縁膜58を介して形成された第1のゲート電極24cを有する第1のトランジスタ66と、第2の素子領域16d上に、第1のゲート絶縁膜58より膜厚の薄い第2のゲート絶縁膜68を介して形成され、第1のゲート電極24cよりゲート長が短い第2のゲート電極24dを有する第2のトランジスタ76とを有し、第2の素子分離領域14dの上面の高さは、第1の素子分離領域14cの上面の高さより高い。

(もっと読む)

半導体デバイスの製造方法およびそれによって得られる半導体デバイス

基板(4)上に半導体デバイスを製造する方法は、基板(4)のメモリ領域(1)に不揮発性メモリ(10)を形成することを含む。基板(4)への不揮発性メモリ形成は、メモリ領域(1)に、浮遊ゲート構造と、制御ゲート構造とを形成することを含む。制御ゲート構造は、浮遊ゲート構造とともに積層型構造に位置する。1以上のゲート材料層は、基板(4)の論理領域(3)に形成される。制御ゲート構造とゲート材料層の形成後、充填材料層(130、130’)は論理領域(3)とメモリ領域(1)に堆積される。論理領域(3)とメモリ領域(1)に位置する充填材料の厚さを、1以上のゲート材料層の表面が少なくとも露出するまで薄くすることによって、充填材料層(130、130’)は除去される。論理デバイスは論理領域(3)に形成され、論理デバイスの形成は、ゲート材料層から論理ゲート構造を形成することを含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】電極間絶縁膜に生じるシームなどの埋込み欠陥の露出を抑制できるようにしてゲート電極間ショートを防止できるようにする。

【解決手段】多結晶シリコン層6bを種として選択成長された選択成長部6cがシリコン酸化膜8、9上に突出して張り出して形成される。その後、多結晶シリコン層6b、6cをシリサイド化することで、金属反応領域を拡大することができ、制御ゲート電極CG(ワード線WL)を低抵抗化することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリ回路のデータ保持特性を向上させる。

【解決手段】半導体基板1Sの主面のメモリセルアレイMRには情報電荷蓄積用の浮遊ゲート電極FGが配置されている。浮遊ゲート電極FGは、キャップ絶縁膜3aと、その上に形成された絶縁膜4aのパターンにより覆われている。さらに、半導体基板1Sの主面上全面には、絶縁膜4aのパターンおよびゲート電極Gを覆うように絶縁膜2aが堆積されている。絶縁膜2aは、プラズマCVD法により成膜された窒化シリコン膜により形成されている。上記絶縁膜4aは、低圧CVD法により成膜された窒化シリコン膜により形成されている。このような絶縁膜4aを設けたことにより、水や水素イオン等が浮遊ゲート電極FGに拡散するのを抑制または防止できるので、フラッシュメモリのデータ保持特性を向上させることができる。

(もっと読む)

不揮発性メモリ及びその製造方法

【課題】不揮発性メモリの性能を向上させつつ製造工程を減少させること。

【解決手段】不揮発性メモリは、メモリセルMCにおいて、N型ウェル3aにP型拡散領域7a、P型拡散領域7b、及びP型拡散領域7cが形成され、P型拡散領域7aとP型拡散領域7bの間のチャネル上にセレクトゲート絶縁膜4aを介してセレクトゲート6aが形成され、P型拡散領域7bとP型拡散領域7cの間のチャネル上にフローティングゲート絶縁膜5を介してフローティングゲート6bが形成されている。周辺回路PTにおいて、N型ウェル3bにP型拡散領域7d及びP型拡散領域7eが形成され、P型拡散領域7dとP型拡散領域7eの間のチャネル上に周辺回路ゲート絶縁膜4bを介し周辺回路ゲート6cが形成されている。フローティングゲート絶縁膜5の膜厚は、セレクトゲート絶縁膜4a及び周辺回路ゲート絶縁膜4bの膜厚よりも厚く構成されている。

(もっと読む)

プログラマブル素子及びそのプログラマブル素子を有する半導体装置の製造方法。

【課題】 プログラム特性の良好なプログラマブル素子及びそのプログラマブル素子を有する半導体装置の製造方法を提供することを目的とする。

【解決手段】 半導体基板100と、半導体基板100表面に離間して形成されたソース/ドレイン層103と、ソース/ドレイン層103間の半導体基板100上に形成されたHfを含有する電荷トラップ膜を有するゲート絶縁膜105と、ゲート絶縁膜105上に形成されたプログラム電位が印加されるゲート電極106を備えることによって、FPGA等のプログラマブルロジックデバイスに使用されるプログラマブル素子のプログラム特性を向上する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】補助パターンでダミーコンタクトが形成されてもゲート電極SGとの間で短絡不良が発生するのを防止できるNAND型フラッシュメモリ装置等の半導体記憶装置を提供する。

【解決手段】ビット線コンタクト4a(CB)の形成時にマスクパターンに補助パターン4b、4cを形成する場合に、メモリセル領域MAから延長して形成される補助パターン4bの端部に位置する補助パターン4cの対応領域について、ビット線コンタクト4a(CB)を形成する領域のスペーサを除去するのと同時にその部分のスペーサを除去する。ゲート電極SLG−SLGの間のパターンニングに余裕を持たせることができ(オフセットを確保することができ)、解像した補助パターン4cの部分でダミーコンタクトホールが形成された場合でも、両脇のゲート電極SLGとの間で短絡不良が発生するのを防止することが出来る。

(もっと読む)

半導体装置

【課題】浮遊ゲートをもち制御ゲートを備えていない不揮発性メモリセルを備えた半導体装置において、その不揮発性メモリセルの読出し特性を飛躍的に改善する。

【解決手段】不揮発性メモリセルは、P型半導体基板1上に形成された書込みメモリゲート酸化膜9及び書込みメモリゲート酸化膜9上に形成された電気的に浮遊状態のポリシリコンからなる書込み浮遊ゲート11をもつPMOS書込みトランジスタと、P型半導体基板1上に形成された読出しメモリゲート酸化膜15及び読出しメモリゲート酸化膜15上に形成された電気的に浮遊状態のポリシリコンからなる読出し浮遊ゲート17をもつNMOS読出しトランジスタを備えている。書込み浮遊ゲート11と読出し浮遊ゲート17は電気的に接続されている。不揮発性メモリセルへの書込みはPMOS書込みトランジスタによって行なわれ、読出しはNMOS読出しトランジスタによって行なわれる。

(もっと読む)

半導体装置の製造方法

【課題】

大型ウエハにおいても均一な丸め込み酸化が行なえ、かつ増加する工程が過度の負担にならない半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法は、シリコン基板の表裏両面上方に窒化シリコン膜、その上にTEOS酸化シリコン膜をCVDで堆積する工程と、表面側TEOS酸化シリコン膜を除去する工程と、TEOS酸化シリコン膜を脱ガスアニールする工程と、表面側窒化シリコン膜をエッチングマスクとしてシリコン基板に素子分離溝をエッチングする工程と、1000℃以上の温度の丸め込み酸化をバッチ処理で行なう工程と、HDP酸化シリコン膜で素子分離溝を埋め込む工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】特性ばらつきが低減され、且つマスク枚数を増やす事なく製造可能なトランジスタを有する半導体装置を提供する。

【解決手段】

半導体装置は、半導体基板1上に形成された第1導電型のウエル3と、ウエル3上に形成された第1のトランジスタ、および第2のトランジスタを備えている。第1のトランジスタは、第1導電型の不純物を含む第1のポケット領域9a、第2導電型の不純物を含む第1のソースおよびドレイン領域11aを有し、第2のトランジスタは、第1導電型の不純物を含む第2のポケット領域9b、第2導電型の不純物を含む第2のソース領域および第2のドレイン領域を有し、アナログ機能を実行する。ソース側及びドレイン側の第2のポケット領域9bに含まれる第1導電型の不純物の濃度は、第1のポケット領域9aに含まれる第1導電型の不純物の濃度よりも低い。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜中に電荷蓄積部を含む不揮発性メモリセルを有する半導体装置において、不揮発性メモリ領域の面積を縮小する。

【解決手段】メモリゲート電極11Aに、局所的に電界が集中するコーナー部11cnを設け、メモリゲート電極11A中の電荷をFNトンネル動作によりゲート絶縁膜2a中の電荷蓄積部に注入する消去方式を用いる。FNトンネルにより消去時の消費電流を低減できるため、メモリモジュールの電源回路面積を低減できる。また、書込みディスターブ耐性を向上できるために、より簡易なメモリアレイ構成を採用してメモリアレイ面積を低減できる。両者の効果を併せてメモリモジュールの面積を大幅に低減し製造コストを低減できる。また、書込み消去の注入電荷中心が一致するため書換え耐性が向上する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】

キャパシタ素子の容量を低下させることなくキャパシタ素子の面積を縮小させると共に、2層ゲート構造と1層ゲート構造を有する半導体記憶装置における1層ゲート構造を有する回路素子のゲート電極と基板間の電気的短絡を防止する。

【解決手段】半導体記憶装置において、キャパシタ素子CPの第3下層電極層33cの上面を凹凸構造してキャパシタ絶縁膜34cを立体的構造にする。同時に、選択ゲートトランジスタSTの第2下層電極層33bの膜厚をメモリセルトランジスタMTの第1下層電極層31aの膜厚より厚くする。その結果、キャパシタ素子CPの素子面積小さくすると共に、選択ゲートトランジスタSTの第2電極間絶縁膜34bの開口部38bから露出される第2素子分離絶縁膜13bの上面は半導体基板21の上面よりも高くなり第2上層電極層37bと半導体基板21との電気的ショートを防止することができる。

(もっと読む)

強誘電体メモリ装置の製造方法

【課題】良好な特性を持つ強誘電体メモリ装置の製造方法を提供する。

【解決手段】MOS型トランジスタ3が、半導体基板1のMOS型トランジスタ領域1bに形成され、層間層4が、MOS型トランジスタ領域1bおよび半導体基板1の強誘電体ゲートFET領域1aに形成され、層間層4の強誘電体ゲートFET領域1aが開口され、強誘電体ゲートFET6が、強誘電体ゲートFET領域1aの開口部5に形成されるようになり、信頼性が向上された強誘電体メモリ装置を製造することができる。

(もっと読む)

半導体装置およびその作製方法

【課題】不揮発性メモリトランジスタの電荷保持特性を向上させる。

【解決手段】半導体基板と導電膜の間には、トンネル絶縁膜として機能する第1絶縁膜、電荷蓄積層、第2絶縁膜が形成されている。電荷蓄積層は2層の窒化シリコン膜でなる。下層の窒化シリコン膜は、窒素ソースガスにNH3を用いてCVD法で形成され、N−H結合を上層よりも多く含む。上層の第2窒化シリコン膜は、窒素ソースガスにN2を用いてCVD法で形成され、Si−H結合を下層よりも多く含む。

(もっと読む)

半導体装置及びその製造方法

【課題】2層ゲート構造と1層ゲート構造を有する半導体記憶装置において1層ゲート構造を有する回路素子のゲート電極と基板間の電気的短絡を防止する。

【解決手段】本発明は、1層ゲート構造を有する選択ゲートトランジスタ及びMOSトランジスタの下層ゲート電極層23b、23cの膜厚をメモリセルトランジスタの浮遊ゲート電極層23aの膜厚より厚くすることにより、第2電極間絶縁層24b、24cに開口部28b、28cを形成する際のエッチングにより下層ゲート電極層23b、23cを貫通しゲート絶縁層22b、22cの上面が露出されることを防止する。従って、後の下層ゲート電極層23b、23cの露出表面に形成された自然酸化膜を除去する際にゲート絶縁層22b、22cが同時に除去されることがなく、選択ゲートトランジスタ及びMOSトランジスタのゲート電極SG、TGと半導体基板21との電気的ショートを防止することができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】微細化に有利な、二重ウェル、及びこの二重ウェルから離れたウェルを備えた不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1導電型の半導体基板1内に形成された第1導電型の第1ウェル10と、第1ウェル10に形成された複数のメモリセルトランジスタQ5−1、Q5−2と、第1ウェル10の側面領域を囲む第1部分7、及び第1ウェル10の下部領域を囲む第2部分9を有し、第1ウェル10を半導体基板1から電気的に分離する第2導電型の第2ウェルと、半導体基板1内に形成された第2導電型の第3ウェル領域5と、を備える。

(もっと読む)

221 - 240 / 403

[ Back to top ]