Fターム[5F092BE27]の内容

Fターム[5F092BE27]に分類される特許

121 - 140 / 322

磁気トンネル接合デバイス

磁気トンネル接合デバイスを製造するおよび使用するシステムおよび方法が開示される。特定の実施形態において、磁気トンネル接合デバイスが、第1自由層と第2自由層とを含む。また、磁気トンネル接合が、スピントルク強化層を含む。磁気トンネル接合が、第1自由層と第2自由層との間にスペーサー層をさらに含み、前記スペーサー層が、1つの材料を含み、第1自由層と第2自由層との間の交換結合を実質的に抑制する厚さを有する。第1自由層と第2自由層とが、静磁的に結合される。  (もっと読む)

(もっと読む)

磁気抵抗素子及び磁気メモリ

【課題】熱安定性と低消費電流のスピン注入書き込み方式の磁気抵抗素子を提案する。

【解決手段】本発明の例に係わる磁気抵抗素子は、膜面垂直方向に磁化容易軸を有する磁化方向が可変の第1磁性層3と、膜面垂直方向に磁化容易軸を有する磁化方向が不変の第2磁性層2と、第1磁性層3と第2磁性層2との間に設けられる第1非磁性層4とを含む。第1磁性層3は、CoとPd、又は、CoとPtが原子稠密面に対して交互に積層されるCoPd合金、又は、CoPt合金を有し、c軸が膜面垂直方向を向く強磁性体から構成される。第1磁性層3の磁化方向は、第1磁性層3、第1非磁性層4及び第2磁性層2を貫く双方向電流により変化する。

(もっと読む)

磁気メモリ素子

【課題】磁気メモリ素子を提供する。

【解決手段】本発明の磁気メモリ素子は、基板上のトンネルバリア、トンネルバリアの一面と接する第1接合磁性層、第1接合磁性層によってトンネルバリアと離隔される第1垂直磁性層、トンネルバリアの他の面と接する第2接合磁性層、第2接合磁性層によってトンネルバリアと離隔される第2垂直磁性層、及び第1接合磁性層と第1垂直磁性層との間の非磁性層を含む。

(もっと読む)

MTJナノピラー構造およびその形成方法

【課題】 臨界反転電流密度JCOを最小限に抑えつつ、熱安定性、書き込み電圧、読み出し電圧、および保磁力Hcが64MbのSTT-RAMの設計要求を満たすMTJナノピラー構造を得る。

【解決手段】 自然酸化法を用いて、酸素界面活性層を含むMgOトンネルバリア層を形成する。フリー層40は、FL1層50/NCC層51/FL2層52なる構造を有する。NCC層51は、SiOマトリクス51b中に形成されたRM粒子(RはCo、Fe、Ni、MはSi、Al等の金属)からなるナノ導電チャネル51aを含む。NCC層51の厚さは、RM粒子の最小粒径前後の厚さに保たれ、FL1層50とFL2層52との間の距離を埋めるのに十分な直径を有する。

(もっと読む)

高速スピン移動トルク書き込み手順を備えた磁気素子

【課題】 高速スピン移動トルク書き込み手順を備えた磁気素子を提供する。

【解決手段】 固定磁化方向を有する基準層と、書き込み電流を磁気トンネル接合部に通過させることによって、基準層の磁化方向に対して調整可能な磁化方向を有する第1の記憶層と、前記基準層および第1の記憶層間に配置された絶縁層と、を含む磁気トンネル接合部であって、磁気トンネル接合部が、書き込み電流のスピンを、基準層の磁化方向に垂直に配向されるように偏極する偏極装置をさらに備えることを特徴とし、前記第1の記憶層が、磁化の切り替え時間が1ns〜100ns間に含まれる範囲になるような減衰定数を有する磁気トンネル接合部。改善された書き込み速度および従来のメモリ装置より低い電力消費を有する、開示の磁気トンネル接合部から形成された複数の磁気素子を備える磁気メモリ素子。

(もっと読む)

二重障壁強磁性トンネル接合および磁気デバイス

【課題】室温で1000%以上のTMR効果が得られる低抵抗の二重障壁強磁性トンネル接合と、この二重障壁強磁性トンネル接合を用いた磁気デバイスを提供する。

【解決手段】下地層/強磁性層1/絶縁層1/強磁性層2/絶縁層2/強磁性層3/上部層の構造が基板材料上に積層され、下地層により強磁性層1の磁化が、上部層により強磁性層3の磁化が固定され、強磁性層2が磁化自由層として機能する構造の二重障壁強磁性トンネル接合において、強磁性層2をCoFeB合金とし、かつ、その厚さを0.5〜1.4nmに薄膜化し、絶縁層1および2をMgOとし、250〜400℃程度の熱処理プロセスを経ることで低抵抗、かつ、1000%を超える巨大なTMR比が得られる。

(もっと読む)

磁気抵抗装置およびその製造方法

【課題】高い巨大磁気抵抗(GMR)値と中程度に低い抵抗面積積(RA)とを有する磁気抵抗装置を提供する。

【解決手段】この装置は、第1の磁性層と、第2の磁性層と、第1の磁性層と第2の磁性層との間に位置する電流狭窄(CCP)スペーサ層とを含む。スペーサ層は、第1の磁性層と第2の磁性層との間に延在する銅電流狭窄を酸化マグネシウムの母材中に含む。スペーサ層は、銅と酸化マグネシウムとの混合物によって形成され、この混合物は、銅電流狭窄を酸化マグネシウム母材内に形成するために熱処理される。

(もっと読む)

電流誘起スピン−運動量移動に基づく高速低電力磁気デバイス

スピン偏極電流を使用してメモリセルの磁気デバイスにおける磁気領域の磁化方向及び/又はヘリシティを制御してスイッチングする高速かつ低電力の方法。磁気デバイスは、固定の磁気ヘリシティ及び/又は磁化方向を有する基準磁化層と、可変の磁気ヘリシティ及び/又は磁化方向を有する自由磁化層とを含む。固定磁化層及び自由磁化層は、非磁化層により分離されることが好ましい。固定及び自由磁化層は、層法線に対して実質的に非ゼロ角度の磁化方向を有することができる。デバイスに電流を印加してトルクを誘起することができ、これは、デバイスの磁気状態を変更し、そのためにそれは情報を書き込むための磁気メモリとして作用することができる。デバイスの磁気状態に依存する抵抗が測定されてデバイスに格納された情報を読み出す。 (もっと読む)

複合磁気シールドを有する磁気センサ

磁気抵抗リーダは、第1の磁気シールド素子と、第2の磁気シールド素子と、第1の磁気シールド素子を第2の磁気シールド素子から分離する磁気抵抗センサ積層体とを含む。第1の磁気シールド素子は、グレイン成長抑制層によって分離される2つの強磁性異方性層を含む。  (もっと読む)

(もっと読む)

メモリ

【課題】同じ構成の記憶素子を用いて、ROMとRAMとを共に実現することができるメモリを提供する。

【解決手段】磁化M1の向きが反転可能な磁化自由層18と、絶縁体からなるトンネルバリア層17と、磁化自由層18に対してトンネルバリア層17を介して配置され、磁化M14,M16の向きが固定された磁化固定層13とを含む、トンネル磁気抵抗効果素子から構成された記憶素子1を複数個含み、記憶素子1の磁化自由層18の磁化M1の向きによって情報が記録される、ランダムアクセスメモリ領域と、記憶素子1のトンネルバリア層17の絶縁破壊の有無によって情報が記録される、リードオンリーメモリ領域とを含むメモリを構成する。

(もっと読む)

スピントロニック素子のスピンバルブ構造およびその形成方法、ボトム型スピンバルブ構造、ならびにマイクロ波アシスト磁気記録用スピントロニック素子

【課題】スピン消極を引き起こすことなく、また、加熱処理を必要とせずに、[Co/Ni]x積層構造の十分な垂直磁気異方性を確保する。

【解決手段】このスピンバルブ構造は、上部の[Co/Ni]x積層リファレンス層23の垂直磁気異方性を向上させるため、Ta層と、fcc[111]またはhcp[001]構造を有する金属層とを含む複合シード層22を備える。[Co/Ni]x積層リファレンス層23は、CoとNiとの界面の損傷を防止し、これにより垂直磁気異方性を保つため、低いパワーと高圧のアルゴンガスとを用いたプロセスにより成膜する。その結果、薄いシード層を用いることが可能となる。垂直磁気異方性は220℃の温度で10時間にわたって熱処理を行った後であっても維持される。この構造は、CPP−GMR素子やCPP−TMR素子に適用できるほか、スピントランスファー発振器やスピントランスファーMRAMにも適用できる。

(もっと読む)

スピン注入構造及びそれを用いたスピン伝導デバイス

【課題】従来のスピン注入構造において、MgOはSi上にエピタキシャル成長しないため、格子不整合によりそこを通過する偏極したスピンが乱されて、偏極スピンが減少するため、良好な特性を維持可能なスピン注入構造を提供する。

【解決手段】Siからなるチャンネル層7と、チャンネル層7上に形成された強磁性体からなる磁化固定層12Bと、チャンネル層7と磁化固定層12Bとの間に介在する第1トンネル障壁8Bとを備えている。さらに、第1トンネル障壁8Bは、チャンネル層7側の領域に位置する非晶質MgO層と、磁化固定層12B側の領域に位置する単結晶MgO層とを有している。第2トンネル障壁8Cも同様に、チャンネル層7側の領域に位置する非晶質MgO層と、磁化固定層12C側の領域に位置する単結晶MgO層とを有している。

(もっと読む)

磁気抵抗素子および磁気メモリ

【課題】熱的に安定であると同時に低電流の磁化反転を可能とするスピン注入書き込み方式用の磁気抵抗素子およびそれを用いた磁気メモリを提供する。

【解決手段】下地層12と、下地層上に設けられ膜面に垂直方向に磁化容易軸を有する磁化方向が可変の第1の磁性層13と、第1の磁性層上に設けられた第1の非磁性層15と、第1の非磁性層上に設けられ膜面に垂直方向に磁化容易軸を有する磁化方向が固定された第2の磁性層17と、を備え、第1の磁性層は、DO22構造またはL10構造を有しc軸が膜面に垂直方向を向くフェリ磁性体層を含み、第1の磁性層と第1の非磁性層と第2の磁性層とを貫く双方向電流によって、第1の磁性層の磁化方向が可変となる。

(もっと読む)

スピントルク移動磁気抵抗ランダムアクセスメモリ(STT‐MRAM)のソースローディング効果の低減

STT‐MRAMのソースローディング効果を低減するシステム及び方法が開示される。特定の実施形態では、本方法は、メモリセルの安定動作を可能にする磁気トンネル接合(MTJ)構造のスイッチング電流比を決定することを含む。メモリセルは、アクセストランジスタに直列に結合されたMTJ構造を含む。本方法は、MTJ構造の自由層に入射するオフセット磁場を変更することも含む。変更されたオフセット磁場によって、MTJ構造がそのスイッチング電流比を示すようにする。  (もっと読む)

(もっと読む)

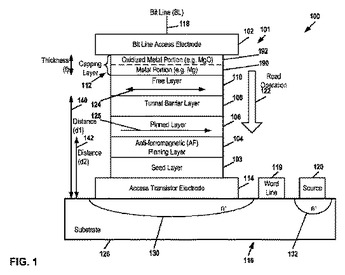

磁気トンネル接合デバイスおよび製造

磁気トンネル接合デバイスおよび製造方法が開示される。特定の実施形態では、方法は、磁気トンネル接合構造のフリー層(110)上にキャップ材料(112)を堆積させてキャップ層を形成するステップと、キャップ材料の一部分を酸化して酸化された材料の層を形成するステップを含む。  (もっと読む)

(もっと読む)

FePt系磁性層を備える積層体構造物およびそれを用いた磁気抵抗効果素子

【課題】 300℃以下の温度において、L10構造FePt規則合金が得られるFePt系磁性層を備える積層体構造物を提案する。

【解決手段】 積層体構造物は、アモルファス状態のTa層と、このTa層の上に形成された酸化亜鉛(ZnO)または酸化マグネシウム(MgO)からなる金属酸化物層と、この金属酸化物層の上に形成されたFePt系磁性層と、を有して構成される。

(もっと読む)

トンネル型磁気検出素子

【課題】 特に、抵抗変化率(ΔR/R)を増大させることが可能なトンネル型磁気検出素子を提供することを目的としている。

【解決手段】 第1軟磁性層13と第2軟磁性層15との間に、Ti、Mg、Ir−Mn、RuあるいはPtのうち少なくともいずれか1種で形成された金属挿入層14が挿入されている。前記第1軟磁性層13と前記第2軟磁性層15は、磁気的に結合されて同一方向に磁化されている。前記第1軟磁性層13と絶縁障壁層5との間にはエンハンス層12が形成されている。これにより、絶縁障壁層5がMg−Oで形成されたトンネル型磁気抵抗効果素子において、従来に比べて、抵抗変化率(ΔR/R)を増大させることが可能である。

(もっと読む)

トンネル型磁気検出素子

【課題】 特に、フリー磁性層内にTa層を挿入した形態に比べて、上下シールド層間のギャップ長(GL)を小さくしつつ抵抗変化率(ΔR/R)を増大させることが可能なトンネル型磁気検出素子を提供することを目的としている。

【解決手段】 フリー磁性層6は、例えば、Mg−Ti−Oから成る絶縁障壁層5上に、下から、エンハンス層12、第1軟磁性層13、非磁性金属層14、第2軟磁性層15の順に積層されている。前記エンハンス層12は例えばCo−Feで、第1軟磁性層13及び第2軟磁性層15は例えばNi−Feで、非磁性金属層14は例えばTiで形成される。前記エンハンス層12の平均膜厚と前記第1軟磁性層13の平均膜厚を足した総合膜厚T5は19Å以上28Å以下で形成される。これにより従来に比べて安定して高い抵抗変化率(ΔR/R)を得ることが出来る。

(もっと読む)

トンネル型磁気検出素子

【課題】 特に、フリー磁性層の磁歪λsの増加を小さく抑えつつ、従来に比べて抵抗変化率(ΔR/R)を増大させることが可能なトンネル型磁気検出素子を提供することを目的としている。

【解決手段】 絶縁障壁層5は、Mg−Oで形成され、前記フリー磁性層6は、下からエンハンス層12、第1軟磁性層13、Co−Ta層14及び第2軟磁性層15の順に積層されている。このように軟磁性層13,15間にCo−Ta層14を挿入した構成とすることで、フリー磁性層6の磁歪λsの増加を小さく抑えつつ、従来に比べて抵抗変化率(ΔR/R)を増大させることが可能である。

(もっと読む)

磁気抵抗効果素子およびその形成方法

【課題】低保磁力、低磁歪および低RA値を確保しつつ、高いTMR比を得る。

【解決手段】フリー層18は、トンネルバリア層17の側から第1の強磁性層、挿入層および第2の強磁性層が順に積層された複合構造を有する。第1の強磁性層は、CoFe合金、または、そのCoFe合金にNiなどを添加してなる合金を含み、かつ、正の磁歪定数を有する。挿入層は、Fe,CoおよびNiから選択される少なくとも一種の磁性元素と、Ta,Ti,W,Zr,Hf,Nb,Mo,V,MgおよびCrから選択される少なくとも一種の非磁性元素とを含む。第2の強磁性層は、CoFeやNiFeなどからなり、負の磁歪定数を有する。

(もっと読む)

121 - 140 / 322

[ Back to top ]