Fターム[5F101BH04]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | 絶縁膜形成 (1,494) | トンネル絶縁膜形成 (136)

Fターム[5F101BH04]に分類される特許

1 - 20 / 136

不揮発性半導体記憶装置

【課題】円筒型MONOSメモリセルで電荷保持特性の向上を図る。

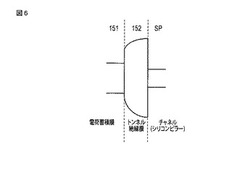

【解決手段】不揮発性半導体記憶装置は、半導体基板と、前記半導体基板上に形成され、上面から下面まで達する円筒状の貫通ホールを有するコントロールゲートCGと、前記貫通ホール内における前記コントロールゲートの側面上に形成されたブロック絶縁膜150と、前記貫通ホール内における前記ブロック絶縁膜の側面上に形成された電荷蓄積膜151と、前記貫通ホール内における前記電荷蓄積膜の側面上に形成されたトンネル絶縁膜152と、前記貫通ホール内における前記トンネル絶縁膜の側面上に形成された半導体層SPと、を具備し、前記トンネル絶縁膜は、SiO2を母材とし、添加することで前記母材のバンドギャップを低下させる元素を含む第1絶縁膜を含み、前記元素の濃度および濃度勾配は、前記半導体層側から前記電荷蓄積膜側に向かって単調に増加する。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

熱アシスト誘電体電荷トラップメモリ

【課題】

誘電体電荷トラップメモリの動作速度及び/又は耐久性を向上させる技術を提供する。

【解決手段】

メモリデバイスは、ワードライン及びビットラインを含む誘電体電荷トラップ構造メモリセルのアレイを含む。該アレイに、読み出し、プログラム及び消去の動作を制御するように構成された制御回路が結合される。コントローラは、該アレイのメモリセル内の誘電体電荷トラップ構造を熱アニールする支援回路を備えるように構成される。熱アニールのための熱を誘起するために、ワードラインドライバ及び前記ワードライン終端回路を用いて、ワードラインに電流を誘起することができる。熱アニールは、サイクルダメージからの回復のために、通常動作とインターリーブされて適用されることが可能である。また、熱アニールは、消去のようなミッション機能中に適用されることもでき、それにより該機能の性能を向上させ得る。

(もっと読む)

ダイオードストラッピングを備えた熱アシストフラッシュメモリ

【課題】フラッシュメモリの動作速度及び耐久性を向上させる技術の提供。

【解決手段】メモリが、行及び列を含むメモリセルのアレイを有している。該メモリは、アレイ内の単数又は複数のワード線上の第1の離隔位置のセットに第1のバイアス電圧を印加するとともに、単数又は複数のワード線上の第2の離隔位置のセットに第1のバイアス電圧とは異なる第2のバイアス電圧を印加する、ワード線に結合された回路部を有し、第1の離隔位置のセットにおける位置は、第2の離隔位置のセットの位置の間に介在しており、それにより、第1の離隔位置のセットにおける位置と第2の離隔位置のセットにおける位置との間に、単数又は複数のワード線の加熱をもたらす電流の流れが誘導される。

(もっと読む)

半導体装置

【課題】抵抗素子を有する半導体装置に関し、集積度を低下することなく低消費電力化と高い回路精度とを実現しうる半導体装置を提供する。

【解決手段】半導体材料により形成された複数の抵抗素子と、複数の抵抗素子の近傍に配置された加熱用抵抗素子と、対向する2つの接続ノード間に加熱用抵抗素子が接続され、対向する他の2つの接続ノード間に電源線が接続された抵抗ブリッジ回路とを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】埋め込みビットライン型不揮発メモリの微細化に適した製造方法を提供し、かつコンタクトの位置ずれに起因するビットライン間ショートを生じ難い構造を提供する。

【解決手段】導電体膜が埋め込まれたシャロートレンチ溝内にビットライン拡散層を設けてSONOS構造セルとする。これにより、ビットライン拡散層の半導体基板主面上での面積を大きくせずにビットライン拡散層の抵抗を低くすることができ、セル面積を増大させることなく安定した電気的特性の半導体記憶装置が得られる。また、Si3N4のサイドウォールを設けてイオン注入することでビットラインを形成する。これにより、メモリセルの微細化が可能となる。

(もっと読む)

半導体装置の製造方法

【課題】 セレクトゲート部におけるゲート閾値電圧が安定した半導体装置の製造方法を提供する。

【解決手段】 実施形態に係る半導体装置の製造方法では、メモリセル部及びセレクトゲート部が形成される。半導体基板上にトンネル絶縁膜が形成され、前記トンネル絶縁膜上に電荷蓄積層が形成される。前記電荷蓄積層、前記トンネル絶縁膜、及び前記半導体基板のエッチングにより素子分離溝部が形成され、前記電荷蓄積層の側面に接するように前記素子分離溝部に素子分離絶縁膜が埋め込まれる。前記電荷蓄積層及び前記素子分離絶縁膜上に電極間絶縁膜が形成され、前記セレクトゲート部において、前記電極間絶縁膜がエッチングされる。前記電極間絶縁膜を覆い、前記電荷蓄積層に接続するシリコン膜が形成され、前記シリコン膜上に金属膜が形成される。熱処理により、前記セレクトゲート部において、前記トンネル絶縁膜に接する前記電荷蓄積層がシリサイド化される。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置の提供。

【解決手段】酸化物半導体材料を用いたトランジスタ162と、酸化物半導体以外の半導体材料を用いたトランジスタ160を組み合わせて用いることにより、書き込み回数にも制限が無く、長期間にわたる情報の保持ができる、新たな構造の半導体装置を実現することができる。さらに、酸化物半導体以外の半導体材料を用いたトランジスタと酸化物半導体材料を用いたトランジスタとを接続する接続電極130bを、当該接続電極と接続する酸化物半導体以外の半導体材料を用いたトランジスタの電極129より小さくすることにより、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることができる。

(もっと読む)

プリント不揮発性メモリ

【課題】低コストで高スループットなプリント技術を使用した不揮発性メモリセルを提供する。

【解決手段】同一水平レベルにおいて所定の距離で離間している第1及び第2の半導体アイランドであって、第1の半導体アイランド2が制御ゲートを構成し、第2の半導体アイランド3がソース端子及びドレイン端子を構成する、当該第1及び第2の半導体アイランドと、第1の半導体アイランド2の少なくとも一部の上のゲート誘電体層4と、第2半導体アイランドの少なくとも一部の上のトンネリング誘電体層5と、ゲート誘電体層4とトンネリング誘電体層5の少なくとも一部の上のフローティングゲート7と、制御ゲート2並びにソース端子及びドレイン端子に電気的に接触する金属層と、を備える。一つの効果的な実施形態では、不揮発性メモリセルを、「全プリント」加工技術を使用して製造することができる。

(もっと読む)

シリコン酸化膜の形成方法、シリコン窒化膜の形成方法、シリコン酸窒化膜の形成方法

【課題】ポリシリコン上において高品質な絶縁膜を形成できる絶縁膜の形成方法を提供する

【解決手段】シリコン酸化膜の形成方法は、基板上にポリシリコン膜を堆積する工程と、

前記ポリシリコン膜の表面を、酸素を含むガスとKrガスを主体とする不活性ガスとよりなる混合ガスにマイクロ波によりプラズマを励起することで形成される原子状酸素O*に曝すことにより、前記ポリシリコン膜の表面にシリコン酸化膜を形成する工程とよりなる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】素子特性の安定性を向上できる半導体集積回路装置の製造方法を提供する。

【解決手段】半導体集積回路装置の製造方法は、シリコン基板101の表面に第1の酸化膜103を形成する工程と、周辺回路領域A2内にあるシリコン基板101の所定箇所に不純物を注入し、この所定箇所上の第1の酸化膜103を除去し、この所定箇所上に第2の酸化膜112を形成する工程と、メモリセル領域A1内の第1の酸化膜103にトンネルウィンドウを形成し、このトンネルウィンドウ内で露出したシリコン基板101上にトンネル酸化膜116を形成し、トンネル酸化膜116を覆うメモリセル用ポリシリコン膜118を形成する工程と、第2の酸化膜112を形成する前記工程の後にメモリセル用ポリシリコン膜118上にONO膜119を形成する工程とを有する。

(もっと読む)

半導体記憶装置

【課題】動作速度が高い半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、それぞれ複数の絶縁膜及び電極膜が交互に積層され、前記絶縁膜及び前記電極膜の積層方向に延びる貫通ホールが形成された積層体と、前記貫通ホールの内面上に設けられたブロック層と、前記ブロック層に囲まれた電荷蓄積層と、前記電荷蓄積層に囲まれたトンネル層と、前記トンネル層に囲まれた半導体ピラーと、を備える。そして、前記トンネル層における前記半導体ピラー側の部分の誘電率は、前記トンネル層における前記電荷蓄積層側の部分の誘電率よりも高い。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 セル部のブロック絶縁膜の誘電率を低下させることなく、セル部のブロック絶縁膜を分断するセル間における絶縁膜中の欠陥を低減し、電荷保持特性の劣化を抑制する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】 実施形態の不揮発性半導体記憶装置においては、半導体基板上にトンネル絶縁膜、前記トンネル絶縁膜上に電荷蓄積層、前記電荷蓄積層上にブロック絶縁膜が設けられる。前記半導体基板に設けられた素子分離溝部に埋め込まれ、底面が前記半導体基板と前記トンネル絶縁膜の接する面の高さよりも低く、かつ上面が前記電荷蓄積層および前記ブロック絶縁膜の接する面の高さよりも低い第1の素子分離絶縁膜が設けられる。前記第1の素子分離絶縁膜上に形成され、前記ブロック絶縁膜の側面と接して前記ブロック絶縁膜上面まで突出し、かつSi濃度が前記ブロック絶縁膜よりも高い第2の素子分離絶縁膜が設けられる。

(もっと読む)

メモリストリングにダイオードを有する3次元アレイのメモリアーキテクチャ

【課題】信頼できる非常に小型の記憶素子を含む、3次元集積回路メモリ用の構造を低い製造コストで提供すること。

【解決手段】3次元メモリデバイスは、絶縁材料によって分離され、復号化回路を介してセンスアンプに結合可能なストリングとして配置された複数の隆起した形状スタック含む。ダイオードは、ストリングのストリング選択端部又は共通ソース選択端部のどちらか一方においてビット線構造に接続される。導電材料の帯片は、隆起した形状のスタックのサイドに側面を有する。ワード線として配列された複数の導電線は、行デコーダに結合することができ、複数の隆起した形状のスタックの上で直交して延びる。記憶素子は、スタック上の電導性帯片の側面と導電線との間の交点における界面領域の多層アレイに設けられる。

(もっと読む)

不揮発性半導体記憶装置

【課題】ゲート電極間絶縁膜のリーク電流を抑制し、電気的信頼性を向上した不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板上に行列状に形成された複数のメモリ素子と、同一列方向のメモリ素子に選択的に接続される複数のビット線と、同一行方向のメモリ素子に接続される複数のワード線とを具備し、各メモリ素子は、半導体基板上に順次形成された第1のゲート絶縁膜、電荷蓄積層、第2のゲート絶縁膜、制御電極と、電荷蓄積層の対向する側面に沿って、前記シリコン基板上面に形成された1対の不純物注入層とを具備し、ビット線に垂直な方向に沿った断面における電荷蓄積層の上部コーナー部が曲面を有し、上部コーナー部が前記第1のゲート絶縁膜の上方にある。

(もっと読む)

不揮発性記憶素子

【課題】本発明は、中間絶縁膜、半導体層、及びトンネル絶縁膜のうちの少なくとも1つが酸化ガリウムを含まない場合に比べて、動作安定性の向上した不揮発性記憶素子を提供する。

【解決手段】不揮発性記憶素子10は、基板30上と、ソース電極34S及びドレイン電極34Dと、半導体層36と、トンネル絶縁膜38と、電荷蓄積層40と、中間絶縁膜42と、ゲート電極44Gと、を備えており、半導体層36、トンネル絶縁膜38、及び中間絶縁膜42が、酸化ガリウムを含んでいる。

(もっと読む)

半導体集積回路装置

【課題】ゲート絶縁膜の厚さが異なる複数種類の電界効果トランジスタを有する半導体集積回路装置の信頼性を高める。

【解決手段】第1の電界効果トランジスタQ3及び第2の電界効果トランジスタQ4は埋込絶縁膜25によって分離され、ゲート絶縁膜31,32は各々熱酸化膜27、30と堆積膜27,28,29が積層され、第1の電界効果トランジスタの熱酸化膜は第2の電界効果トランジスタの熱酸化膜より厚く、各トランジスタの堆積膜は、各々各トランジスタの熱酸化膜よりも厚く構成され、第1の電界効果トランジスタのゲート電極は、ゲート幅方向における端部が埋込絶縁膜上に引き出され、かつ端部と埋込絶縁膜との間に第1の電界効果トランジスタの堆積膜が設けられ、第2の電界効果トランジスタのゲート電極は、ゲート幅方向における端部が埋込絶縁膜上に引き出され、かつ前記端部と埋込絶縁膜との間に第2の電界効果トランジスタの堆積膜が設けられる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】寄生容量を抑制した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】第1方向に沿って交互に積層された複数の電極膜WLと複数の電極間絶縁膜14とを有する積層構造体MLと、積層構造体MLを第1方向に貫通する半導体ピラーSPと、複数の電極膜WLのそれぞれと半導体ピラーSPとの間に設けられた電荷蓄積膜48と、電荷蓄積膜48と半導体ピラーSPとの間に設けられた内側絶縁膜42と、電極膜WLのそれぞれと電荷蓄積膜48との間に設けられた外側絶縁膜43と、を有するメモリ部MUと、メモリ部MUと、第1方向に対して直交する第2方向に沿って併設され、積層構造体MLの第1方向に沿った少なくとも一つの電極膜WLの位置と同じ位置に絶縁部50と、を有する非メモリ部PR10とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】良質な特性を有する半導体装置の製造方法を提供する。

【解決手段】制御ゲート電極202の表面に絶縁膜203を形成する工程と、絶縁膜203の表面に電荷蓄積層204を形成する工程と、電荷蓄積層204の表面にトンネル絶縁膜205を形成する工程と、トンネル絶縁膜205の表面にシリコン層206を形成する工程と、シリコン層206を形成した後、熱処理を行ってトンネル絶縁膜205及びシリコン層206の境界面近傍に存在する酸素とシリコンとを反応させる工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】高速処理が可能で、かつ電荷保持特性の高いチャージトラップ型フラッシュメモリを得ることができる半導体装置の製造方法を提供する。

【解決手段】基板100の表面を酸化してシリコン酸化膜140を形成するシリコン酸化膜形成工程と、プラズマ状態の窒素含有ガスをシリコン酸化膜140に供給してシリコン酸化膜140の表面近傍に窒素ピーク濃度が20原子%以上60原子%以下の窒化層141を形成する窒化層形成工程と、窒化層141が形成されたシリコン酸化膜140上に電荷保持膜150を形成する電荷保持膜形成工程と、電荷保持膜150上に、絶縁膜160と電極膜170を形成する電極膜形成工程とを有する。

(もっと読む)

1 - 20 / 136

[ Back to top ]