Fターム[5F101BH09]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | イオン注入 (487)

Fターム[5F101BH09]の下位に属するFターム

イオン注入によるトラップ形成 (10)

Fターム[5F101BH09]に分類される特許

141 - 160 / 477

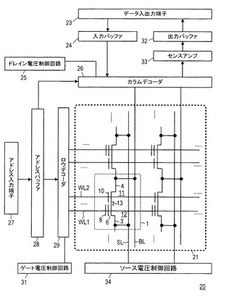

不揮発性半導体記憶装置並びにその駆動方法

【課題】 注入効率が高く、書き込まれた情報が安定的に保持される不揮発性半導体記憶装置並びにその駆動方法を提供する。

【解決手段】 メモリセル1は、N型基板2上に、P型の不純物拡散領域3,4を離間して形成し、両領域間に係る前記基板上において、不純物拡散領域3に隣接して形成された第一積層部15と、不純物拡散領域4に隣接し前記第一積層部15と離間して形成された第二積層部16を備える。メモリセル1に対する書き込み処理時において、第一ゲート電極8に対し、同ゲート電極下方に位置する基板2の表面が弱反転状態となる条件の第一負電圧を印加し、第二ゲート電極10に対し、前記第一負電圧よりも絶対値の大きい第二負電圧を印加し、不純物拡散領域4に対して前記第一負電圧よりも絶対値の大きいドレイン電圧を印加し、不純物拡散領域3に対して、前記ドレイン電圧よりも電位の高いソース電圧をそれぞれ印加する。

(もっと読む)

不揮発性メモリー装置

【課題】MONOS型不揮発性メモリーの消去を行う場合には、FN電流を用いた消去法を用いる場合でも、バンド間トンネリングホットホールを用いた消去を行う場合においても、負電源を用いることが必要となる。負電源を用いるためには別途電気的に分離できるよう配線パターンを設計する必要があり、配線パターンに制約が加わるという課題がある。

【解決手段】接合深さとして、10nm以上500nm以下の値となるようドレイン領域203D、ソース領域203Sを形成した。ドレイン領域203D、ソース領域203Sでの電界強度が大きくとれることから、バンド間トンネリングホットホールをゲート電極206を接地し、ドレイン領域203Dに5[V]程度の電位を供給することで発生させることができ、負電源を用いることなく消去を行うことが可能となる。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】信頼性の高い不揮発性メモリと周辺回路を含む半導体装置を提供する。

【解決手段】不揮発性半導体記憶装置の製造方法は、周辺回路領域では、フローティングゲート電極層p1sは除去し、コントロール電極層p2はパターニングしない状態で、不揮発性メモリの積層ゲート電極を形成し、サイドウォ−ルSW1を形成し、周辺回路領域では、コントロール電極層PGの側壁上に第1冗長絶縁性サイドウォ−ルSNPを形成し、コントロールゲート電極層PGをパターニングして単層ゲート電極PGを形成すると共に、第1冗長絶縁性サイドウォ−ルSNPに隣接する部分を残す。

(もっと読む)

不揮発性メモリー装置および不揮発性メモリー装置の製造方法

【課題】MONOS型不揮発性メモリー素子の消去を行う場合として、バンド間トンネリングホットホールによる消去方法を用いることが好適である。この場合、消去できる領域がドレイン領域近傍に制限されるため、FN電流を用いた消去動作よりも消去できる領域が狭く、特にソース領域近傍側の電荷を消去しきれないという課題があり、特に製造工程で帯電したソース領域近傍の電荷を消去することが困難になるという課題がある。

【解決手段】ソース領域203Sに5V程度の電圧をかけ、ドレイン領域203D、ゲート電極206を接地する動作と、ドレイン領域203Dに5V程度の電圧をかけ、ソース領域203S、ゲート電極206を接地する動作とを行う。ソース領域203S近傍に位置するゲート絶縁層204の電荷も消去することが可能となり、製造工程で帯電したソース領域近傍の電荷を消去することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセルの隣り合うワード線の間のショートの発生を防止し、高歩留まりを可能とする構造を備えた半導体装置を提供する。

【解決手段】半導体装置は、複数の拡散ビット線108と、複数のワード線114と、電荷保持機能を有する複数のトラップ膜102と、複数のビット線絶縁膜110とを備える。複数のワード線114は、複数の多結晶シリコン膜103と、該複数の多結晶シリコン103と電気的に接続する多結晶シリコン膜112とからなる。基板101の表面から複数のビット線絶縁膜110の上面までの高さは、基板101の表面から複数の多結晶シリコン膜103の上面までの高さよりも低い。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】占有面積を縮小させた揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】メモリストリングMSは、基板Baに対して垂直方向に延びる一対の柱状部38a、及び一対の柱状部38aの下端を連結させるように形成された連結部38bを有するU字状半導体層38と、U字状半導体層38の側面を取り囲むように形成された電荷蓄積層37bと、電荷蓄積層27bの側面を取り囲むように形成された第1〜第4ワード線導電層32a〜32dとを備える。柱状部38aは、カラム方向に第1ピッチ3Fをもって整列し、且つロウ方向に第2ピッチ2Fcosθをもって千鳥状に配列され、第1〜第4ワード線導電層32a〜32dは、カラム方向に第1ピッチ3Fをもって配列され、ロウ方向においては柱状部38aの千鳥状の配列に沿って波状に曲がりながら延びるように構成されている。

(もっと読む)

レジスト組成物及びそれを用いた半導体装置の製造方法

【課題】レジストの解像度を損うことなく、レジストの感度を向上させることができるレジスト組成物及び該レジスト組成物を用いた半導体装置の製造方法の提供。

【解決手段】本発明のレジスト組成物は、金属塩、樹脂、及び溶剤を含むことを特徴とする。金属塩がアルカリ金属塩及びアルカリ土類金属塩のいずれかである態様、金属塩がセシウム塩である態様、金属塩の含有量が、樹脂に対し、5質量%〜50質量%である態様、などが好ましい。

(もっと読む)

半導体記憶装置の製造方法

【課題】GIDLが抑制できるメモリセルトランジスタと選択トランジスタからなるフラッシュEEPROMを製造する。

【解決手段】半導体基板の表面に対して斜め方向且つメモリセルトランジスタCT及び選択トランジスタSTのゲート長方向に対して平行する方向に不純物を導入し、水平方向に所定角度回転させた半導体基板の表面に対して斜め方向且つメモリセルトランジスタ及び選択トランジスタのゲート長方向に対して交差する方向に不純物を導入して、メモリセルトランジスタのゲート電極と選択トランジスタのゲート電極との間の基板表面における不純物濃度が、メモリセルトランジスタのゲート電極同士の間の基板表面における不純物濃度及び選択トランジスタのゲート電極同士の間の基板表面における不純物濃度よりも低くなるようにメモリセルトランジスタ及び選択トランジスタのソース、ドレイン拡散層を形成する。

(もっと読む)

半導体素子及びその製造方法

【課題】本発明は、半導体素子及びその製造方法を提供するためのものである。

【解決手段】本発明に従う半導体素子は、半導体基板10上に形成された第1絶縁膜パターン(第1絶縁膜21)、上記第1絶縁膜パターン上に形成され、フルオリンを含む第2絶縁膜パターン(第2絶縁膜22)、上記第2絶縁膜パターン上に形成された第3絶縁膜パターン(第3絶縁膜23)、及び上記第3絶縁膜23パターン上に形成されたポリシリコン膜パターン(ポリシリコン膜30)を含む。本発明は、フラッシュメモリ素子でデータが格納される窒化膜にフルオリンを注入してキャパシタ特性に影響を与えず、且つデータリテンション及び信頼性を向上させることができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】コンタクトプラグとゲート電極との間のショートおよび/またはコンタクトプラグとシリコンピラーとの間のショートを防止した半導体装置および半導体装置の製造方法を得るという課題があった。

【解決手段】基板1上に立設された第一のシリコンピラー2と、その側面を覆う絶縁膜5と、絶縁膜5を覆うとともに、その先端部6aが第一のシリコンピラー2の先端部2aよりも基板1よりに位置してなるゲート電極6と、からなる縦型Tr部101と、基板1上に立設された第二のシリコンピラー2’と、その側面を覆う絶縁膜5’と、絶縁膜5’を覆うとともに、その先端部6’aが第二のシリコンピラー2’の先端部2’aよりも基板1から離れた側に位置してなり、ゲート電極6に接続されてなるゲートコンタクト電極6’と、からなるゲートコンタクト部102と、を有する半導体装置111を用いることにより、上記課題を解決できる。

(もっと読む)

EEPROM

【課題】2つのメモリトランジスタに同一のデータを確実に書き込むことができる、W(ダブル)セル方式のEEPROMを提供する。

【解決手段】半導体層には、第1不純物領域8、第2不純物領域9、第3不純物領域10、第4不純物領域11、第5不純物領域12および第6不純物領域13が形成されている。セレクトゲート15は、第1不純物領域8と第2不純物領域9との間の領域に、第1絶縁膜14を挟んで対向している。第1フローティングゲート16は、第2不純物領域9と第3不純物領域10との間の領域および第5不純物領域12に、第1絶縁膜14を挟んで対向している。第2フローティングゲート20は、第3不純物領域10と第4不純物領域11との間の領域および第6不純物領域13に、第1絶縁膜14を挟んで対向している。第5不純物領域12および第6不純物領域13は、第2不純物領域9と接続されている。

(もっと読む)

半導体装置

【課題】チャネル長を、トランジスタごとに自由に設計が可能な半導体装置を提供する。

【解決手段】複数の半導体柱2が立設された半導体基板1と、半導体柱2の外周面に設けられたゲート絶縁膜7と、半導体柱2の外周面を覆うゲート電極8と、半導体柱2の上側に設けられた第1不純物拡散領域3と、半導体柱2の下側に設けられた第2不純物拡散領域4と、を備え、第1不純物拡散領域3の厚さが半導体柱2ごとに異なっていることを特徴とする半導体装置。

(もっと読む)

メモリ素子、半導体記憶装置、表示装置、および携帯電子機器

【課題】チャネル領域の端部に起因するリーク電流を低減し、低電圧で動作し安定したメモリ特性(書込み、消去、読出し)を有する不揮発性のメモリ素子、メモリ素子を備える半導体記憶装置、表示装置、および表示装置を備える携帯電子機器を提供する。

【解決手段】メモリ素子1は、支持基板10と、支持基板10に積層され対向するソース領域11sおよびドレイン領域11dを有する半導体層11と、ソース領域11sおよびドレイン領域11dの間で半導体層11に形成されたチャネル領域11cと、チャネル領域11cに積層され電荷蓄積機能を有する第1ゲート絶縁膜13と、第1ゲート絶縁膜13を被覆する第1ゲート電極17と、チャネル領域11cのチャネル幅方向Dcwの端部11ctを被覆し第1ゲート絶縁膜13の膜厚Tg1と異なる膜厚Tg2を有する第2ゲート絶縁膜15を備え、第1ゲート電極17は、第2ゲート絶縁膜15を被覆している。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】不揮発性記憶素子と、容量素子若しくは抵抗素子とを有するシステムICの製造方法を提供する。

【解決手段】半導体基板の主面の素子分離領域5上に下部電極10cが設けられ、かつ下部電極10c上にONO膜11,12,13からなる誘電体膜を介在して上部電極19cが設けられた容量素子Cを有する半導体集積回路装置であって、半導体基板の主面の素子分離領域5と下部電極10cとの間に耐酸化性膜8、及び下部電極10cと上部電極19cとの間に耐酸化性膜12を有する。

(もっと読む)

不揮発性半導体装置及び不揮発性半導体装置の製造方法

【課題】ONO膜とシリサイド膜との短絡を起こさないようにし、ONO膜での電荷の不安定や電解分布の不均一、ONO膜の膜質低下などを防止する。

【解決手段】不揮発性半導体記憶装置はワードゲート22とコントロールゲート24と電荷蓄積層14とを具備する。ワードゲート22は半導体基板10のチャネル領域上方に絶縁層12を介して設けられている。コントロールゲート24はワードゲート22の側方に設けられている。電荷蓄積層14はチャネル領域とコントロールゲート24との間、及び、ワードゲート22とコントロールゲート24との間にONO膜で設けられている。コントロールゲート24は、シリサイド層24aと、非シリサイド層24b、24cとを備える。シリサイド層24aはニッケルを含むシリサイドで設けられている。非シリサイド層24b、24cはシリサイド層24aと電荷蓄積層14との間に設けられている。

(もっと読む)

半導体装置とその製造方法

【課題】 トランジスタと抵抗等複数種類の半導体素子を簡略化した工程で作成する。

【解決手段】 半導体装置の製造方法は、半導体基板にアスペクト比1以上の素子分離領域を形成し、ゲート絶縁膜を形成し、シリコン層を堆積し、パターニングしてゲート電極と抵抗素子を形成し、ゲート電極の側壁サイドウォールを形成し、第1の活性領域に高濃度の燐を、第2の活性領域及び抵抗素子に高濃度のp型不純物を、イオン注入し、500℃以下の温度でサリサイドブロック層を形成し、サリサイドブロック層を覆うように金属層を堆積し、選択的に金属シリサイド層を形成する。厚いゲート絶縁膜と著しく薄いゲート絶縁膜を形成し、サイドウォール形成前、厚いゲート絶縁膜は貫通しない第1導電型のイオン注入と、厚いゲート絶縁膜も貫通する逆導電型の斜めイオン注入を行う。

(もっと読む)

半導体装置およびその製造方法

【課題】STI構造の素子分離を行う場合にソース/ドレイン領域の形成時点で半導体基板に対する転位の発生を抑制できるようにする。

【解決手段】素子分離絶縁膜3を活性領域2との間の接触領域においてシリコン基板1の表面の高さよりも深く且つソース/ドレイン領域1bのピーク濃度となる高濃度不純物拡散領域1bの形成深さd4(もしくはPN接合部)よりも浅い高さに位置し、当該領域よりも外方領域に遠ざかるに連れて深さd4よりも深い深さd2に位置するように形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】高性能な書きこみ消去特性を有する不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板のp型ウエル2上にゲート絶縁膜6を介して選択ゲート18が形成され、p型ウエル2上に酸化シリコン膜15a、窒化シリコン膜15bおよび酸化シリコン膜15cからなる積層膜15を介してメモリゲート17が形成される。メモリゲート17は、積層膜15を介して選択ゲート18に隣接する。p型ウエル2の選択ゲート18およびメモリゲート17の両側の領域には、ソース、ドレインとしてのn型の不純物拡散層20,21が形成されている。不純物拡散層20,21の間に位置するチャネル領域のうち、選択ゲート18により制御され得る領域51とメモリゲート17により制御され得る領域52とにおける不純物の電荷密度が異なる。

(もっと読む)

固体撮像素子、その動作方法、その製造方法及びデジタルカメラ

【課題】受光量に十分に対応(ばらつきの少ない線形又は非線形)したデータを不揮発性メモリセルから読み出すことができる固体撮像装置を実現すること。

【解決手段】入射光を受け信号電荷を発生させる受光素子と、一端が受光素子に接続され、他端が検出ノードに接続された第1のトランジスタと、一端が検出ノードに接続された第2のトランジスタと、検出ノードに制御ゲート又は一端が接続された電荷蓄積層を有するメモリセルトランジスタと、を具備することを特徴とする固体撮像装置。

(もっと読む)

半導体記憶装置

【課題】高集積化することができるチャージトラップ型フラッシュ構造の半導体記憶装置を提供する。

【解決手段】半導体記憶装置70には、半導体基板1の第1主面(表面)にゲート絶縁膜2、電荷蓄積膜3、高誘電率絶縁膜4、ゲート電極膜5、及び絶縁膜6が積層形成される。高誘電率絶縁膜4は、底部が上部より広い台形形状を有する。ゲート電極膜5及び絶縁膜6は、高誘電率絶縁膜4の底部端よりも内側に形成される。メモリセルトランジスタMTRのゲート長とメモリセルトランジスタMTRのゲート間は60nm以下に形成される。メモリセルトランジスタMTRのゲート間にはソース或いはドレインが設けられず、メモリセルトランジスタMTRの書き込み動作及び読み出し動作時では、発生する反転層31がソース或いはドレインの代わりをする。

(もっと読む)

141 - 160 / 477

[ Back to top ]