Fターム[5F101BH09]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | イオン注入 (487)

Fターム[5F101BH09]の下位に属するFターム

イオン注入によるトラップ形成 (10)

Fターム[5F101BH09]に分類される特許

101 - 120 / 477

不揮発性半導体記憶装置及びその駆動方法

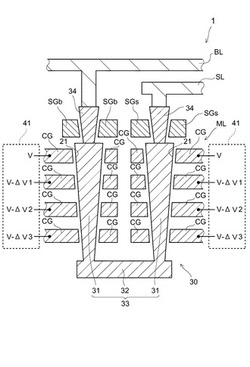

【課題】動作の信頼性が高い不揮発性半導体記憶装置及びその駆動方法を提供する。

【解決手段】不揮発性半導体記憶装置1においては、シリコン基板上に、それぞれ複数の絶縁膜及び電極膜が交互に積層された積層体MLが設けられており、積層体ML内には積層方向に延びる貫通ホール21が形成されており、各電極膜は複数の制御ゲート電極CGに分断されており、貫通ホール21の内部にはシリコンピラー31が埋設されている。また、装置1には、制御ゲート電極CGに対して電位を供給する駆動回路41が設けられている。そして、貫通ホール21の径は積層方向における位置によって異なっており、駆動回路41は、貫通している貫通ホール21の径が小さい制御ゲート電極CGほど、シリコンピラー31との間の電位差が小さくなるような電位を印加する。

(もっと読む)

不揮発性半導体記憶装置

【課題】動作の信頼性が高い不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置にメモリセルアレイ及び制御回路を設け、メモリセルアレイには、それぞれ複数の絶縁膜及び電極膜が交互に積層された積層体を設け、この積層体に積層方向に延びる貫通ホールを形成し、その内部にシリコンピラーを埋設し、電極膜とシリコンピラーとの間に電荷蓄積膜を設ける。これにより、電極膜とシリコンピラーとの交差部分毎にメモリセルが形成される。そして、制御回路は、フォーマット時に、全てのメモリセルに値「0」を書き込み、全てのメモリセルに対して値「0」を消去する動作を行い、積層体の最上段に形成されたメモリセルに記憶された値を読み出し、値「0」が読み出されたメモリセルについては、消去動作が不良であったと判定し、以後不使用とする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】半導体基板の素子分離溝内の絶縁膜をエッチバック処理したときに側壁に残存する絶縁膜を除去して容量カップリングのロスを低減する。

【解決手段】シリコン基板1に、ゲート絶縁膜4、浮遊ゲート電極用の多結晶シリコン膜5、シリコン窒化膜8を積層形成する。所定間隔で複数のトレンチ1aを形成し、トレンチ1a内に素子分離絶縁膜2を埋め込み形成する。トレンチ1a内の素子分離絶縁膜2を所定深さまでエッチバックする。フォトレジストを全面に塗布してトレンチ1a底部が露光されにくい条件で露光し、トレンチ1aの底面部にレジスト10aを残す。レジスト10aをマスクとしてウェットエッチングでシリコン酸化膜をエッチングしてトレンチ1a内の側壁に残存する素子分離絶縁膜を除去する。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】ワードゲートとコントロールゲートの間の高低差を大きくすることなく、シリサイドショートを防止することが可能な不揮発性半導体記憶装置、及びその製造方法を提供すること。

【解決手段】本発明にかかる不揮発性半導体記憶装置は、半導体基板1上にゲート絶縁膜2を介して形成され、一定の幅を有する部分が上に突出した突出部3bが設けられているワードゲート3と、ワードゲート3の側壁面にONO膜4を介して設けられたコントロールゲート5と、コントロールゲート5の側壁面と、ワードゲート3の突出部3bの側壁面とに形成された絶縁性のサイドウォール7と、ワードゲート3の突出部3bの上面と、コントロールゲート5の表面の一部とに形成されたシリサイド層9と、を備え、突出部3bの幅は、突出部3bよりも下側の部分のワードゲート3の幅よりも狭いものである。

(もっと読む)

半導体装置の製造方法

【課題】ロジック回路とメモリ回路を混載した半導体装置において、ロジック回路部に形成されるレジストパターン形状の精度低下抑制に寄与する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、ロジックトランジスタ、不揮発性メモリをそれぞれ形成する第1及び第2の活性領域を画定する素子分離絶縁膜を、STIで形成する工程と、第2の活性領域上方に、フローティングゲートとなる導電層を形成する工程と、導電層上及びその外側の領域を覆って、窒化シリコンを含む絶縁膜を形成する工程と、第1の活性領域の隣接部分の素子分離絶縁膜上の窒化シリコンを含む絶縁膜を覆い、第1の活性領域を露出するマスクを用いてエッチングする工程と、第1の活性領域の隣接部分の素子分離絶縁膜上の窒化シリコンを含む絶縁膜上に端部の配置されたフォトレジストパターンを形成する工程とを有する。

(もっと読む)

フローティングゲートメモリセルを製造するための方法およびフローティングゲートメモリセル

【課題】ソースがチャネル領域の中に横方向に散在および拡散するのを低減させ、これはフローティングゲートメモリセルにおけるドレイン誘導障壁低下(DIBL)の低減をもたらす。

【解決手段】基板404のソース領域422に窪み464を形成する。窪み464はスタックゲート構造408に隣接して位置し、窪み464は傾斜のついた側壁466と底部468と深さ476とを有し、スタックゲート構造408は基板404におけるチャネル領域426の上に位置する。さらに、窪み464の傾斜のついた側壁466に隣接したフローティングゲートメモリセル402のソース488を形成し、スタックゲート構造408に隣接しかつ窪み464の傾斜のついた側壁466に隣接したスペーサ490を形成する。スペーサ490は窪み464の底部468に延在し、ソース488が前記チャネル領域426の中に横方向に散在および拡散するのを低減させる。

(もっと読む)

半導体装置の製造方法

【課題】フラッシュメモリと、精度が低くても高耐圧性が要求されるキャパシタと、耐圧性が低くても高精度が要求されるキャパシタとを備えた半導体装置を比較的少ない工程で製造できる半導体装置の製造方法を提供する。

【解決手段】半導体基板10上に形成されたシリコン膜13により、フラッシュメモリのフローティングゲートと高耐圧キャパシタの下部電極13bとを形成する。この場合、シリコン膜13中の不純物濃度を、フラッシュメモリに適した濃度とする。その後、半導体基板10に不純物をイオン注入して高精度キャパシタの下部電極となる高濃度不純物領域15を形成する際に、高耐圧キャパシタの下部電極13bに不純物を追加注入し、下部電極13bの不純物濃度を向上させる。次いで、高精度キャパシタの誘電体膜12を、増速酸化により形成する。

(もっと読む)

半導体装置の製造方法

【課題】電荷蓄積膜を用いる不揮発性記憶用MOS型トランジスタと、これを選択するMOS型トランジスタが隣接するスプリットゲート構造を有する不揮発性メモリセルにおいて、電荷保持特性を向上し、ゲート電極を低抵抗化する。

【解決手段】電荷蓄積膜のコーナー部20の薄膜化を抑制して電荷保持特性を向上するために、選択ゲート電極15の側壁にテーパーを設ける。また、自己整合で形成するゲート電極を低抵抗化するシリサイドを安定に行うため、選択ゲート電極15の側壁をリセスさせる。もしくは、自己整合ゲート電極上部18と選択ゲート電極上部65の間に段差を設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中に含まれる不純物の拡散を防止することができ、さらに、ゲート絶縁膜の信頼性及びホットキャリア耐性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】N型シリコン基板1上にゲート酸化膜36およびP+型ゲート電極35を形成する。P+型ゲート電極35の両側にソース/ドレイン領域6を形成する。ゲート酸化膜36およびP+型ゲート電極35中には窒素がドープされ、窒素ドーピング領域30が形成される。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】選択トランジスタの閾値が安定した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置1において、シリコン基板11に複数本のSTI17を形成して、シリコン基板11の上層部分を複数本のアクティブエリアAAに区画する。また、アクティブエリアAA上にトンネル絶縁膜14及び電荷蓄積膜15を設け、STI17を覆うようにブロック絶縁膜18を設け、その上にワード電極WL及び選択ゲート電極SGを設ける。そして、STI17の上面17aにおける選択ゲート電極SGの直下域を、ワード電極WLの直下域よりも上方に位置させることにより、アクティブエリアAAの角部と選択ゲート電極SGとの間の最短距離を、アクティブエリアAAの角部とワード電極WLとの間の最短距離よりも長くする。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極から電荷蓄積層に電荷を注入する不揮発性メモリにおいて、従来のゲート構造に比べて電荷の注入効率、電荷保持特性および信頼性を共に向上させる。

【解決手段】電荷蓄積層を構成する窒化シリコン膜に電子および正孔を注入し、トータルの電荷量を変えることによって書き込み・消去を行う不揮発性メモリにおいて、ゲート電極からの電荷注入を高効率で行うために、メモリセルのゲート電極を、ノンドープのポリシリコン層54とメタル材料電極層59の2層膜で構成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】コントロールゲートが半導体基板に形成された不純物拡散層によって構成されている不揮発性半導体記憶装置において、信頼性を維持しつつ、カップリング比を大きくする。

【解決手段】P型の半導体基板1に、N型ウェル3とN型高濃度拡散層17からなるコントロールゲートと、コントロールゲートとは絶縁され、互いに間隔をもって形成された2つのN型拡散層からなるソース5及びドレイン7が形成されている。コントロールゲート表面に第1絶縁膜11が形成されている。ソース5及びドレイン7の間の半導体基板1表面に第2絶縁膜13が形成されている。第1絶縁膜11上からフィールド酸化膜9上を介して第2絶縁膜13上にわたって形成された半導体膜からなるフローティングゲート15が形成されている。コントロールゲートの一部分を構成するN型高濃度拡散層17は、フローティングゲート15下にも配置されている。

(もっと読む)

NANDフラッシュ・メモリを製造するための単一トンネル・ゲート酸化方法

【課題】選択トランジスタと浮遊ゲート・メモリ・トランジスタのゲート酸化物(24)を単一の酸化工程で製造する、NANDメモリ・ストリングを製造するための単一トンネル・ゲート酸化方法を開示する。

【解決手段】選択ゲート・トランジスタと浮遊ゲート・メモリ・トランジスタは、85Å〜105Åの厚さの酸化物を有する。単一トンネル・ゲート手法の場合は、NANDメモリ・ストリングを適切に機能させるためにミデアムドープ・ソース/ドレイン領域(62)注入条件を慎重に選択する必要がある。1つの実施形態において、ミデアムドープ・ソース/ドレイン領域は、ヒ素が1013〜1014/cm2の濃度にドープされる。

(もっと読む)

不揮発性半導体記憶装置

【課題】高性能な書きこみ消去特性を有する不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板のp型ウエル2上にゲート絶縁膜6を介して選択ゲート18が形成され、p型ウエル2上に酸化シリコン膜15a、窒化シリコン膜15bおよび酸化シリコン膜15cからなる積層膜15を介してメモリゲート17が形成される。メモリゲート17は、積層膜15を介して選択ゲート18に隣接する。p型ウエル2の選択ゲート18およびメモリゲート17の両側の領域には、ソース、ドレインとしてのn型の不純物拡散層20,21が形成されている。不純物拡散層20,21の間に位置するチャネル領域のうち、選択ゲート18により制御され得る領域51とメモリゲート17により制御され得る領域52とにおける不純物の電荷密度が異なる。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高いドレインコンタクトを有する半導体装置の製造方法を提供する。

【解決手段】第1ドレインコンタクト14を形成する工程と、第1ドレインコンタクト14に接続された第2ドレインコンタクト15を形成する工程と、第2ドレインコンタクト15に接続された配線16を形成する工程と、配線16をマスクとして自己整合的に、少なくとも第2ドレインコンタクト15の近傍の第2層間絶縁膜33に、第1層間絶縁膜13と第2層間絶縁膜33との界面34より深い位置まで不純物イオンを注入し、界面34に残置されている異物32をアモルファス化する工程と、不純物イオンが注入された第1および第2層間絶縁膜13、33をエッチングして異物32を露出させ、異物32を除去する工程と、第1絶縁膜13上に配線16を覆うように第3層間絶縁膜36を形成する工程と、を具備する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】微細化が進んだ場合であってもトランジスタのカットオフ特性を改善する。

【解決手段】半導体基板100上に形成されるp型ウェル2には、ビット線BLの長手方向に沿って形成されたトレンチ3に素子分離絶縁膜4が埋め込まれている。素子分離絶縁膜4によりp型ウェル2が分離され、メモリトランジスタが形成される素子形成領域2Aが形成される。素子分離絶縁膜4にはボロン等のp型不純物が注入されており、その不純物濃度は、p型ウェル2の不純物濃度よりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】 抵抗素子の抵抗値の選択範囲を拡大し、且つ抵抗層形成後にシリサイドブロックを形成せずに該抵抗層のシリサイド化を防止することを可能にする。

【解決手段】 半導体領域11上に絶縁膜15を形成し、絶縁膜15を介して半導体領域11に不純物のイオン注入12を行う。これにより、絶縁膜15の下に抵抗層13が形成されるとともに、抵抗層13に隣接して電極領域14が形成される。その後、電極領域14の表面にシリサイド膜17を形成する。このとき、絶縁膜15は、抵抗層13がシリサイド化されることを防止するシリサイドブロックとして機能する。イオン注入12として、同一半導体基板上に形成されるMOSトランジスタのソース/ドレイン領域への不純物注入工程を利用し得る。

(もっと読む)

半導体装置とその製造方法

【課題】周辺回路領域に形成されるロジック回路等に不具合が発生するのを防ぐことができるフラッシュメモリセルを備えた半導体装置とその製造方法を提供すること。

【解決手段】第1導電体25aのコンタクト領域CR上の第2絶縁膜26を除去する工程と、第2絶縁膜26の上に第2導電膜30を形成する工程と、第1導電体25aのコンタクト領域CR上の第2導電膜30を除去し、該第2導電膜30を第2導電体30aとする工程と、第2導電体30aを覆う層間絶縁膜(第3絶縁膜)44を形成する工程と、コンタクト領域CR上の層間絶縁膜44に第1ホール44aを形成する工程と、コンタクト領域CRと電気的に接続される導電性プラグ45aを第1ホール44a内に形成する工程と、を有することを特徴とする半導体装置の製造方法による。

(もっと読む)

パターン形成方法、薄膜トランジスタ及びその作製方法

【課題】フォトリソグラフィ法に用いるフォトマスクの枚数を少なくする。

【解決手段】第1の膜を形成し、該第1の膜上にフォトリソグラフィ法により第1のレジストマスクを形成し、第1のレジストマスクを用いて所定のパターンを有する第1の層を形成し、第1のレジストマスクを除去し、第2の膜を形成し、該第2の膜上にフォトリソグラフィ法により第1のレジストマスクと同一のフォトマスクにより第2のレジストマスクを形成し、該第2のレジストマスクを縮小して第3のレジストマスクを形成し、第3のレジストマスクを用いて所定のパターンを有する第2の層を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

101 - 120 / 477

[ Back to top ]