Fターム[5F101BH09]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | イオン注入 (487)

Fターム[5F101BH09]の下位に属するFターム

イオン注入によるトラップ形成 (10)

Fターム[5F101BH09]に分類される特許

61 - 80 / 477

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

半導体装置の製造方法

【課題】注入した不純物の拡散を抑制しつつ結晶欠陥を低減する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、リンまたはボロンを分子状イオンの形態で含有する第1の不純物80と、リンまたはボロンよりも注入量が少ない炭素、フッ素または窒素を分子状イオンの形態で含有する、もしくは、リンまたはボロンよりも注入量が少ない炭素を原子イオンの形態で含有する第2の不純物81と、を半導体層1に注入して不純物注入層9を形成する工程を含む。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】データの保持期間を長くする半導体装置又は半導体記憶装置を提供する。

【解決手段】一対の不純物領域を有する第1の半導体層152aと、第1の半導体層と同じ材料であり、第1の半導体層と離間する第2の半導体層152bと、第1、第2の半導体層の上に設けられた第1の絶縁層153と、第1の絶縁層153を介して第1の半導体層に重畳する第1の導電層154と、第1の絶縁層153を介して第1の導電層に重畳し、第1の半導体層と異なる材料である第3の半導体層156と、第1の導電層及び第3の半導体層に電気的に接続される第2の導電層157bと、第3の半導体層156に電気的に接続され、第2の導電層と同じ材料である第3の導電層157aと、第3の半導体層、第2の導電層、及び第3の導電層の上に設けられた第2の絶縁層158と、第2の絶縁層を介して第3の半導体層に重畳する第4の導電層159と、を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】特性を向上させる不揮発性メモリを有する半導体装置を提供する。

【解決手段】半導体装置を、制御ゲート電極CGと、制御ゲート電極CGと隣合うように配置されたメモリゲート電極MGと、絶縁膜3と、その内部に電荷蓄積部を有する絶縁膜5と、を有するよう構成する。このうち、メモリゲート電極MGは、絶縁膜5上に位置する第1シリコン領域6aと、第1シリコン領域6aの上方に位置する第2シリコン領域6bと、を有するシリコン膜よりなり、第2シリコン領域6bは、p型不純物を含有し、第1シリコン領域6aのp型不純物の濃度は、第2シリコン領域6bのp型不純物の濃度よりも低く構成する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】対向する二つの記憶素子のコントロールゲートのゲート長に起因する記憶素子の特性のばらつきを抑制する。

【解決手段】上記の課題を解決するために、不揮発性半導体記憶装置(1)を以下のように構成する。第1不揮発性メモリセル(1a)は、第1チャネル領域(11a)と、第1フローティングゲート(5a)と、第1コントロールゲート(6a)とを含むものとする。また、第2不揮発性メモリセル(1b)は、第2チャネル領域(11b)と、第2フローティングゲート(5b)と、第2コントロールゲート(6b)とを含むものとする。ここにおいて、第1チャネル領域(11a)は、第1フローティングゲート側チャネル領域(13a)と、第1コントロールゲート側チャネル領域(12a)とを備え、第1コントロールゲート側チャネル領域(12a)は不純物濃度が濃い高濃度ポケット領域(10)を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】スタック構造のゲート電極を有する不揮発性メモリの低電圧動作化・低消費電力化を実現しうる半導体装置の製造方法を提供する。

【解決手段】素子分離絶縁膜上に第1の導電膜を形成し、素子領域上に第1の絶縁膜を形成し、第1の絶縁膜上及び第1の導電膜が形成された素子分離絶縁膜上に第2の導電膜を形成し、第2の導電膜及び第1の導電膜をパターニングし、第2の導電膜により形成された第1の部分が素子領域上に位置し、第1の導電膜と第2の導電膜の積層膜により形成された第2の部分が素子分離絶縁膜上に位置するフローティングゲートを形成し、フローティングゲート上に第2の絶縁膜を形成し、第2の絶縁膜上にコントロールゲートを形成する。

(もっと読む)

半導体メモリ及びその製造方法

【課題】半導体メモリの構造の簡略化と製造プロセスの簡易化とを実現する。

【解決手段】半導体基板と、半導体基板内に形成され、かつ互いに直交する第1及び第2の方向にそれぞれ延在する第1及び第2のソース領域104、109とを有する半導体メモリ。第1及び第2のソース領域はそれぞれ拡散領域であって、交差する部分で電気的に接続されている。また半導体メモリは、第2のソース領域109と同一方向に延在するビットライン108と、第2のソース領域109上に形成されたソースラインとを有し、ソースラインと第2のソース領域109とのコンタクトと、ビットライン108と半導体基板内に形成されたドレイン領域とのコンタクトとは直線状に配置されている。

(もっと読む)

半導体装置

【課題】パーコレーションリークを抑制可能な構造を有する半導体装置を提供する。

【解決手段】ソース領域18、ドレイン領域18及びチャネル領域を有する半導体領域と、チャネル領域上に形成された第1のトンネル絶縁膜12と、第1のトンネル絶縁膜上に形成され、エネルギー障壁を有する障壁層13と、障壁層上に形成された第2のトンネル絶縁膜14と、第2のトンネル絶縁膜上に形成され、SiY(SiO2)X(Si3N4)1-X (ただし、0≦X≦1、Y>0)で表される絶縁膜を具備する電荷蓄積部15と、電荷蓄積部上に形成され、エネルギー障壁の高さを制御する制御電極17とを備え、X及びYは、[2×2X/(4−2X)+(4−4X)/(4−2X)]×[Y/(Y+7−4X)]≧0.016 なる関係を満たし、障壁層は、クーロンブロッケイド条件を満たす導電性微粒子を含んだ微粒子層で形成されている。

(もっと読む)

不揮発性メモリー装置の製造方法

【課題】不揮発性メモリー装置の製造方法であって、特に半導体パターン厚さの均一性が向上される3次元半導体装置の製造方法、及び当該製造方法によって製造された3次元半導体装置を提供する。

【解決手段】この製造方法は、基板10の上に複数の第1の膜(鋳型膜)120及び複数の第2の膜(犠牲膜)が交互に積層された積層膜構造体を形成する段階、積層膜構造体を貫通する開口部、及び開口部周囲にアンダーカット領域を形成する段階、アンダーカット領域に局所的に配置される絶縁スペーサー155を形成する段階、絶縁スペーサー155が形成された開口部内に半導体パターン165を形成する段階を含む。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】隣接セルとの容量を抑制することが可能な半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態の半導体記憶装置は、第1の方向および前記第1の方向と直交する第2の方向に配置される複数のメモリセルトランジスタを備える。前記メモリセルトランジスタのそれぞれは、半導体基板上に形成される第1の絶縁膜と、前記第1の絶縁膜上に形成される浮遊ゲート電極と、前記浮遊ゲート電極上に形成される第2の絶縁膜と、前記第2の絶縁膜上に形成される制御ゲート電極と、を有する。前記第1および第2の方向に隣接する2つの前記メモリセルトランジスタの前記浮遊ゲート電極は、前記隣接する方向の側面に括れた領域を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース・ドレイン領域とコンタクトプラグの接続部分の電気抵抗が低減され、かつ短チャネル効果の発生が抑えられたトランジスタを有する、n型およびp型トランジスタを含む半導体装置、およびその半導体装置の製造方法を提供すること。

【解決手段】不純物高濃度領域を有する半導体装置を提供する。前記不純物高濃度領域は、第1のソース・ドレイン領域内の前記第1のソース・ドレイン領域と前記第1のコンタクトプラグとの界面近傍に形成される。前記不純物高濃度領域の前記第1のコンタクトプラグの底面の長手方向の前記第1のコンタクトプラグの前記底面の輪郭からの前記不純物高濃度領域の輪郭の広がり幅の少なくとも一方は、前記第1のコンタクトプラグの前記底面の短手方向の前記第1のコンタクトプラグの前記底面の輪郭からの前記不純物高濃度領域の輪郭の広がり幅よりも大きい。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】ビット線に拡散層を用いる半導体記憶装置のチャネル領域に発生する2次電子を抑制して信頼性を向上できるようにする。

【解決手段】半導体記憶装置100は、P型の半導体基板101の上部にそれぞれが互いに並行に延びるように形成された複数のビット線拡散層108と、半導体基板101の上で、且つそれぞれが各ビット線拡散層108と交差する方向に互いに並行に延びるように形成された複数のワード線電極110とを有している。さらに、半導体基板101における各ワード線電極110の下方の領域には、周囲よりも濃度が低いP型の複数の第3の不純物層111Aがそれぞれ自己整合的に形成されている。

(もっと読む)

半導体記憶装置

【課題】動作信頼性を向上出来る半導体記憶装置を提供すること。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板10上に第1絶縁膜13を介在して形成された電荷蓄積層14と、電荷蓄積層14上に第2絶縁膜15を介在して形成された制御ゲート16とを具備し、制御ゲート16は、その少なくとも一部領域16−2において、その側面が外側に向かって膨らんだ形状を有し、制御ゲート16において側面が膨らみ始める部分から該制御ゲート16の頂上までの高さH1は、膨らみ始める部分より上の領域における制御ゲート16の最大幅W2_max2よりも大きい。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】半導体記憶装置において、微細化が可能で基板へのリーク電流が低減された構造及びその製造方法を提供する。

【解決手段】半導体記憶装置は、複数の拡散ビット線2と、複数の拡散ビット線2の各々の上に設けられた埋め込み絶縁膜3と、複数の拡散ビット線2の間に設けられたトラップ膜4と、複数の拡散ビット線2と交差する複数のワード線5と、対応する前記拡散ビット線と各々電気的に接続された複数の第1の注入拡散層7aと、複数の第1の注入拡散層7aの各々を電気的に分離する素子分離領域8とを備える。複数のワード線5のうち、複数の第1の注入拡散層7aに最も近いワード線5xの上面上から拡散ビット線2の第1の注入拡散層7a側の端部上及び素子分離領域8上に至る領域に絶縁膜11が設けられている。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】多層配線構造を使って、キャパシタンスが大きく、かつキャパシタンス値が安定なキャパシタ素子を半導体基板上に集積化する。

【解決手段】多層配線構造18は、少なくとも第1層目の層間絶縁膜16と、第1層目の層間絶縁膜中に埋設された第1配線層と、を含み、第1配線層は、第1の電源に接続され前記第1の層間絶縁膜中に埋設された第1の配線パタ―ン15C1と、第2の電源に接続され前記第1の層間絶縁膜中に埋設された第2の配線パタ―ン15C2と、を含み、第1の配線パタ―ンと前記第2の配線パタ―ンとは容量結合して第1のキャパシタを形成し、第1の配線パタ―ンは積層配線パタ―ン13C上に形成されて、前記第4の電極パターン13Gと容量結合して第2のキャパシタを形成し、第4の電極パターンは第2の配線パタ―ンに電気的に接続されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】電荷蓄積層をもち、電荷のトラップを利用する記憶素子の保持特性を向上させる技術を提供する。

【解決手段】電荷蓄積層(24)の上のメモリゲート(21)と、第1サイドゲート(22)と、第2サイドゲート(23)と、第1サイドゲート(22)側の第1不純物注入領域(31)と、第2サイドゲート(23)側の第2不純物注入領域(32)と、チャネル領域(33、34、35)とを具備する不揮発性半導体記憶装置を構成する。チャネル領域(33、34、35)は、電荷蓄積層(24)の下の第1領域(33)と、第1領域(33)と第1不純物注入領域(31)との間のセレクト側領域(34)と、第1領域(33)と第2不純物注入領域(32)との間のアシスト側領域(35)とを含むことが好ましい。そして、ゲート長方向におけるセレクト側領域(34)の長さ(L1)は、アシスト側領域(35)の長さ(L2)よりも長いものとする。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の駆動方法

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを保存する半導体装置を提供する。

【解決手段】書き込みトランジスタのドレインと読み出しトランジスタのゲート、および、前記ドレインとキャパシタの一方の電極を接続した記憶セルを複数用いて形成されたマトリクスにおいて、書き込みトランジスタのゲートを書き込みワード線に、書き込みトランジスタのソースを書き込みビット線に、読み出しトランジスタのソースとドレインとを、それぞれ、読み出しビット線及びバイアス線に接続する。さらに、キャパシタの他方の電極を読み出しワード線に接続する。配線数を減らすために、読み出しワード線を、前記書き込みトランジスタのゲートが接続していない書き込みワード線で代用する、さらに読み出しビット線を書き込みビット線で代用する。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】閾値電圧の制御性を向上させて形成された複数種類のトランジスタを備える不揮発性記憶装置、および、それに適した製造方法を提供する。

【解決手段】1つの半導体基板2の表面に形成された複数種類のMOSトランジスタを有する不揮発性記憶装置であって、n形のソース領域14およびドレイン領域15と、その間の半導体基板2の表面上に設けられたゲート絶縁膜17と、ゲート電極18と、ゲート絶縁膜17の直下に位置し、n形不純物とp形不純物との両方を含むチャネル領域42と、を有するMOSトランジスタ10と、n形のソース領域24およびドレイン領域25と、その間の半導体基板2の表面上に設けられたゲート絶縁膜27と、ゲート電極28と、ゲート絶縁膜27の直下に位置し、n形不純物の濃度プロファイルがチャネル領域42と同じであるチャネル領域43と、を有するMOSトランジスタ20と、を備える。

(もっと読む)

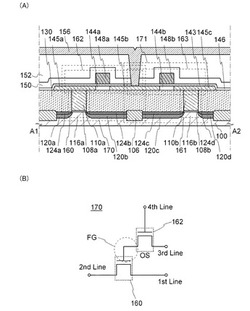

半導体装置、及び半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供することを課題の一とする。また、信頼性の高い半導体装置の作製方法を提供することを課題の一とする。また、消費電力が低い半導体装置を提供することを課題の一とする。また、消費電力が低い半導体装置の作製方法を提供することを課題の一とする。また、量産性の高い半導体装置を提供することを課題の一とする。また、量産性の高い半導体装置の作製方法を提供することを課題の一とする。

【解決手段】酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すれば良い。具体的には、酸化物半導体層にハロゲン元素を添加した後に加熱処理を施し、不純物を除去して使用すれば良い。ハロゲン元素としては、フッ素が好ましい。

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供することを課題の一とする。また、信頼性の高い半導体装置の作製方法を提供することを課題の一とする。また、消費電力が低い半導体装置を提供することを課題の一とする。また、消費電力が低い半導体装置の作製方法を提供することを課題の一とする。また、量産性の高い半導体装置を提供することを課題の一とする。また、量産性の高い半導体装置の作製方法を提供することを課題の一とする。

【解決手段】酸素欠損を生じることなく酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すればよい。具体的には、酸化物半導体層に酸素を添加した後に加熱処理を施し、不純物を除去して使用すればよい。特に酸素の添加方法としては、高エネルギーの酸素をイオン注入法またはイオンドーピング法などを用いて添加する方法が好ましい。

(もっと読む)

61 - 80 / 477

[ Back to top ]