Fターム[5F101BH09]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | イオン注入 (487)

Fターム[5F101BH09]の下位に属するFターム

イオン注入によるトラップ形成 (10)

Fターム[5F101BH09]に分類される特許

81 - 100 / 477

半導体装置

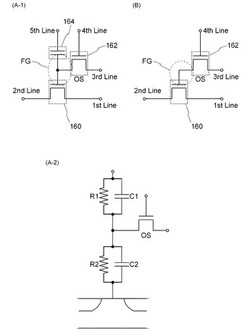

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用トランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの情報の書き込みは、書き込み用トランジスタをオン状態とすることにより、書き込み用トランジスタのソース電極(またはドレイン電極)と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタとして、しきい値電圧を正に制御したトランジスタを用いることで、読み出し電位を正の電位とする。

(もっと読む)

半導体装置およびその製造方法

【課題】高品質な半導体装置およびその製造方法を提供する

【解決手段】半導体基板1内に形成された一対の第1の不純物拡散領域1bと、一対の第1の不純物拡散領域1bに挟まれ、一対の第1の不純物拡散領域1bに隣接して形成され、第1の不純物拡散領域1bと同じ導電型且つ第1の不純物拡散領域1bよりも不純物濃度の低い一対の第2の不純物拡散領域1aと、一対の第2の不純物拡散領域1aに挟まれたチャネル領域と、第1の不純物拡散領域1b上に形成された周辺絶縁膜4と、第2の不純物拡散領域1a上およびチャネル領域上に形成され、周辺絶縁膜4よりも膜厚の厚いゲート絶縁膜3と、ゲート絶縁膜3上且つチャネル領域の略直上に形成されたゲート電極5とを備える。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタの微細化を達成し、電界緩和がなされた、酸化物半導体を用いた半導体装置を提供することを課題の一とする。

【解決手段】ゲート電極の線幅を微細化し、ソース電極層とドレイン電極層の間隔を短縮する。ゲート電極をマスクとして自己整合的に希ガスを添加し、チャネル形成領域に接する低抵抗領域を酸化物半導体層に設けることができるため、ゲート電極の幅、即ちゲート配線の線幅を小さく加工しても位置精度よく低抵抗領域を設けることができ、トランジスタの微細化を実現できる。

(もっと読む)

半導体装置

【課題】トランジスタ間の分離性が良好な半導体装置を提供する。

【解決手段】半導体装置において、第1導電型の半導体基板と、前記半導体基板の上層部分を複数の能動領域に区画する素子分離絶縁膜と、前記能動領域の上部に相互に離隔して形成された第2導電型のソース層及びドレイン層と、前記半導体基板上における前記ソース層と前記ドレイン層との間のチャネル領域の直上域に設けられたゲート電極と、前記半導体基板と前記ゲート電極との間に設けられたゲート絶縁膜と、第1導電型であり、実効的な不純物濃度が前記半導体基板の実効的な不純物濃度よりも高く、前記能動領域における前記ソース層及び前記ドレイン層の直下域に形成され、前記ゲート電極の直下域には形成されていないパンチスルーストッパ層と、を設ける。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】従来の半導体記憶装置では、十分に半導体チップの面積を削減することができない問題があった。

【解決手段】本発明の半導体記憶装置は、半導体基板の平坦部に形成されたドレイン領域13と、半導体基板に形成された凸部の上端部に形成されたソース領域10と、ドレイン領域13の一部と重なる領域であって、かつ、平坦部の上層に形成されるコントロールゲート12と、コントロールゲート12と隣り合った領域であって、平坦部、凸部の壁面及びソース領域10の一部を覆う領域に形成されるフローティングゲート11と、を有する。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】メモリセルMCは、半導体基板1の主面上のゲート絶縁膜5を介して設けられたコントロールゲート電極CGと、コントロールゲート電極CGの側面および半導体基板1の主面に沿って設けられたONO膜9と、ONO膜9を介してコントロールゲート電極CGの側面および半導体基板1の主面上に設けられたメモリゲート電極MGとを有する。コントロールゲート電極CGおよびメモリゲート電極MGの上部には、シリサイド膜15およびシリサイド膜15の表面の酸化によって形成された絶縁膜51が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の不純物分布のバラツキを抑え、STIエッジ部分への電界集中をより効果的に制御でき、実効チャネル幅が狭くなることを抑制できる半導体装置およびその製造方法を提供する。

【解決手段】P型のシリコン基板10の一主面11に、トレンチ22と絶縁物24とを有する素子分離領域25と、素子分離領域25に囲まれた素子領域12であって、シリコン基板10の側面上部17が、トレンチ25に露出した素子領域12を形成し、ゲート絶縁膜40をシリコン基板10の上面14から側面上部17に延在して形成し、N+型ポリシリコン32とN+型ポリシリコン32の両側のP+型ポリシリコン34と、P+型ポリシリコン34の下側の側面上部17に沿って設けられたN+型ポリシリコン36とを有するゲート電極30を形成する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】素子分離絶縁膜の埋め込み後の化学機械研磨法による研磨で、浮遊ゲート電極をストッパ膜として使用できるようにする。

【解決手段】シリコン基板1にゲート絶縁膜4、下層多結晶シリコン膜5a、上層多結晶シリコン膜5bを積層形成する。上層多結晶シリコン膜5bは、成膜時に炭素を1×1018atoms/cm3以上例えば2×1020〜2×1021atoms/cm3の範囲の濃度で添加される。素子分離溝1bを形成した後に、素子分離絶縁膜2を埋め込み、化学機械研磨法の研磨で素子分離溝1b内以外の部分を除去する。この時、上層多結晶シリコン膜5bがスクラッチの発生を抑制できるストッパ膜として利用でき、シリコン窒化膜などを不要とした構成とすることができる。

(もっと読む)

半導体記憶装置

【課題】スプリットゲート型のMONOSメモリセルを有する半導体記憶装置において、SSI方式による書込み時のディスターブ耐性を向上させる。また、非選択メモリセルのディスターブ耐性が向上することにより、メモリモジュールの面積を低減させる。

【解決手段】メモリゲート電極12の側面において、電荷蓄積膜9と絶縁膜11との間に絶縁膜10を形成し、メモリゲート電極12側面の絶縁膜10および11の合計の厚さを、メモリゲート電極12下部の絶縁膜11の厚さよりも厚く形成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】電荷保持特性の良好な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体層SMLと、半導体層に対向して設けられた第1絶縁層I1と、半導体層と第1絶縁層との間に設けられた第2絶縁層I2と、第1絶縁層と第2絶縁層との間に設けられた機能層I3と、第1絶縁層の半導体層とは反対の側に設けられ、互いに離間した第1ゲート電極G1及び第2ゲート電極G2と、を備えた不揮発性半導体記憶装置が提供される。機能層のうちの第1ゲート電極に対向する第1領域R1、及び、機能層のうちの第2ゲート電極に対向する第2領域R2の電荷蓄積能は、機能層のうちの第1領域と第2領域との間の第3領域R3とは異なる。

(もっと読む)

スプリットゲート不揮発性メモリセルの作製に有用な半導体構造を形成する方法

半導体層(12)に半導体デバイス(10)を形成する方法が提供される。方法は、半導体層(12)の上方に選択ゲート誘電体層(14)を形成すること、選択ゲート誘電体層(14)の上方に選択ゲート層(16)を形成すること、選択ゲート層の少なくとも一部分を除去することによって、選択ゲート層(16)の側壁を形成することを含む。方法は、選択ゲート層(16)の側壁の少なくとも一部分に、および選択ゲート層(16)の少なくとも一部分の下に、犠牲層(22)を成長させること、犠牲層(22)を除去して、選択ゲート層の側壁の少なくとも一部分の表面および選択ゲート層の下の半導体層の表面を露出させることをさらに含む。方法は、制御ゲート誘電体層(28)、電荷蓄積層(32)、および制御ゲート層(34)を形成することをさらに含む。 (もっと読む)

半導体装置

【課題】電荷蓄積膜を用いる不揮発性記憶用MOS型トランジスタと、これを選択するMOS型トランジスタが隣接するスプリットゲート構造を有する不揮発性メモリセルにおいて、電荷保持特性を向上し、ゲート電極を低抵抗化する。

【解決手段】電荷蓄積膜のコーナー部の薄膜化を抑制して電荷保持特性を向上するために、選択ゲート電極15の側壁にテーパーを設ける。また、自己整合で形成するゲート電極を低抵抗化するシリサイドを安定に行うため、選択ゲート電極15の側壁をリセスさせる。もしくは、自己整合ゲート電極上部18と選択ゲート電極上部65の間に段差を設ける。

(もっと読む)

半導体装置

【課題】記憶容量の大容量化に伴うメモリ誤動作の発生を抑制できる不揮発性メモリを含む半導体装置を提供すること。

【解決手段】半導体基板と、その表面に埋め込まれた素子分離絶縁膜と、該基板上の複数の不揮発性のメモリセルを備え、該メモリセルは、該基板上の第1絶縁膜、第1絶縁膜上の電荷蓄積層、電荷蓄積層上方の制御ゲート電極及び制御ゲート電極と電荷蓄積層の間の第2絶縁膜を備え、該メモリセルのチャネル幅方向の断面において、素子分離絶縁膜上面は該基板表面よりも高く且つ電荷蓄積層上面よりも低く、第2絶縁膜は素子分離絶縁膜上面及び電荷蓄積層上面上に設けられ、素子分離絶縁膜上面上の第2絶縁膜は電荷蓄積層上面上の第2絶縁膜よりも誘電率が低く且つ電荷蓄積層上面上の第2絶縁膜とは組成が異なる領域を含み及び複数の該メモリセルの隣接する該メモリセル間の素子分離絶縁膜上面上の制御ゲート電極は下に向かって突出している。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】N+型ソース層とフローティングゲートとのカップリング比を高くしてプログラム特性を改善すると共にメモリーセルの面積の縮小化を図る。

【解決手段】N+型ソース層4の両側にトレンチ3を形成する。トレンチ3の側壁は2つの素子分離層STI2の端面と平行なトレンチ側壁2a、トレンチ側壁2bと、STI2に垂直な面からなるトレンチ側壁3a、及びトレンチ側壁3aと平行でないトレンチ側壁3bから構成される。かかる構成のトレンチ3の上部からトレンチ側壁3aに平行で、且つP型ウエル層1に垂直又は角度をもった砒素イオン等のイオン注入を行い、トレンチ3底面からトレンチ側壁3bに延在するフローティングゲートFG6と広い面積で対峙するN+型ソース層4を形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】複数の絶縁膜及び電極膜が交互に積層された信頼性が高い不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置において、メモリアレイ領域にメモリ積層体を設け、周辺回路領域にダミー積層体を設け、ダミー積層体にダミーホール31a,31bを形成し、その内部に絶縁部材を埋め込む。そして、絶縁部材内に複数本のコンタクト35a,35b,35c,35d,35eを形成する。コンタクト35a,35bはMOSFET40のソース層36に、コンタクト35c,35dはドレイン層37に、コンタクト35eはゲート電極38に接続される。そして、1つのダミーホール内に配置された複数本のコンタクトは、同じ電位が印加されるコンタクトとするか、ダミーホールの長手方向に延びる中心線41a,41c、41d、41f、41h、41j、41k、41lから外れた位置に配置する。

(もっと読む)

絶縁層の下に埋め込まれた第2のコントロールゲートを有するSeOI上のフラッシュメモリセル

【課題】周辺回路の設計の複雑さと、セルの信頼性とを改善するメモリセルを提供する。

【解決手段】絶縁BOX層によってベース基板5から分離された半導体材料からなる薄膜を備えた半導体・オン・インシュレータ基板上の、フローティングゲート20を備え薄膜内にチャネル4を有するFETトランジスタからなるフラッシュメモリセル1Aに関する。フラッシュメモリセル1Aは2つのコントロールゲートを備え、フロント・コントロール・ゲート22が、フローティングゲート20の上方に配置され、かつ、ゲート間誘電体層23によってフローティングゲート20から分離され、バック・コントロール・ゲート6が、絶縁BOX層のみによってチャネル4から分離されるように、ベース基板5内において絶縁BOX層の真下に配置され、これらの2つのコントロールゲート22;6がセル書き込み動作を実行するために併用されるように設計されている。

(もっと読む)

半導体装置

【課題】素子特性の劣化を可及的に防止することのできる半導体装置を提供する。

【解決手段】半導体基板51と、半導体基板上に設けられたゲート絶縁膜53と、ゲート絶縁膜上に設けられた第1ゲート電極54aと、第1ゲート電極上に設けられ金属および酸素を含む電極間絶縁膜55と、電極間絶縁膜上に設けられた第2ゲート電極54bと、第1および第2ゲート電極の両側の半導体基板に設けられたソース/ドレイン領域58a、58bと、を備え、電極間絶縁膜55は、リン、砒素、アンチモン、ビスマスのうちから選択された少なくとも1つの添加元素を含み、その含有量が0.1at%以上3at%以下である。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成してからチャネル形成用半導体部を形成する方法において、結晶品質の良い単結晶Siを用いて良質なゲート絶縁膜を形成した縦型半導体装置を提供する。

【解決手段】単結晶半導体基板に少なくとも第1絶縁層を有する積層体を形成する工程S1と、前記積層体に、前記単結晶半導体基板が露出する孔を形成する工程S2と、前記孔の底面に露出している前記単結晶半導体基板を種結晶領域とすることにより、前記第1絶縁層の上にゲート電極となる単結晶半導体部を形成する工程S3と、前記孔内に埋められた前記単結晶半導体部を除去することで、前記孔の底面に前記単結晶半導体基板を再び露出させる工程S4と、前記単結晶半導体部の前記孔の側面に露出している部分にゲート絶縁膜を形成する工程S5と、前記孔にチャネル形成用半導体部を形成する工程S6と、を有する半導体装置の製造方法。

(もっと読む)

半導体記憶装置

【課題】微細化が進んだ場合であってもトランジスタのカットオフ特性を改善しつつ、選択トランジスタのカットオフ特性のバラツキ及びジャンクションリークを抑制する。

【解決手段】半導体基板100上に形成されるp型ウェル2には、ビット線BLの長手方向に沿って形成されたトレンチ3に素子分離絶縁膜4が埋め込まれている。素子分離絶縁膜4によりp型ウェル2が分離され、メモリトランジスタが形成される素子形成領域2Aが形成される。ドレインコンタクト拡散領域15’の位置における素子分離絶縁膜4の高さは、メモリトランジスタMCの位置における素子分離絶縁膜4の高さよりも高くされている。

(もっと読む)

Pチャネル型不揮発性メモリ及び半導体装置、Pチャネル型不揮発性メモリの製造方法

【課題】書き換え電圧を低くできるようにしたPチャネル型不揮発性メモリ及び半導体装置、Pチャネル型不揮発性メモリの製造方法を提供する。

【解決手段】シリコン基板1に設けられたN型ウェル領域2と、N型ウェル領域2内で互いに離れた状態で設けられた第1のP型拡散領域(ソース)及び第2のP型拡散領域(ドレイン)と、第2のP型拡散領域上に設けられたトンネル絶縁膜14bと、N型ウェル領域2のうちの第1のP型拡散領域と第2のP型拡散領域とに挟まれた領域(即ち、チャネルとなる領域)上に設けられたゲート絶縁膜14aと、ゲート絶縁膜14a上からトンネル絶縁膜14b上にかけて連続して設けられた浮遊ゲート電極15と、を備え、第2のP型拡散領域はトンネル絶縁膜14bの直下の全領域に配置されている。

(もっと読む)

81 - 100 / 477

[ Back to top ]