Fターム[5F101BH09]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | イオン注入 (487)

Fターム[5F101BH09]の下位に属するFターム

イオン注入によるトラップ形成 (10)

Fターム[5F101BH09]に分類される特許

41 - 60 / 477

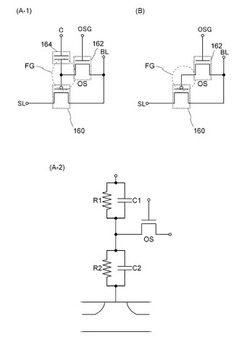

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

記憶装置、及び半導体装置

【課題】プロセスを複雑化させることなく、単位面積あたりの記憶容量を高めることができる記憶装置を提案する。

【解決手段】複数のメモリセルと、複数のワード線と、複数のビット線とを有し、複数のメモリセルは、スイッチング素子と、第1の電極及び第2の電極を有する容量素子と、をそれぞれ有し、複数のメモリセルの少なくとも1つにおいて、複数のワード線のうち一のワード線に与えられる電位に従って、スイッチング素子が複数のビット線のうち一のビット線と第1の電極の接続を制御し、なおかつ、第2の電極が複数のワード線のうち一のワード線とは異なる一のワード線に接続されている記憶装置。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果を抑制しつつ微細化を達成した半導体装置およびその作製方法を提供することを目的の一とする。

【解決手段】絶縁層にトレンチを形成し、トレンチの上端コーナー部と接する酸化物半導体膜に不純物を添加し、ソース領域およびドレイン領域を形成する。上記構造にすることで微細化することが可能である。また、トレンチを有することで、ソース電極層とドレイン電極層との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果を抑制することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】FMONOSメモリセルとCMOSトランジスタが共存する半導体装置において、トランジスタの駆動電流を高めるとともにFMONOSメモリセルとしての機能を確保する半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、主表面上に形成された、チャネルを有するMONOS型メモリセルと、主表面上に形成されたnチャネル型トランジスタと、主表面上に形成されたpチャネル型トランジスタとを備える半導体装置である。上記MONOS型メモリセル、nチャネル型トランジスタおよびpチャネル型トランジスタの上面に接するように窒化膜CS1、CS2が形成されている。上記窒化膜CS1、CS2はMONOS型メモリセル、nチャネル型トランジスタおよびpチャネル型トランジスタのチャネルに応力を付加する。

(もっと読む)

選択トランジスタ、選択トランジスタの作成方法、メモリ装置及びメモリ装置の製造方法

【課題】少ない工程数で製造でき、フラットバンド電圧のシフトを抑制できる選択トランジスタ、選択トランジスタの作成方法、メモリ装置及びメモリ装置の製造方法を提供すること。

【解決手段】直列接続された複数のメモリトランジスタを備えたメモリ装置で用いられる選択トランジスタであって、半導体基板上に形成されたトンネル絶縁層と、トンネル絶縁層上に形成された電荷蓄積層と、電荷蓄積層上に形成され、アルゴンをソースガスとするガスクラスタイオンビームが照射されたブロッキング絶縁層と、ブロッキング絶縁層上に形成されたゲート電極と、ゲート電極の両側の半導体基板中に形成されたソース/ドレイン領域と、を具備する。

(もっと読む)

半導体装置

【課題】抵抗素子を有する半導体装置に関し、集積度を低下することなく低消費電力化と高い回路精度とを実現しうる半導体装置を提供する。

【解決手段】半導体材料により形成された複数の抵抗素子と、複数の抵抗素子の近傍に配置された加熱用抵抗素子と、対向する2つの接続ノード間に加熱用抵抗素子が接続され、対向する他の2つの接続ノード間に電源線が接続された抵抗ブリッジ回路とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細配線を簡易に低抵抗化する。

【解決手段】実施形態に係わる半導体装置は、第1の方向に積み重ねられる第1乃至第3の半導体層3a,3b,3cを有し、第2の方向に延びるフィン型積層構造を有する。第1のレイヤーセレクトトランジスタTaは、第1のゲート電極10aを有し、第1の半導体層3aでノーマリオン状態である。第2のレイヤーセレクトトランジスタTbは、第2のゲート電極10bを有し、第2の半導体層3bでノーマリオン状態である。第3のレイヤーセレクトトランジスタTcは、第3のゲート電極10cを有し、第3の半導体層3cでノーマリオン状態である。第1の半導体層3aのうちの第1のゲート電極10aにより覆われた領域、第2の半導体層3bのうちの第2のゲート電極10bにより覆われた領域及び第3の半導体層3cのうちの第3のゲート電極10cにより覆われた領域は、それぞれ金属シリサイド化される。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】埋め込みビットライン型不揮発メモリの微細化に適した製造方法を提供し、かつコンタクトの位置ずれに起因するビットライン間ショートを生じ難い構造を提供する。

【解決手段】導電体膜が埋め込まれたシャロートレンチ溝内にビットライン拡散層を設けてSONOS構造セルとする。これにより、ビットライン拡散層の半導体基板主面上での面積を大きくせずにビットライン拡散層の抵抗を低くすることができ、セル面積を増大させることなく安定した電気的特性の半導体記憶装置が得られる。また、Si3N4のサイドウォールを設けてイオン注入することでビットラインを形成する。これにより、メモリセルの微細化が可能となる。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】従来のMONOS型の不揮発性半導体記憶装置の製造方法では、トップ絶縁膜のエッチング加工にウェットエッチングを用いるため、サイドエッチングが侵攻してしまうという問題があった。これにより電荷蓄積層とゲート電極との間の絶縁性が損なわれ、電気的リークが発生し、消去特性などの電気特性が低下していた。

【解決手段】本発明の不揮発性半導体記憶装置の製造方法は、2つの犠牲膜を用いることにより、トップ絶縁膜と側壁保護膜とを同時に形成するエリアを作り出し、酸化処理によってそれらを形成する。このような製造方法とすることで、メモリゲート絶縁膜のサイドエッチングが発生することはない。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】従来のMONOS型の不揮発性半導体記憶装置の製造方法では、トップ絶縁膜のエッチング加工にウェットエッチングを用いるため、サイドエッチングが侵攻してしまうという問題があった。これにより電荷蓄積層とゲート電極との間の絶縁性が損なわれ、電気的リークが発生し、消去特性などの電気特性が低下していた。

【解決手段】メモリゲート絶縁膜の形成前に保護絶縁膜を形成し、この保護絶縁膜によりメモリゲート絶縁膜のサイドエッチングを防止する製造方法とすることで、電荷蓄積層とゲート電極との間の絶縁性が向上する。そして、この保護絶縁膜を不揮発性半導体記憶装置の製造後も側壁保護膜として残してもよい。そうすると不揮発性半導体記憶装置の完成後に、他の半導体素子を形成するためのウェットエッチング工程があったとしても、メモリゲート絶縁膜がサイドエッチングされることはない。

(もっと読む)

半導体装置の製造方法

【課題】実施形態によれば、メモリストリングの下端を連結する構造を少ない工程数で形成することができる半導体装置の製造方法を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、シリコンを含む下地層にマスクを用いて選択的に不純物を注入し、下地層に、ホウ素を含むホウ素添加領域と、ホウ素添加領域よりもホウ素濃度が低い被エッチング領域とを形成する工程を有する。また、複数層の電極層を含む積層体に、被エッチング領域に達する一対のホールを形成する工程を有する。また、エッチング液を用いて被エッチング領域をホールを通じて除去し、下地層に、一対のホールのそれぞれの下端とつながった凹部を形成する工程を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】高品質な半導体装置を提供する。

【解決手段】P型の半導体基板10と、半導体基板10内に形成されるNウェル11、半導体基板10内かつNウェル11上に形成されるPウェル12、及びPウェル12上に形成されるメモリセルトランジスタMTを含むCell領域と、半導体基板10内に形成されるNウェル14、及びNウェル上14に形成されるトランジスタHVP−Trを含むHVP−Tr領域と、半導体基板10上に形成されるトランジスタHVN―Trを含むHVN―Tr領域と、半導体基板10内に形成されるNウェル22、半導体基板10内かつNウェル22上に形成されるPウェル23、およびPウェル23上に形成されるトランジスタLVNE−Trを含むLVNE−Tr領域と、を具備し、Nウェル11及びNウェル22の底面の位置はNウェル14の底面の位置よりも低く、Nウェル14の底面の位置はPウェル12及びPウェル23の底面の位置よりも低い。

(もっと読む)

半導体記憶装置

【課題】総工程数を低減することができ、コストを低廉なものにする半導体記憶装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体記憶装置10は、半導体基板13と、第1不純物領域17と、第2不純物領域15と、第1不純物領域17と第2不純物領域15との間に形成されたチャネル領域75と、チャネル領域75が位置する半導体基板13の主表面上のうち、第1不純物領域17側の主表面上に形成された第1ゲート42と、チャネル領域75が位置する半導体基板13の主表面上にうち、第2不純物領域側15の主表面上に第2絶縁膜44を介して形成された第2ゲート45と、第1ゲート45に対して第2ゲート42と反対側に位置する半導体基板の主表面上に位置し、第1ゲート42の側面上に形成された第3絶縁膜46と、第3絶縁膜46とその直下に位置する半導体基板13との界面が、第2絶縁膜44とその直下に位置する半導体基板の主表面との界面より上方に位置する。

(もっと読む)

半導体装置および半導体装置の製造方法

【目的】水素終端よりも強い界面終端構造を有する半導体装置を提供することを目的の1つとする。

【構成】実施形態の半導体装置は、絶縁膜とSi半導体部とを備えている。絶縁膜は、酸化物と窒化物と酸窒化物とのいずれかを用いて形成される。Si半導体部202は、前記絶縁膜下に配置され、硫黄(S)とセレン(Se)とテルル(Te)とのうち少なくとも1種の元素が前記絶縁膜との界面に存在する、シリコン(Si)を用いて形成される。

(もっと読む)

不揮発性メモリ及びその製造方法

【課題】

不揮発性メモリ構造を提供する。

【解決手段】

必要に応じて、LDD領域が、アクティブ領域のゲートチャネル領域の保護のためのマスクを用いてイオン注入によって形成され得る。2つのゲートが、互いに離隔され、アクティブ領域の中央領域の2つの側方のそれぞれでアイソレーション構造上に配設される。これら2つのゲートの各々は、その全体がアイソレーション構造上に配置されてもよいし、部分的にアクティブ領域の中央領域の側方部分に重なってもよい。電荷トラップ層及び誘電体層が、格納ノード機能を果たすように、2つのゲートの間且つアクティブ領域上に形成される。これらは更に、スペーサとして機能するように、2つのゲートの全ての側壁上に形成されてもよい。ソース/ドレイン領域が、ゲート及び電荷トラップ層の保護のためのマスクを用いて、イオン注入によって形成される。

(もっと読む)

半導体装置

【課題】動作特性に対する信頼性を向上させることができる半導体装置を提供する。

【解決手段】シリコンを含む基板7と、前記基板7上に設けられた積層体6と、を有する半導体装置1であって、前記積層体6は、少なくとも前記積層体6の側壁の前記基板側にフッ素を含む抑制領域13を有している。前記抑制領域13は、基板7上に設けられた絶縁膜2の前記側壁側に設けられ、フッ素濃度は、チャネル領域11のフッ素濃度よりも高い。

(もっと読む)

半導体装置およびその作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置、およびその作製方法を提供することである。

【解決手段】基板上に下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、第1の加熱処理を行って第2の酸化物半導体膜を形成した後、選択的にエッチングして、第3の酸化物半導体膜を形成し、第1の絶縁膜および第3の酸化物半導体膜上に絶縁膜を形成し、第3の酸化物半導体膜の表面が露出するように絶縁膜の表面を研磨して、少なくとも第3の酸化物半導体膜の側面に接するサイドウォール絶縁膜を形成した後、サイドウォール絶縁膜および第3の酸化物半導体膜上にソース電極およびドレイン電極を形成し、ゲート絶縁膜およびゲート電極を形成する。

(もっと読む)

半導体装置の駆動方法

【課題】新たな構造の半導体装置、及びその駆動方法を提供することを目的の一とする。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用のpチャネル型トランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態として、書き込み用トランジスタのソース電極と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態として、ノードに所定量の電荷を保持させることで行う。また、保持期間において、メモリセルを選択状態とし、且つ、読み出し用トランジスタのソース電極およびドレイン電極を同電位とすることで、ノードに蓄積された電荷を保持する。

(もっと読む)

半導体記憶装置の製造方法、及び半導体記憶装置

【課題】1つの実施形態は、例えば、トンネル電流を容易に増加できる半導体記憶装置の製造方法、及び半導体記憶装置を提供することを目的とする。

【解決手段】1つの実施形態によれば、半導体記憶装置の製造方法が提供される。半導体記憶装置の製造方法では、Ge、Sn、C、及びNのいずれかの不純物を半導体基板の表面に導入する。半導体記憶装置の製造方法では、前記不純物が導入された前記半導体基板の表面にトンネル絶縁膜が形成されるように、前記半導体基板を熱酸化する。半導体記憶装置の製造方法では、前記トンネル絶縁膜上に電荷蓄積層を有するゲートを形成する。半導体記憶装置の製造方法では、前記ゲートと自己整合的に前記半導体基板内に不純物拡散領域を形成する。

(もっと読む)

41 - 60 / 477

[ Back to top ]