Fターム[5F101BH09]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | イオン注入 (487)

Fターム[5F101BH09]の下位に属するFターム

イオン注入によるトラップ形成 (10)

Fターム[5F101BH09]に分類される特許

161 - 180 / 477

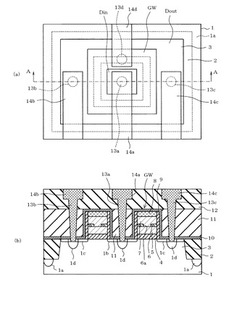

半導体装置およびその製造方法

【課題】素子形成領域の端部のチャンネル起因の閾値電圧低下の抑制や、隣接素子との間のリーク電流の低減を可能にする。

【解決手段】シリコン基板1の表面は素子分離絶縁膜2により島状の素子形成領域である活性領域3に分離されている。活性領域3内にゲート絶縁膜4を介して矩形の環状をなすゲート電極GWが形成されている。ゲート電極GWの内部側Dinに内部拡散領域1bが、外部側Doutに外部拡散領域1cが形成されている。ゲート電極GWは活性領域3内に形成されるので、端部でのチャンネル発生を抑制できる。内部拡散領域1b側に高電圧を印加することで、隣接する素子との間のリーク電流の低減が可能である。

(もっと読む)

EEPROMの製造方法

【課題】高い不純物濃度を有する拡散領域によってメモリセルトランジスタと選択トランジスタとが確実に接続されるEEPROMの製造方法を提供する。

【解決手段】半導体基板にメモリセルトランジスタのソース及びドレイン領域を形成し、半導体基板上にメモリセルトランジスタ及び選択トランジスタのゲート電極構造を形成した後に、メモリセルトランジスタのドレイン領域と部分的に重ねて選択トランジスタのソース領域を形成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】データ保持の信頼性が高い不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】シリコン基板上にそれぞれ複数の絶縁膜12及び電極膜WLを交互に積層させて積層体を形成し、この積層体に積層方向に延びる貫通ホール17を形成する。次に、貫通ホール17を介して絶縁膜12をエッチングすることにより、電極膜WL間に隙間18を形成する。次に、貫通ホール17の側面及び隙間18の内面に沿って電荷蓄積層26を形成し、貫通ホール17の内部にシリコンピラーSPを埋設する。これにより、不揮発性半導体記憶装置1を製造する。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の特性を向上させる。

【解決手段】電荷蓄積膜MI1に対して電荷を授受することで記憶動作を行う不揮発性メモリセルNVM1を有する半導体装置であって、不揮発性メモリセルNVM1は、シリコン基板1の主面s1に形成されたpウェルpw1と、主面s1上に電荷蓄積膜MI1を隔てて形成されたメモリゲート電極MG1とを有し、更に、シリコン基板1の主面s1のうち、電荷蓄積膜MI1下に位置するメモリチャネル領域ch1aにフッ素を含んでいる。

(もっと読む)

半導体装置の製造方法

【課題】所望の特性を果たす複数種類のトランジスタを少ない工程数で製造する形成方法を提供する。

【解決手段】半導体装置は、第1の深さに達する素子分離領域12と、第1導電型の第1および第2のウェルと、第1のウェルに形成され、第1の厚さのゲート絶縁膜GI1と、第2導電型のソース/ドレイン領域およびゲート電極とを有する第1のトランジスタ17と、第2のウェルに形成され、第1の厚さより薄い第2の厚さのゲート絶縁膜GI2と、第2導電型のソース/ドレイン領域およびゲート電極とを有する第2のトランジスタ18と、を有し、第1のウェルは、第1の深さと同等又はより深い深さにのみ極大値を有する第1の不純物濃度分布を有し、第2のウェルは、第1のウェルと同一の第1の不純物濃度分布に第1の深さより浅い第2の深さに極大値を有する不純物濃度分布を重ね合わせ、全体としても第2の深さにも極大値を示す第2の不純物濃度分布を有する。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】工程数を削減した不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】浮遊ゲート電極18からキャップ層30まで、およびゲート電極24からキャップ層30までをマスクとして、半導体基板11の上方から、メモリセルアレイ領域に不純物を自己整合的にイオン注入し、浮遊ゲート電極18、およびゲート電極24をそれぞれ挟むように第1不純物拡散層21を形成する工程と、半導体基板11の斜め上方から、ゲート電極24を挟むように形成された第1不純物拡散層21のうち、セルトランジスタ12と反対側に形成されている第1不純物拡散層21aに不純物を選択的にイオン注入し、第1不純物拡散層21aを、不純物の濃度が第1不純物拡散層21より高い第2不純物拡散層22に転換する工程と、を具備する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】素子分離領域の深さを抑制しながら耐圧の低下を抑制できるようにする。

【解決手段】ドレイン領域2aはゲート電極MG1の近傍に位置して形成されており、ソース領域2bはシリコン酸化膜11およびシリコン窒化膜12の膜厚分だけゲート電極MG1の側端(端部)から平面方向に離間してシリコン基板2の表層に形成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】面積の増大を抑制しつつ、高速な動作が可能な不揮発性半導体記憶装置を提供する。

【解決手段】トレンチを有する半導体基板(2)と、トレンチ内に形成された電荷蓄積層(7)と、トレンチの一側面及び底面の一部に、第1絶縁層(8)を介して形成された第1ゲート(5)と、電荷蓄積層(7)上に形成され、第1ゲート(5)の側方に第2絶縁層(7)を介して形成された第2ゲート(6)とを備えている不揮発性半導体記憶装置を攻勢する。ここにおいて、その不揮発性半導体記憶装置は、トレンチ内の半導体基板(2)中に形成された第1拡散層(3)と、トレンチ外の半導体基板中に形成された第2拡散層(4)とを備えることが好ましい。

(もっと読む)

不揮発性半導体記憶装置ならびにその駆動方法、動作方法および製造方法

【課題】不揮発性半導体記憶装置の駆動時において、書き戻しに駆動電流が大きい、書き戻し時間が長い、チャネルコンダクタンスの劣化があるなどの課題があった。

【解決手段】第1導電型のチャネル領域を介して対向する第2導電型の第1、第2の拡散層2aa,2bbと、第1導電型のチャネル領域上の2層ゲート電極とを備えたトランジスタに対して、チャネル領域と一方の拡散層を第1の電圧レベルに設定し、拡散層の他方を第2の電圧レベルに設定し、コントロールゲート6を第1または第3の電圧レベルに設定し、第1の電圧レベルと第2の電圧レベルとの電位差が第1の電圧レベルと第3の電圧レベルとの電位差よりも絶対値において大きく設定し、チャネル電流が流れるトランジスタに対してそのチャネル領域を流れる電荷の一部をフローティングゲート4に注入するようにした。

(もっと読む)

電気光学装置、電気光学装置の製造方法、及び電子機器

【課題】TFTの従来構造をそのまま生かした構造で同一基板内に不揮発性メモリを形成することができ、よりコンパクトな信頼性の高いものを得る構造を提供する。

【解決手段】本発明の電気光学装置は、画素部と、不揮発性メモリ110AのTFTの半導体層10が同一層に形成され、不揮発性メモリ110Aは、ゲート絶縁膜20を介して半導体層10上に設けられたゲート電極30を覆うように形成されたフローティングゲート絶縁膜21と、フローティングゲート絶縁膜21を介してゲート電極30と一部重なるように配置されたフローティングゲート電極31と、フローティングゲート電極31を覆うように形成されたトンネル絶縁膜22と、トンネル絶縁膜22を介してゲート電極30及びフローティングゲート電極31と一部重なるように配置されたソース電極32とを有するメモリセルを備えている。

(もっと読む)

半導体装置の作製方法

【課題】薄型化及び小型化を達成しながら、外部ストレス、及び静電気放電に耐性を有する信頼性の高い半導体装置を提供することを目的の一とする。また、作製工程においても外部ストレス、又は静電気放電に起因する形状や特性の不良を防ぎ、歩留まり良く半導体装置を作製することを目的の一とする。さらに低コストで生産性高く半導体装置を作製することを目的の一とする。

【解決手段】半導体集積回路を囲いこむように覆う導電性遮蔽体により、半導体集積回路の静電気放電による静電気破壊(回路の誤動作や半導体素子の損傷)を防止する。導電性遮蔽体はめっき法により電気的に接続するように形成する。また、導電性遮蔽体の形成にめっき法を用いるために、低コストで生産性高く半導体装置を作製することができる。

(もっと読む)

チャージトラップ型フラッシュメモリ装置及びその製造方法

【課題】通常のロジックLSI製造プロセスに最小限の変更により、ロジックLSIに組み込むのに適した構成にしたチャージトラップ型のメモリセルを提供する。

【解決手段】本発明は、ゲート絶縁膜としての高誘電率絶縁膜及びゲート電極を有するロジックFETと共に、1チップ内に混載することによりロジックLSIを半導体基板上に構成する。半導体基板上にトンネル絶縁膜として機能する絶縁膜を形成する。この絶縁膜の上に、ロジックFETの高誘電率絶縁膜と同じプロセスフローで実現される高誘電率絶縁膜をチャージトラップ層として形成する。このチャージトラップ層の上に絶縁膜を、かつその上にゲート電極を形成する。

(もっと読む)

非常に短いゲート形状を有するトランジスタとメモリセルの製造方法

【課題】強力なプログラム/消去効率及び読み出し速度を示し低い動作電圧を許容する非常に小さいゲート形状及び全体サイズを有した高性能のトランジスタ及びメモリセルを製造して、チャネル長さを劇的にスケーリングできる半導体素子及びその製造方法を提供する。

【解決手段】本発明は、半導体トランジスタを形成する方法において、半導体基板領域上に該半導体基板領域から絶縁されるゲート電極を形成する工程と、前記ゲート電極の側壁(side-walls)に沿ってオフセットスペーサを形成する工程と、前記ゲート電極と各々のソース及びドレイン領域との間のオーバーラップの広さが前記オフセットスペーサの厚さに依存するように、前記オフセットスペーサを形成した後に、前記基板領域内にソース領域及びドレイン領域を形成する工程とを含む。

(もっと読む)

非常に短いゲート形状を有するトランジスタとメモリセルの製造方法

【課題】強力なプログラム/消去効率及び読み出し速度を示し低い動作電圧を許容する非常に小さいゲート形状及び全体サイズを有した高性能のトランジスタ及びメモリセルを製造して、チャネル長さを劇的にスケーリングできる半導体素子及びその製造方法を提供する。

【解決手段】本発明は、半導体トランジスタを形成する方法において、半導体基板領域上に該半導体基板領域から絶縁されるゲート電極を形成する工程と、前記ゲート電極の側壁(side-walls)に沿ってオフセットスペーサを形成する工程と、前記ゲート電極と各々のソース及びドレイン領域との間のオーバーラップの広さが前記オフセットスペーサの厚さに依存するように、前記オフセットスペーサを形成した後に、前記基板領域内にソース領域及びドレイン領域を形成する工程とを含む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】不揮発性メモリを有する半導体装置の特性を向上させる。

【解決手段】シリコン基板1上のメモリ領域Rmに不揮発性メモリを形成する工程であって、シリコン基板1の主面に選択ゲート電極CGを形成し、いずれか一方の側壁面に隣り合うダミーゲートDGを形成する。その後、ダミーゲートDGをイオン注入マスクとしたイオン注入D01によって、メモリソース・ドレイン領域SDmを形成する。その後ダミーゲートDGを除去し、ダミーゲートDGが配置されていた箇所に、電荷蓄積膜とメモリゲート電極とを順に形成することで、メモリゲート電極の側方下部にメモリソース・ドレイン領域SDmが配置された構造を形成する。本工程では、メモリソース・ドレイン領域SDmを形成するためのイオン注入D01を施した後に、電荷蓄積膜とメモリゲート電極とを形成する。

(もっと読む)

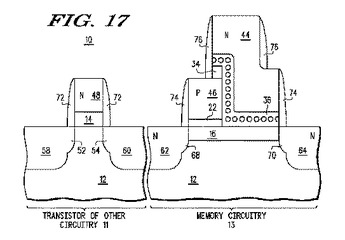

スプリット・ゲート・メモリ・デバイスの形成方法および装置

スプリット・ゲート・メモリ・デバイス(10)は、第1の仕事関数を有する選択ゲート(46)を基板(12)の第1の部分の上に有する。第2の仕事関数を有する制御ゲート(44)は、第1の部分に隣接する基板の第2の部分の上にある。スプリット・ゲート・メモリ・デバイス(10)の多数キャリアが電子であるとき、第1の仕事関数は第2の仕事関数よりも大きい。スプリット・ゲート・メモリ・デバイス(10)の多数キャリアがホールであるとき、第1の仕事関数は第2の仕事関数よりも小さい。基板(12)内の第1の電流電極(62)および第2の電流電極(64)は、制御ゲートおよび選択ゲートの下にあるチャネルによって分離される。制御ゲートおよび選択ゲートの異なる仕事関数は、デバイス性能を最適化するために各ゲートに対して異なる閾値電圧をもたらす。nチャネルデバイスでは、選択ゲートはp導電型であり、制御ゲートはn導電型である。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセル間の干渉を抑制できる不揮発性半導体記憶装置を提供する。

【解決手段】NAND型メモリ1において、半導体基板11の表面上に、トンネル絶縁層12、電荷蓄積層13、電荷ブロック層14を設け、その上に、チャネル長方向に沿ってそれぞれ複数の制御ゲート電極15及びセル間絶縁膜16を交互に設ける。そして、電荷ブロック層14におけるセル間絶縁膜16の直下域に相当する部分14bに塩素を導入し、部分14bの誘電率を電荷ブロック層14における制御ゲート電極15の直下域に相当する部分14aの誘電率よりも低くする。

(もっと読む)

半導体装置およびその製造方法、ならびにその半導体装置を用いた集積半導体装置および不揮発性半導体記憶装置

【課題】絶縁ゲート型電界効果トランジスタにおいて低電圧下で急峻なスイッチング特性を有する半導体素子を提供する。

【解決手段】大規模集積回路に用いられているプレーナ型のロジック回路用MOSFETにおいて、ドレイン拡散層電極のなかに、ダイオード素子と抵抗素子が並列配置されるように形成することで、低電圧であってもゲート電圧変化に対してドレイン電流が急峻な変化を示す高性能トランジスタが実現できる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 メモリセルの最小面積をより小さくし、高集積化、高密度化、大容量化を図ることが可能になるNAND型の不揮発性半導体記憶装置を提供する。

【解決手段】 絶縁層と半導体層が半導体基板10の表面に垂直な第1方向に沿って交互に積層され、且つ、1対の互いに対向する側面を備えて畝状に構成された積層構造部Lと、積層構造部Lの1対の側面の両方に接し、側面内における半導体基板10の表面に平行な第2方向に一定の幅を有するように形成された電荷蓄積層CSと、電荷蓄積層CSの表面に接し、積層構造部L及び電荷蓄積層CSを覆うように形成された第1導電体層CG1を備え、半導体層の第1導電体層CG1の第2方向の両側部分にソースドレイン領域A2が形成され、ソースドレイン領域A2、電荷蓄積層CS及び第1導電体層CG1により、積層構造部Lの1対の側面に、1つの半導体層に対し、1対のメモリセルが構成されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】一度の酸化処理でONO膜の上側酸化膜を下側酸化膜よりも厚く形成することができるミラービットの半導体装置の製造方法を提供する。

【解決手段】基板10上に第1酸化膜11、この第1酸化膜11よりも膜厚が薄い窒化膜12、第1酸化膜11よりも膜厚が薄い第2酸化膜13、及びゲート電極14を積層する工程と、第1酸化膜11の端部及び第2酸化膜13の端部を除去して窒化膜12を一部露出する工程と、第1酸化膜11が除去された基板10上に第3酸化膜15を形成すると同時に、窒化膜12の露出部分を酸化して第4酸化膜16を形成し且つゲート電極14の周囲に第5酸化膜17を形成して、第4酸化膜16と第5酸化膜17とが一体化した、第3酸化膜15よりも厚い酸化膜を形成する工程と、第3酸化膜15と第4酸化膜16との間に電荷蓄積層18aを形成する工程と、をこの順に行う。

(もっと読む)

161 - 180 / 477

[ Back to top ]