Fターム[5F102FA03]の内容

接合型電界効果トランジスタ (42,929) | 目的、効果 (2,241) | ソース・ドレイン抵抗、コンタクト抵抗の低減 (386)

Fターム[5F102FA03]に分類される特許

101 - 120 / 386

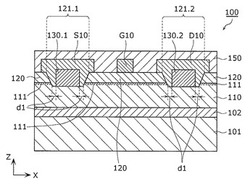

電界効果トランジスタ

【課題】歩留りの低下を抑制する。

【解決手段】開口部121.1の形成により、第1の半導体層110の上面のうち、上方に第2の半導体層120が形成されていない部分の少なくとも一部には、絶縁体130.1が形成される。開口部121.1には、絶縁体130.1を覆うようにソース電極S10が形成される。ソース電極S10は、第1の半導体層110と前記第2の半導体層120との界面と接するように形成される。

(もっと読む)

窒化物半導体装置

【課題】活性層の上に電極パッドを形成する場合に生じる問題を解決し、オン抵抗の上昇を抑えた窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、活性領域102Aを有する窒化物半導体層積層体102と、活性領域の上に互いに間隔をおいて形成されたフィンガー状の第1の電極131及び第2の電極132とを備えている。第1の電極の上に接して第1の電極配線151が形成され、第2の電極の上に第2の電極配線152が接して形成されている。第1の電極配線及び第2の電極配線を覆うように第2の絶縁膜が形成され、第2の絶縁膜の上に第1の金属層161が形成されている。第1の金属層は、第2の絶縁膜を介して活性領域の上に形成され、第1の電極配線と接続されている。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】本発明は、ソース電極およびドレイン電極の熱耐久性を向上させて、かつ製造過程においてオーミック性に与える不安定要因を取り除き信頼性および量産性の高いGaN系HEMTを提供する。

【解決手段】GaN系HEMTは、基板と、窒化ガリウム系半導体と、融点が3000℃と高融点金属のタンタルと低融点金属のアルミニウムが前記窒化ガリウム系半導体上に積層されてなる前記ソースおよび前記ドレイン電極を備えている。前記ソース電極および前記ドレイン電極は、前記タンタルと前記アルミニウムの積層膜厚の比(前記アルミニウム膜厚/前記タンタル膜厚)を10以上にし、積層後のアニール処理温度が510℃以上、600℃未満で処理されて成る。

(もっと読む)

半導体装置の製造方法

【課題】コンタクト抵抗率を低く抑えることが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、Al組成比が0.2以上のAlGaN層をエッチングして、RMS粗さが0.3nm未満の底面を有する凹部を形成する工程と、前記凹部の底面に接して、4nmから8nmの厚さの第1Ta層を形成する工程と、前記第1Ta層に熱処理を施して、前記AlGaN層にオーミック接触させる工程と、を有する半導体装置の製造方法である。

(もっと読む)

ワイドギャップ半導体基板およびワイドギャップ半導体装置の製造方法

【課題】ワイドギャップ半導体基板の位置検出を、可視光を用いて高精度に行う。

【解決手段】一実施形態によれば、ナローギャップ半導体基板(例えばSi基板2)の主面の所定の位置に彫り込み型のアライメントマーク4が形成されたナローギャップ半導体基板のその主面上にワイドギャップ半導体層(例えばGaN層19)をエピタキシャル成長したことにより、基板位置決め用のアライメントマークが予め埋め込まれているワイドギャップ半導体基板を提供する。

(もっと読む)

半導体トランジスタおよびその製造方法

【課題】FETの閾値電圧のばらつきのない半導体トランジスタおよびその製造方法を提供する。

【解決手段】半導体トランジスタ100は、基板1と、基板1の上方に形成された第1化合物半導体層103と、第1化合物半導体層103上に形成され、第1化合物半導体層103よりもバンドギャップの大きい第2化合物半導体層104と、第2化合物半導体層104内の少なくとも一部に、酸素がドープされた酸素ドープ領域105と、第2化合物半導体層104上に形成された第3化合物半導体層106と、第1化合物半導体層103に電気的に接続されたソース電極107およびドレイン電極109と、酸素ドープ領域105の上方に、酸素ドープ領域105に接するように形成されたゲート電極108とを有する。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】半導体層とソース電極、ドレイン電極とのコンタクト抵抗が小さい電界効果トランジスタを提供すること。

【解決手段】SiC基板11の表面上に形成された、活性層を含む半導体層12と、半導体層12上に互いに離間して形成され、チタン層18、およびこのチタン層18に対する膜厚比が12〜15であるアルミニウム層19を有するソース電極16およびドレイン電極15と、半導体層12上のうち、ソース電極16とドレイン電極15との間に形成されたゲート電極17と、を具備する電界効果トランジスタ。

(もっと読む)

電界効果トランジスタ

【課題】オン抵抗の低減を図ることができる電界効果トランジスタ(FET)を提供する。

【解決手段】FET101は、化合物半導体基板1と、化合物半導体基板1上に形成され、当該基板側から見て、n型キャリアが蓄積するチャネル層5、ショットキー層8、及びキャップ層9を順次含む半導体積層構造10と、ゲート電極20、ソース電極21、及びドレイン電極22とを備えている。キャップ層9は、ショットキー層8側から見て、自然超格子構造を有するアンドープの又はn型キャリアが添加された第1のInGaP層9Aと、自然超格子構造を有しないn型キャリアが添加された第2のInGaP層9Bとを順次含んでいる。

(もっと読む)

ホモエピタキシャルIII−V族窒化物品、デバイス、およびIII−V族窒化物ホモエピタキシャル層を形成する方法

【課題】LEDや高電子移動度トランジスタなどのデバイス用として有用なIII−V族窒化物品の提供。

【解決手段】自立III−V族窒化物基板上に堆積したIII−V族窒化物ホモエピタキシャル層を含むホモエピタキシャルIII−V族窒化物品であって、前記III−V族窒化物ホモエピタキシャル層が1E6/cm2未満の転位密度を有しており、(i)前記III−V族窒化物ホモエピタキシャル層と前記自立III−V族窒化物基板の間に酸化物を有するか、(ii)前記III−V族窒化物ホモエピタキシャル層と前記自立III−V族窒化物基板の間にエピ中間層を有するか、

(iii)前記自立III−V族窒化物基板がオフカットされており、前記III−V族窒化物ホモエピタキシャル層が非(0001)ホモエピタキシャルステップフロー成長結晶を含むことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクトプラグを介さずに、MOSトランジスタの第2ソース/ドレイン電極に相変化材料領域を直接、接続することで、電圧降下のロスを抑制し、効率よく相変化材料を加熱する。これにより、消費電力を抑制する。

【解決手段】半導体装置は、第1ソース/ドレイン電極及び第2ソース/ドレイン電極を有するMOSトランジスタと、コンタクトプラグを介して第1ソース/ドレイン電極に接続されたGND配線と、相変化材料領域と、相変化材料領域上に設けられた上部電極と、を有する。相変化材料領域は、第2ソース/ドレイン電極に直接、接続されている。

(もっと読む)

III族窒化物半導体電子デバイス、III族窒化物半導体電子デバイスを作製する方法

【課題】Id―max特性低下を低減可能なIII族窒化物半導体電子デバイスが提供される。

【解決手段】III族窒化物半導体電子デバイス11では、チャネル層21はAlGaNからなると共に、バリア層23はチャネル層21より大きなバンドギャップのAlGaNからなる。チャネル層21が、GaNではなく、AlGaNからなるので、III族窒化物半導体電子デバイス11においてId―max特性低下を低減可能である。また、第1及び第2の電極17、19は、それぞれ、チャネル層21の第1及び第2の部分21a、21b上に設けられる。チャネル層21において第1の部分21aの不純物濃度が第2の部分21bの不純物濃度と同じであるから、チャネル層21における第1の部分にイオン注入が行われていない。半導体積層15に部分的にイオン注入を行っていない。このイオン注入の使用回避により、Id―max特性低下を更に低減可能である。

(もっと読む)

窒化物半導体素子

【課題】ノーマリオフ特性を有する低オン抵抗で高耐圧の窒化物半導体素子を提供する。

【解決手段】基板上に設けられた第1導電型の窒化物半導体からなる第1半導体層5と、前記第1半導体層の上に設けられ、前記第1半導体層のシートキャリア濃度と同量のシートキャリア濃度を有する第2導電型の窒化物半導体からなる第2半導体層6と、を備える。前記第2半導体層の上には、前記第2半導体層よりも禁制帯幅が広い窒化物半導体からなる第3半導体層7が設けられる。前記第2半導体層に電気的に接続された第1主電極10と、前記第1主電極と離間して設けられ、前記第2半導体層に電気的に接続された第2主電極20と、をさらに備え、前記第1主電極と前記第2主電極との間において、前記第3半導体層および前記第2半導体層を貫通して前記第1半導体層に達する第1のトレンチの内部に絶縁膜33を介して設けられた制御電極30を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において低抵抗なオーミック性を有し、酸・アルカリによる腐食に対し高い耐性を持つ電極を得ることを目的とする。

【解決手段】本発明に係る第1の半導体装置は、窒化物半導体層1と、窒化物半導体層上に設けられた電極とを備え、窒化物半導体層1は電極下に、それ以外の部分よりも高濃度にn型不純物を含む高濃度不純物領域2を備え、電極は、窒化物半導体層1上に設けられた第一金属層3と、第一金属層3上に設けられた第二金属層4と、第二金属層4上に設けられた第三金属層5と、を備え、第一金属層3は第二金属層4よりも窒化物半導体層1との高い密着性を有する金属を含み、第三金属層5は水素よりもイオン化傾向の小さい金属を含む。

(もっと読む)

半導体基板、トランジスタおよび半導体基板の製造方法

【課題】大きな電流密度あるいは大きな利得での駆動と低いオン抵抗とを両立したHFETを得る。

【解決手段】InxAlyGa1−x−yAszP1−z(ただしx、yおよびzは、0≦x<1、0≦y<1、0<x+y≦1および0≦z≦1を満たす)からなる半導体層を有し、前記半導体層が、トランジスタのソースとして機能するソース領域の全部または一部と、前記トランジスタのドレインとして機能するドレイン領域の全部または一部と、前記ソース領域および前記ドレイン領域の間に配置され、前記トランジスタのゲートとして機能するゲート領域の全部または一部とを含み、前記ゲート領域の全部または一部における前記半導体層の最大電子親和力が、前記ソース領域の全部または一部における前記半導体層の最小電子親和力または前記ドレイン領域の全部または一部における前記半導体層の最小電子親和力より小さい半導体基板を提供する。

(もっと読む)

ノーマリオフ型GaN系電界効果トランジスタ

【課題】ゲート耐電圧が高くかつオン抵抗が低減されたノーマリオフ型GaN系FETを提供する。

【解決手段】ノーマリオフ型GaN系FETは、第1種GaN系半導体からなるチャネル層4と、このチャネル層上で互いに隔てて設けられた第2種GaN系半導体からなる一対の電子供給層5と、これら電子供給層の間でチャネル層を覆うゲート絶縁膜7と、チャネル層にオーミックコンタクトしているソース電極およびドレイン電極と、ゲート絶縁膜上に形成されたゲート電極とを備え、ゲート絶縁膜はチャネル層上に順次堆積された第1と第2の絶縁層を含み、第1絶縁層7aはSiの酸化物、窒化物および酸窒化物のいずれかからなりかつ5nm以下の厚さを有し、第2絶縁層7bは第1絶縁層に比べて大きなε×Ecを有し、ここでεは誘電率を表し、Ecは絶縁破壊電界を表している。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧向上や短チャンネル効果の抑制を可能とする半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、半導体基板であるSiC基板1上に形成された、バッファ層2と、バッファ層2上に形成された、バッファ層2よりもバンドギャップが小さいチャネル層3と、チャネル層3上に形成された、チャネル層3よりもバンドギャップが大きいバリア層4と、バリア層4上に互いに離間して形成された、ソース、ドレイン電極7、8と、ソース、ドレイン電極7、8下から、バリア層4を通ってチャネル層3中にそれぞれ達する、不純物領域5とを備え、不純物領域5の下端は、バッファ層2に達しない。

(もっと読む)

半導体装置

【課題】III-V族窒化物半導体に設けるオーミック電極のコンタクト抵抗を低減しながらデバイスの特性を向上できるようにする。

【解決手段】半導体装置(HFET)は、SiC基板11上にバッファ層12を介在させて形成された第1の窒化物半導体層13と、該第1の窒化物半導体層13の上に形成され、該第1の窒化物半導体層13の上部に2次元電子ガス層を生成する第2の窒化物半導体層14と、該第2の窒化物半導体層14の上に選択的に形成されたオーム性を持つ電極16、17とを有している。第2の窒化物半導体層14は、底面又は壁面が基板面に対して傾斜した傾斜部を持つ断面凹状のコンタクト部14aを有し、オーム性を持つ電極16、17はコンタクト部14aに形成されている。

(もっと読む)

半導体素子用エピタキシャル基板および半導体素子

【課題】InAlN/GaNヘテロ構造を有し、かつオーミックコンタクト特性の優れた半導体素子用のエピタキシャル基板を提供する。

【解決手段】半導体素子用エピタキシャル基板10Aが、下地基板1と、GaNからなるチャネル層3と、AlNからなるスペーサ層4と、III族元素としてInとAlとGaとを含む障壁層5と、を備え、障壁層が、InxAl1-xN(0<x<1)からなるマトリックス層にGa原子がドープされ、障壁層のGa原子の濃度が1.2×1020cm-3以下であるようにする。

(もっと読む)

凹部バリア層を備えた高電子移動度トランジスタ

【課題】高電子移動度トランジスタ(HEMT)で、凹部バリア層を備え、バリア層間にゲート電極を形成することにより、エンハンスメント型FETを提供する。

【解決手段】基板上104上にバッファ108層を形成し、バッファ層上にスペーサ層112を形成し、スペーサ層上にバリア層116を形成する。バリア層内に凹部を形成し、凹部を通して、少なくてもその一部が前記スペーサ層上に配置されるようにゲート構造140を形成する。

(もっと読む)

半導体装置

【課題】コンタクト抵抗が小さいオーミック電極を備えたIII−V族窒化物半導体を用いた半導体装置を実現できるようにする。

【解決手段】半導体装置は、基板11の上に順次形成された、第1のIII−V族窒化物半導体層12及び第1のIII−V族窒化物半導体12と比べてバンドギャップが大きい第2のIII−V族窒化物半導体層13と、p型の導電型を有する第3のIII−V族窒化物半導体層21と、第1のオーミック電極14とを備えている。第1のオーミック電極14は、下部が第2のIII−V族窒化物半導体層13及び第3のIII−V族窒化物半導体層21を貫通し且つ第1のIII−V族窒化物半導体層12における2次元電子ガス層よりも下側の領域に達するように形成されている。

(もっと読む)

101 - 120 / 386

[ Back to top ]