Fターム[5F102FA03]の内容

接合型電界効果トランジスタ (42,929) | 目的、効果 (2,241) | ソース・ドレイン抵抗、コンタクト抵抗の低減 (386)

Fターム[5F102FA03]に分類される特許

81 - 100 / 386

化合物半導体装置およびその製造方法

【課題】

本発明は、ソース電極およびドレイン電極の熱耐久性を向上させて、かつ製造過程においてオーミック性に与える不安定要因を取り除き信頼性および量産性の高いGaN系HEMTを提供する。

【解決手段】

化合物半導体装置は、基板と、前記基板上に形成された窒化ガリウム系半導体と、前記窒化ガリウム系半導体上に形成された窒化ガリウム系保護層と、前記窒化ガリウム系保護層上にタンタルとアルミニウムが任意の順に積層されてなるオーミック電極とを備え、前記オーミック電極が形成された箇所の前記窒化ガリウム系保護層の膜厚は、前記オーミック電極が形成されていない箇所の前記窒化ガリウム系保護層の膜厚よりも薄い。

(もっと読む)

半導体装置およびその製造方法

【課題】低いオン抵抗を得ながら、優れた耐圧性能を持つ、縦型の半導体装置およびその製造方法を提供する。

【解決手段】開口部28はn−型GaNドリフト層4にまで届いており、開口部の壁面を覆うように位置する再成長層27と、p型GaNバリア層6と、ゲート電極Gと、ソース電極Sとを備え、チャネルが電子走行層22内の電子供給層26との界面に生じる二次元電子ガスにより形成され、p型GaNバリア層6がGaN系積層体15の表層をなし、かつソース電極Sが、再成長層27およびp型GaNバリア層6に接して位置することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 p型GaNバリア層の電位を確実に固定することでピンチオフ特性、耐圧性能の向上を安定して得ることができる縦型の半導体装置を提供する。

【解決手段】 GaN系積層体15に開口部28が設けられており、開口部の壁面を覆うように位置するチャネルを含む再成長層27と、ソース電極Sとオーミック接触するn+型ソース層8と、p型GaNバリア層6と、その間に位置するp+型GaN補助層7とを含み、p型GaNバリア6の電位をソース電位に固定するために、p+型GaN補助層7が、n+型ソース層8とトンネル接合を形成することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 縦型GaN系半導体装置において、p型GaNバリア層による耐圧性能の向上を得ながら、オン抵抗を低くできる半導体装置を提供する。

【解決手段】 開口部28壁面に位置するチャネルを含む再成長層27と、端面が被覆されるp型バリア層6と、p型バリア層上に接するソース層7と、再成長層の上に位置するゲート電極Gと、開口部の周囲に位置するソース電極Sとを備え、ソース層が超格子構造で構成され、該超格子構造が、p型バリア層よりも小さい格子定数を持つ第1の層(a層)と、該第1の層よりも格子定数が大きい第2の層(b層)との積層体である、ことを特徴とする。

(もっと読む)

保護層および低損傷陥凹部を備える窒化物ベースのトランジスタならびにその製作方法

【課題】窒化物ベースの半導体チャネル層上に窒化物ベースの半導体バリア層を形成すること、および窒化物ベースの半導体バリア層のゲート領域上に保護層を形成することによって、トランジスタが製作される。

【解決手段】パターニングされたオーム性接触金属領域が、バリア層上に形成され、第1および第2のオーム性接触を形成するためにアニールされる。アニールは、保護層をゲート領域上に載せたままで実施される。バリア層のゲート領域上に、ゲート接点も形成される。ゲート領域内に保護層を有するトランジスタも形成され、バリア層の成長させたままのシート抵抗と実質的に同じシート抵抗をもつバリア層を有するトランジスタも同様である。

(もっと読む)

接合型電界効果トランジスタを備えた半導体装置およびその製造方法

【課題】埋込ゲート層とゲート配線とのコンタクト構造をより微細化できる構造としたJFETを有する半導体装置を提供する。

【解決手段】埋込ゲート層10とゲート配線12との電気的な接続をトレンチ13内に形成したp+型コンタクト埋込層14によって行うようにする。これにより、p+型コンタクト埋込層14のみしか配置されないトレンチ13の幅を、従来の半導体装置のように層間絶縁膜やゲート配線などが配置されるトレンチと比較して、狭くすることが可能となる。したがって、埋込ゲート層10とゲート配線12とのコンタクト構造をより微細化できる構造としたJFETを有する半導体装置とすることが可能となる。

(もっと読む)

化合物半導体装置

【課題】窒化物化合物半導体装置において、ゲートリーク電流を抑制する。

【解決手段】化合物半導体装置20は、基板21と、前記基板上方に形成された窒化物半導体よりなるキャリア走行層22を含む半導体積層構造と、前記半導体積層構造上方に形成されたゲート電極26、ソース電極27A、ドレイン電極27Bと、前記半導体積層構造上方であって、ゲート電極とソース電極の間、及び、ゲート電極とドレイン電極との間に形成された絶縁膜28と、前記絶縁膜のうち、ゲート電極とソース電極の間、及びゲート電極とドレイン電極の間に形成された開口と、前記開口に埋め込まれたアルミナ膜29と、を備える。

(もっと読む)

ヘテロ接合型電界効果トランジスタ

【課題】ゲートのリーク電流を少なくする。

【解決手段】サファイアからなる基板11上に膜厚が30nmのGaNからなる核形成層12を形成し、核形成層12上に膜厚が2μmのGaNからなるバッファ層13を形成し、バッファ層13上に膜厚が20nmでありかつIn組成が0.25のInAlNからなるバリア層16の第1の層14を形成し、第1の層14上に膜厚が20nmでありかつIn組成が0.15のInAlNからなるバリア層16の第2の層15を形成し、第2の層15上にAl/TiまたはTi/Auからなるソース電極17、ドレイン電極18をオーミック接合により形成し、第2の層15が除去された部分にNi/Auからなるゲート電極19を形成する。

(もっと読む)

電界効果トランジスタ

【課題】 本発明は、低消費電力で動作する論理回路に応用できる電界効果トランジスタを提供することを目的とするものである。

【解決手段】 ソース電極とソース電極が接する半導体の伝導帯又は価電子帯との間に障壁を有しており、ソース電極から障壁を通して流れ込む電子又はホールをゲート電圧により調整できる構成を有することを特徴とするnチャンネル又はpチャンネルの電界効果トランジスタ。

(もっと読む)

半導体素子

【課題】 GaN基板上に結晶成長する各半導体層の平坦性向上した半導体基板を実現し、この半導体基板を基礎として、特性の高性能化された半導体素子を提供する。

【解決手段】n型基板11と、n型基板11上に積層された窒化物系III−V族化合物半導体単結晶からなるn型ドリフト層24と、n型ドリフト層24上に設けられた窒化物系III−V族化合物からなるp型ベース層25と、p型ベース層25上に設けられた窒化物系III−V族化合物からなるn型エミッタ層26と、n型基板11とn型ドリフト層24との間に設けられた、Siを5x1017cm-3以上2x1019cm-3以下含有する層とを備える。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】窒化物半導体層の表面に形成したオーミック電極のコンタクト抵抗を低減した窒化物半導体装置およびその製造方法を提供すること。

【解決手段】第一の窒化物半導体層3と、第一の窒化物半導体層3の上に形成された第二の窒化物半導体層4と、第二の窒化物半導体層4の表面に形成されるオーミック電極としてのカソード電極6と、を備え、第二の窒化物半導体層4の表面におけるカソード電極6が形成される領域に、凹凸構造を有するコンタクト部4aが形成され、このコンタクト部4aの表面粗さ(RMS)が0.25nm以上5nm以下であり、かつコンタクト部4aの表面の酸素の組成比率が5at.%以下に設定されている。

(もっと読む)

半導体装置及びその製造方法

【課題】GaAsデバイスにおいて、空洞上に浮遊するGaAs層に素子形成を行うことにより、浮遊容量を抑え、高速化・低電力化を図ることが可能な半導体装置とその製造方法を提供する。

【解決手段】本発明の実施形態は、半導体基板11上に形成される空洞14と、空洞14上に形成されるGaAsエピタキシャル層13と、GaAsエピタキシャル層13上に形成されるゲート電極15と、それぞれGaAsエピタキシャル層13上に形成され、隣接するゲート電極15を挟むように形成される一対のソース電極16及びドレイン電極17と、を備える。

(もっと読む)

III−V族化合物半導体エピタキシャルウェハ及びその製造方法

【課題】コンタクト層に不純物として供給するTe、Seのメモリーの影響を小さくしつつ、コンタクト抵抗を低減し、かつ、特性変動や信頼性低下を抑制しつつ、電子供給層の不純物濃度を高め、オン抵抗を低減したIII−V族化合物半導体エピタキシャルウェハを提供する。

【解決手段】単結晶基板11上に、GaAs層、AlGaAs層からなるバッファ層12a,12b、n型不純物を含有するAlGaAs層13,17又はInGaP層若しくはSiプレナードープ層からなる電子供給層、InxGa(1-x)As層からなるチャネル層15、アンドープ又は低濃度n型不純物を含有するAlGaAs層からなるショットキー層18、n型不純物を含有するInxGa(1-x)As層からなるコンタクト層20a、20bを積層したHEMT構造を有し、チャネル層のxを0.3≦x≦0.35とし、コンタクト層のxを0.55≦x≦0.60としたものである。

(もっと読む)

化合物半導体エピタキシャルウェハ及びその製造方法

【課題】面内にわたって表面抵抗率を均一化し、得られるHEMT素子の製品抵抗のバラツキを低減した化合物半導体エピタキシャルウェハ及びその製造方法を提供する。

【解決手段】GaAsからなる基板1上に、少なくともAlGaAsからなるバッファ層3、AlGaAsからなる下部電子供給層4、GaAsもしくはInGaAsからなる電子走行層5、AlGaAsからなる上部電子供給層6、AlGaAsからなるショットキー層7、及びn型不純物を含有するGaAsからなるオーミックコンタクト層8が順次形成された化合物半導体エピタキシャルウェハ10において、オーミックコンタクト層8の外周部のキャリア濃度を中心部のキャリア濃度より高くしたものである。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】制御性の良い製造方法のみで形成することができる高周波数動作が可能なノーマリオフ型の窒化物半導体装置を提供する。

【解決手段】ソース電極5とドレイン電極6との間の電子供給層4上に、電子供給層とショットキー接触する浮遊電極8を配置し、この浮遊電極8上に絶縁膜9を介してゲート電極7を配置する。そして、ゲート電極に正バイアス印加し、浮遊電極に電子を蓄積される。

(もっと読む)

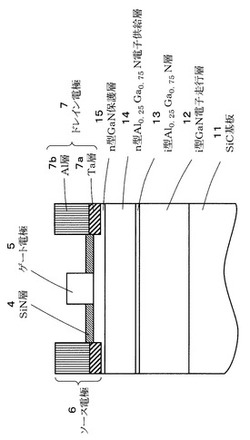

窒化物半導体装置

【課題】歩留まり良く形成することができ、高い信頼性を保つことができる、高周波特性が優れた窒化物半導体装置を提供する。

【解決手段】ソース電極5とドレイン電極6との間の電子供給層4上に、電子供給層とショットキー接触する浮遊電極8を配置し、この浮遊電極上に絶縁膜9を介してゲート電極7を配置する。特に絶縁膜を強誘電体材料とすると好ましい。

(もっと読む)

ヘテロ接合電界効果トランジスタの製造方法

【課題】電流コラプスを抑制し、且つゲートリーク電流を低減するヘテロ接合電界効果トランジスタの製造方法の提供を目的とする。

【解決手段】本発明に係るヘテロ接合電界効果トランジスタの製造方法は、(a)チャネル層30、バリア層40、キャップ層50が順に積層された積層体を備える窒化物半導体層を準備する工程と、(b)前記窒化物半導体層上にSiを含まないキャップ膜110を形成する工程と、(c)工程(b)の後、前記窒化物半導体層に選択的に不純物を注入し、熱処理により前記不純物を活性化して不純物領域60を形成する工程と、(d)工程(c)の後、キャップ膜110を除去して不純物領域60上にソース電極80及びドレイン電極90を形成する工程と、(e)前記窒化物半導体層の少なくとも一部を除去した領域にゲート電極100を形成する工程と、を備える。

(もっと読む)

ヘテロ接合電界効果トランジスタ及びその製造方法

【課題】電流コラプスを抑制し、且つゲートリーク電流を低減するヘテロ接合電界効果トランジスタとその製造方法の提供を目的とする。

【解決手段】本発明に係るヘテロ接合電界効果トランジスタは、バリア層40及びバリア層40上に形成されたキャップ層50を含む窒化物半導体層と、前記窒化物半導体層に下部を埋没するようにして前記窒化物半導体層上に設けられたゲート電極90と、前記窒化物半導体層上に形成されたSiを含まない絶縁膜からなる表面保護膜100とを備える。

(もっと読む)

半導体装置

【課題】本発明は、外部ノイズ等の過大電流に起因するHEMTの損傷、破壊若しくは発火を防止することができる半導体装置を提供する。

【解決手段】半導体装置1は、第1の半導体層31と、第2の半導体層32と、二次元キャリアガス層33と、ソース電極41と、ドレイン電極42と、ゲート電極5と、二次元キャリアガス層33上においてゲート電極5とドレイン電極42との間に配設された補助電極6と、を備え、二次元キャリアガス層33のゲート電極5とソース電極6との間のチャネル抵抗R1に比べて、二次元キャリアガス層33のゲート電極5と補助電極6との間のチャネル抵抗R2が高く設定されている。

(もっと読む)

半導体装置の製造方法

【課題】信頼性を向上させることが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、窒化物半導体層11の表面に、パワー密度が0.2〜0.3W/cm2である酸素プラズマ処理を行う工程を有する半導体装置の製造方法である。本発明によれば、酸素プラズマ処理によって、窒化物半導体層11に導電層26が形成されることにより、イオンマイグレーション現象が抑制される。このため、半導体装置の信頼性が向上する。

(もっと読む)

81 - 100 / 386

[ Back to top ]