Fターム[5F102GD10]の内容

接合型電界効果トランジスタ (42,929) | ゲート接合のタイプ (3,160) | その他(MOS、擬似MIS) (744)

Fターム[5F102GD10]に分類される特許

201 - 220 / 744

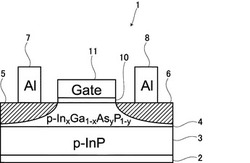

半導体デバイス、その製造方法及び集積回路

【課題】電極領域の抵抗を従来よりも一段と低減させることができる半導体デバイス、その製造方法及び集積回路を提供する。

【解決手段】III−V族化合物半導体層4上にニッケル層17を形成し、RTA処理により加熱することで、ニッケルIII−V族合金(Ni-InxGa1-xAsyP1-y合金)からなるソース領域5及びドレイン領域6が形成される。これにより、MOSFET1では、III−V族化合物半導体層4に対して単に不純物をインプラテーションで注入して形成された従来のソース領域及びドレイン領域の寄生抵抗に比べて、ソース領域5及びドレイン領域6の寄生抵抗を一段と低減させることができる。

(もっと読む)

半導体装置

【課題】本発明は、オーバーシュートの発生を減少することができ、素子破壊を防止することができるとともに、スイッチング動作速度の高速化を実現することができるスイッチング素子を備えた半導体装置を提供する。

【解決手段】半導体装置1は、第1の半導体層31と、第2の半導体層32と、二次元キャリアガス層33と、第1の主電極41と、第2の主電極42と、第1のゲート電極51と、第2のゲート電極52とを備える。第1のゲート電極51は、第1の主電極41の一部と対向する第2の主電極42の一部との間に配設される。第2のゲート電極52は、第1の主電極41の他の一部と対向する第2の主電極42の他の一部との間において、第1のゲート電極51との間に分離領域6を介在し配設され、第1のゲート電極51に対して独立に制御される。

(もっと読む)

半導体基板および絶縁ゲート型電界効果トランジスタ

【課題】絶縁ゲート型(MIS型)のP−HEMT構造において、チャネル層のキャリア移動度を向上し、界面準位の影響を低減した、良好なトランジスタ性能を実現できる技術を提供する。

【解決手段】ベース基板と、第1結晶層と、絶縁層とを有し、前記ベース基板、前記第1結晶層および前記絶縁層が、前記ベース基板、前記第1結晶層、前記絶縁層の順に位置し、前記第1結晶層が、GaAsまたはAlGaAsに擬格子整合できるInxGa1−xAs(0.35≦x≦0.43)からなる半導体基板を提供する。前記第1結晶層は、電界効果トランジスタのチャネル層に適用できる層であってもよく、前記絶縁層は、前記電界効果トランジスタのゲート絶縁層に適用できる層であってもよい。前記第1結晶層の77Kにおけるフォトルミネッセンス発光のピーク波長が、1070nmより大きいものであってもよい。

(もっと読む)

半導体基板、絶縁ゲート型電界効果トランジスタおよび半導体基板の製造方法

【課題】絶縁ゲート型P−HEMT構造において、良好なトランジスタ性能を実現する。

【解決手段】ベース基板、第1結晶層、第2結晶層および絶縁層をこの順に有し、第1結晶層と第2結晶層との間、または、ベース基板と第1結晶層との間に位置する第3結晶層をさらに有し、第2結晶層が、第1結晶層を構成する結晶に格子整合または擬格子整合し、かつ第1結晶層を構成する結晶よりも禁制帯幅が大きい結晶からなり、第3結晶層が、第1結晶層を構成する結晶に格子整合または擬格子整合し、かつ第1結晶層を構成する結晶よりも禁制帯幅が大きい結晶からなり、第3結晶層は、ドナーまたはアクセプタとなる第1原子を含み、第3結晶層がドナーとなる第1原子を含む場合、第2結晶層が、アクセプタとなる第2原子を含み、第3結晶層がアクセプタとなる第1原子を含む場合、第2結晶層が、ドナーとなる第2原子を含む半導体基板。

(もっと読む)

電界効果トランジスタ

【課題】 本発明は、低消費電力で動作する論理回路に応用できる電界効果トランジスタを提供することを目的とするものである。

【解決手段】 ソース電極とソース電極が接する半導体の伝導帯又は価電子帯との間に障壁を有しており、ソース電極から障壁を通して流れ込む電子又はホールをゲート電圧により調整できる構成を有することを特徴とするnチャンネル又はpチャンネルの電界効果トランジスタ。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】低オン抵抗の電界効果トランジスタを低コストで実現する。

【解決手段】電界効果トランジスタは、第一導電型の半導体基体であるN+型SiC基板2及びN-型ドレイン領域1と、N+型SiC基板2の第一主面側に、P型ウエル領域3とN+型ソース領域5とゲート電極7とを有する。N-型ドレイン領域1中に、N-型ドレイン領域1とはバンドギャップの異なるP+型ポリシリコンで形成され、第一主面から第二主面へ向かって伸びる柱状のヘテロ半導体領域4が、間隔を置いて並んで複数形成されている。ゲート電極7直下にチャネル領域が形成されないときに、N-型ドレイン領域1がヘテロ半導体領域4と接することによりN-型ドレイン領域1の全域が空乏化される。

(もっと読む)

半導体積層体とこれを含むHFETおよびそれらの製造方法

【課題】半導体積層体に含まれるチャネル層下の化合物半導体層を不純物ドーピングでp型化することなく、その半導体積層体を含むHFETのリーク電流の低減や耐電圧の向上などを可能とする。

【解決手段】半導体積層体は、基板(11)上において順次堆積された第1、第2および第3の化合物半導体層(13、14、15)を少なくとも含み、その第1化合物半導体層(13)の少なくとも部分的層(16)は非晶質に改質されており、第2化合物半導体層(14)は第1化合物半導体層(13)に比べて小さなバンドギャップを有して光吸収層として作用し得る。

(もっと読む)

半導体装置

【課題】オフ時のリーク電流を低減し、パワースイッチング素子に適用可能なノーマリーオフ型の半導体装置を提供する。

【解決手段】基板101と、基板101の上に形成されたアンドープGaN層103と、アンドープGaN層103の上に形成されたアンドープAlGaN層104と、アンドープGaN層103又はアンドープAlGaN層104の上に形成されたソース電極107及びドレイン電極108と、アンドープAlGaN層104の上に形成され、ソース電極107とドレイン電極108との間に配置されたp型GaN層105と、p型GaN層105の上に形成されたゲート電極106とを備え、アンドープGaN層103は、チャネルを含む活性領域113と、チャネルを含まない不活性領域112とを有し、p型GaN層105は、ソース電極107を囲むように配置されている。

(もっと読む)

窒化物系半導体装置

【課題】MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させ、かつ、チップサイズの増加を抑制した、窒化物系半導体装置を提供することができる、窒化物系半導体装置を提供することを目的とする。

【解決手段】ショットキー電極30が、ソース電極24とドレイン電極26とが対向する領域の、ソース電極24とドレイン電極26とが対向する方向と略直交する方向にゲート電極28と並んで形成されている。ショットキー電極30は、AlGaN層20とショットキー接合されており、ソース電極24に電気的に接続されている。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

電界効果トランジスタ

【課題】電界効果トランジスタにおけるソースの高キャリア濃度化をプロセス面での負荷を抑えつつ実現する。

【解決手段】ゲート絶縁膜30は、3−5族化合物半導体のチャネル層20の第1面のゲート領域に形成される。ソースコンタクト層34およびドレインコンタクト層38は、チャネル層20の第1面にゲート領域を挟むように位置するドレイン領域およびソース領域それぞれに形成される。裏面絶縁膜50は、チャネル層20の第1面と反対側の第2面側に形成される。ソース下面電極52は、裏面絶縁膜50のチャネル層20と反対の面側に、ソースコンタクト層34と対向する領域に形成される。

(もっと読む)

AlGaN酸化膜を有する半導体装置、及び、その製造方法

【課題】 AlGaN層上に容易に絶縁膜を形成することができる技術を提供する。

【解決手段】 AlGaN層と、AlGaN層の表面に形成されたAlGaN酸化膜とを備えている半導体装置の製造方法であって、アルカリ溶液48中にAlGaN層を有する基板40と陰極44とを浸した状態で、AlGaN層と陰極44との間にAlGaN層がプラスとなる電圧を印加するとともに、AlGaN層に紫外線を照射する酸化ステップを有している。

(もっと読む)

半導体基板および半導体装置

【課題】高いしきい値電圧と低いリーク電流のノーマリーオフの半導体素子を提供する。

【解決手段】基板2の上に少なくともAlを含むIII族窒化物からなる下地層(バッファー層)3を設けた上で、III族窒化物、好ましくはGaNからなる第1の半導体層(チャネル層)4と、少なくともAlを含むIII族窒化物、好ましくはAlxGa1−xNであってx≧0.2である第2の半導体層(電子供給層)6が積層されてなる半導体層群からなるHEMT構造の半導体素子の上に、Al2O3−Si3N4の混晶からなる絶縁膜7を形成し、その上にゲート電極9を形成した。

(もっと読む)

窒化物系半導体装置

【課題】導通抵抗が低く、かつ高い電圧を維持すると共に、ゲート絶縁膜の破壊を抑制したゲート信頼性の高い窒化物系半導体装置を提供することを目的とする。

【解決手段】AlGaN層20上に形成されたショットキー電極22が、正孔をソース電極30に流す(輸送する)ため、ゲート絶縁膜24、特にトレンチ部23のコーナー部に集中して電圧が印加されることがなくなる。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】ゲートリセスの深さの制御を安定的に行なえるようにして、ノーマリオフ動作のデバイスを安定的に作製できるようにする。

【解決手段】半導体装置を、基板1の上方に設けられたGaN電子走行層2と、GaN電子走行層2上に設けられた第1AlGaN電子供給層3と、第1AlGaN電子供給層3上に設けられたAlN電子供給層4と、AlN電子供給層4上に設けられた第2AlGaN電子供給層5と、第2AlGaN電子供給層5及びAlN電子供給層4に設けられたゲートリセス9と、ゲートリセス9に設けられたゲート電極12とを備えるものとする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】比較的簡素な構成で、シート抵抗及びゲートリーク電流の増加、出力の低下等の不都合を生ぜしめることなく、所期のノーマリ・オフを実現する。

【解決手段】化合物半導体層が電子走行層2、中間層3、電子供給層4、及びキャップ層5を有して構成され、キャップ層5上にゲート絶縁膜9を介してゲート電極15が形成されており、ゲート絶縁膜9は、キャップ層5の表面に酸素プラズマが照射されて形成されたGa2O3を含む極性反転層6と、極性反転層6の存在でO極性のZnOとなった逆極性層7とが積層されてなる。

(もっと読む)

半導体基板および半導体装置

【課題】高いしきい値電圧と低いリーク電流のノーマリーオフの半導体素子を提供する。

【解決手段】基板2の上に少なくともAlを含むIII族窒化物からなる下地層(バッファー層)3を設けた上で、III族窒化物、好ましくはGaNからなる第1の半導体層(チャネル層)4と、少なくともAlを含むIII族窒化物、好ましくはAlxGa1−xNであってx≧0.2である第2の半導体層(電子供給層)6が積層されてなる半導体層群からなるHEMT構造の半導体素子の上に、Al2O3−SiO2の混晶からなる絶縁膜7を形成し、その上にゲート電極9を形成した。

(もっと読む)

半導体装置及びこれを用いた電気回路、電気回路の制御方法

【課題】消費電力を増大させずにオンチップでHEMTの動作状況をモニターする。

【解決手段】

この半導体装置10においては、第1の半導体層である電子走行層11上に、第2の半導体層である電子供給層12が形成されている。これらの界面(ヘテロ接合界面)における電子走行層側に、2次元電子ガス(2DEG)層13が形成される。この半導体装置10において、電子は、電子供給層12の表面に形成された第1の主電極であるソース電極14と、同様にこの表面に形成された第2の主電極であるドレイン電極15との間を、この2DEG層13を通って流れる。ゲート電極16とソース電極14との間の電子供給層12上に電位検出電極17が設置される。この電位検出電極17には、動作時にこの電位検出電極17に流れる電流がドレイン電流と比べて無視できる程度となるような、充分に高い抵抗値をもつ抵抗18が接続される。

(もっと読む)

窒化物半導体装置

【課題】歩留まり良く形成することができ、高い信頼性を保つことができる、高周波特性が優れた窒化物半導体装置を提供する。

【解決手段】ソース電極5とドレイン電極6との間の電子供給層4上に、電子供給層とショットキー接触する浮遊電極8を配置し、この浮遊電極上に絶縁膜9を介してゲート電極7を配置する。特に絶縁膜を強誘電体材料とすると好ましい。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】電流コラプスを抑制し、高出力動作可能な窒化物半導体装置を提供する。

【解決手段】ショットキ接触する電極(ゲート電極16)16とオーミック接触する電極(ソース電極17a、ドレイン電極17b)との間のIII−V族窒化物半導体層14表面に、ECRスパッタリング法により珪素膜15を形成する。ショットキ接触する電極16とIII−V族窒化物半導体層14との間に、珪素膜15を形成してもよい。

(もっと読む)

201 - 220 / 744

[ Back to top ]