Fターム[5F102GR07]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 半導体基体内に付加領域を設けたもの (876) | 不純物領域 (317)

Fターム[5F102GR07]の下位に属するFターム

ウェル領域 (42)

Fターム[5F102GR07]に分類される特許

41 - 60 / 275

p型のIII族窒化物半導体層を含む半導体装置

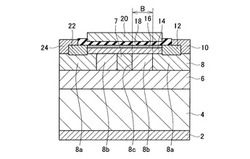

【課題】 p型のIII族窒化物半導体層に貫通孔が形成されており、その貫通孔をn型のIII族窒化物半導体が充填している場合、貫通孔を充填しているn型のIII族窒化物半導体の不純物濃度が濃くなり、p型のIII族窒化物半導体とn型のIII族窒化物半導体の接合界面を電流が流れやすくなり、耐圧が低くなりやすい。

【解決手段】 p型のIII族窒化物半導体層8に不純物濃度の分布を設ける。貫通孔8cに臨んでいる範囲8bでは不純物濃度を薄くし、貫通孔8cから離反している範囲8aでは不純物濃度を濃くする。半導体装置のオフ時に、空乏層が不純物濃度の薄い範囲8bに広く拡がり、必要な耐圧を確保できる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】バッファ層の結晶成長時に高抵抗化の不純物をドーピングすることなく上層の化合物半導体の結晶品質を保持するも、バッファ層を高抵抗化してオフリーク電流を確実に抑制し、信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2の裏面から、化合物半導体積層構造2の少なくともバッファ層2aに不純物、例えばFe,C,B,Ti,Crのうちから選ばれた少なくとも1種類を導入し、バッファ層2aの抵抗値を高くする。

(もっと読む)

へテロ接合電界効果型トランジスタ及びその製造方法

【課題】耐圧特性の低下やゲートリーク電流の増加を生じることなく、低抵抗で高速動作可能なヘテロ接合電界効果型トランジスタおよびその製造方法を提供する。

【解決手段】ヘテロ接合FETの製造方法に関し、(a)チャネル層3及びチャネル層3上に形成されたバリア層4を窒化物半導体層として準備する工程と、(b)窒化物半導体層上に不純物拡散源としてZnO膜9を形成する工程と、(c)ZnO膜9上のドレイン電極6及びソース電極5を形成すべき領域以外に酸化膜10を形成する工程と、(d)窒化物半導体層に対して熱処理を行い、酸化膜10が形成されていない領域の下部のチャネル層3及びバリア層4に選択的に、ZnO膜9からZn及びOを拡散させる工程とを備える。

(もっと読む)

トランジスタ装置及びトランジスタ装置製造方法

【課題】トラップの影響を低減し、過渡応答を改善するトランジスタ装置及びトランジスタ装置製造方法を提供する。

【解決手段】ソース電極5とゲート電極6との間のGaNチャネル2における一部に形成された、不純物濃度が高い領域である高不純物領域13を含み、高不純物領域13は、ゲート電極6とドレイン電極7との間より不純物濃度が高い。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】簡便な方法で形成することが可能な高抵抗のバッファ層を備えた窒化物半導体装置およびその製造方法を提供する。

【解決手段】基板上に、原料ガスとして有機金属ガリウムを供給しながら、エピタキシャル成長温度とn型不純物のドーピングガスの供給量を制御することにより、有機金属ガリウムに起因する炭素がドーピングされて所望の抵抗率となる窒化ガリウム層をバッファ層としてエピタキシャル成長する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】低コストでしきい値電圧のバラツキの少ないノーマリーオフ化されたHEMTを提供する。

【解決手段】基板10の上方に半導体層21〜24を形成する工程と、半導体層23〜24にフッ素成分を含むガスを用いたドライエッチングによりリセス51となる開口部を形成する工程と、半導体層を加熱することによりリセス51の側面及び底面に付着しているフッ素を半導体層22〜24に拡散させフッ素を含む領域を形成する工程と、リセス51の内面及び半導体層22〜24上に絶縁膜30を形成する工程と、リセス51が形成されている領域に絶縁膜30を介し電極41を形成する工程と、を有する。

(もっと読む)

半導体装置、電源装置、増幅器及び半導体装置の製造方法

【課題】半導体装置に形成される絶縁膜の付着力を高め歩留りを向上させる。

【解決手段】基板10の上方に形成された半導体層20〜23と、前記半導体層20〜23上に形成された絶縁膜31,32と、前記絶縁膜上31,32に形成された電極41と、を有し、前記絶縁膜31,32は、前記電極41の側における膜応力よりも、前記半導体層20〜23の側における膜応力が低いことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

ノーマリオフ型パワーJFETの製造方法

【課題】SiC系JFETにおいて、トレンチゲート領域間を高精度に制御するため、ソース領域内にゲート領域を形成する必要がある。これにより増加するソース領域、ゲート領域間高濃度PN接合による接合電流を削減できる半導体装置を提供する。

【解決手段】ノーマリオフ型パワーJFETの製造方法であって、N型SiC1sの表面に、Nエピタキシャル下層1ea、中層1eb、上層1ec等複数層を形成し、表面には複数のソース層9、及びPゲート領域4が設けられる。ゲート領域はアクティブ領域3の外端部に接するように、下層、中層、上層のPエッジターミネーション領域7a、7b、7cが設けられる。裏側種面には、高濃度ドレイン層8が形成される。

(もっと読む)

半導体素子用のエピタキシャル基板、および半導体素子用エピタキシャル基板の製造方法

【課題】高耐電圧性を有するとともにp型不純物の拡散による結晶品質の劣化が好適に抑制された、半導体素子用のエピタキシャル基板を提供する。

【解決手段】(111)方位の単結晶シリコンである下地基板1の上に、前記下地基板の基板面に対し(0001)結晶面が略平行となるようにIII族窒化物層群を形成してなる半導体素子用のエピタキシャル基板10が、組成の相異なる第1単位層31と第2単位層32とを繰り返し交互に積層してなる組成変調層3と、組成変調層の上に形成され、Alを含むIII族窒化物からなる中間層5と、を含む単位構造体を複数積層してなるバッファ層8と、バッファ層の直上に形成されたチャネル層9aと、チャネル層の上に形成されたバリア層9bと、を備え、バッファ層に含まれる複数の前記中間層のうちの少なくとも1つにp型不純物が意図的に導入されてなり、隣接層に第1の層から拡散したp型不純物が存在する、ようにする。

(もっと読む)

p型のIII族窒化物半導体層を含む半導体装置とその製造方法

【課題】p型のIII族窒化物半導体層を含む積層構造を利用して複数個の半導体装置を製造し、エッチング等して個々の半導体装置に分割すると、個々の半導体装置の側面に露出するp型のIII族窒化物半導体層の表面に沿ってリ−ク電流が流れてしまう。

【解決手段】p型のIII族窒化物半導体層8を含む積層構造の表面または裏面からp型のIII族窒化物半導体層8に達しない深さまでエッチングまたはダイシングし、残った厚みをへき開して個々の半導体装置に分割する。半導体装置の側面に露出するp型のIII族窒化物半導体層8の表面はへき開面となり、結晶欠陥が少なく、側面に沿ってリ−ク電流が流れることを防止する。

(もっと読む)

半導体素子

【課題】低オン抵抗および高信頼性を有する半導体素子を提供する。

【解決手段】半導体素子1Aは、第1導電形層11が表面に選択的に設けられた半絶縁性基板10と、前記半絶縁性基板および前記第1導電形層の上に設けられたノンドープAlXGa1−XN(0≦X<1)を含む第1半導体層15と、前記第1半導体層上に設けられたノンドープもしくは第2導電形のAlYGa1−YN(0<Y≦1、X<Y)を含む第2半導体層16とを備える。半導体素子は、前記第2導電形層11に接続された第1主電極20と、前記第2半導体層16に接続された第2主電極と21、前記第1主電極と、前記第2主電極と、のあいだの前記第2半導体層の上に設けられた制御電極30とを備える。前記第1導電形層11は、前記制御電極30の下に設けられている。

(もっと読む)

半導体装置

【課題】 オン抵抗の増大を抑制しつつ、耐圧の低下を抑制する技術を提供する。

【解決手段】 ノーマリオフ型の半導体装置100は、ヘテロ接合を構成する半導体層16と、第1リセス部8と、第1リセス部8よりも浅い第2リセス部4と、ゲート部5を備えている。半導体層16は、第1半導体層12と、第1半導体層12上に設けられているとともに第1半導体層12よりもバンドギャップが広い第2半導体層14を有している。第2リセス部4は、第2半導体層14を貫通していない。第2リセス部4の下方に位置する第2チャネル部C2は、第1リセス部8の下方に位置する第1チャネル部C1よりも電流経路20の上流側に配置されている上流側第2チャネル部C2uを有する。

(もっと読む)

半導体装置、及びその製造方法

【課題】低消費電力・低電圧動作で、高利得・低歪特性を有し、かつ低コスト化が実現可能な半導体装置とその製造方法を提供する。

【解決手段】本発明に係る半導体装置のpチャネルFET2は、ソース/ドレインを形成する高濃度p型半導体層33と、その直下層に配設された低濃度p型半導体層32と、高濃度p型半導体層33上に形成された第1電極層41と、低濃度p型半導体層32の下方に形成され、ゲートとなる高濃度n型半導体層22と、その上に形成された第2電極層42とを備える。nチャネルFET3は、ソース/ドレインを形成する高濃度n型半導体層22と、ゲートを形成する高濃度p型半導体層33と、その下方に形成された低濃度n型半導体層21と、第1電極層42と、第2電極層42とを備える。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制する。

【解決手段】トレンチ6の先端部に形成されたn-型チャネル層7がトレンチ6の長辺に位置する部分よりも膜厚が厚くなるため、そのトレンチ6の先端部においてJFET構造が構成されないようにする。例えば、トレンチ6の先端部をp+型領域20にて埋め尽くすようにする。これにより、トレンチ6の先端部のJFET構造の閾値がトレンチ6の長辺に位置する部分のJFET構造の閾値からずれることによる影響を受けることがない。したがって、ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制できる構造のSiC半導体装置とすることが可能となる。

(もっと読む)

電界効果型トランジスタ

【課題】耐圧向上を図った電界効果型トランジスタを提供する。

【解決手段】電界効果型トランジスタは、基板101上に、核形成層として機能する第一の窒化物半導体層102と、第一の窒化物半導体層102よりも電子親和力の大きい第二の窒化物半導体層103と、第二の窒化物半導体層103よりも電子親和力の小さい第三の窒化物半導体層104とを順に積層して形成されている。第三の窒化物半導体層104上には中間層106を介して形成されたソース電極107、ドレイン電極108、ゲート電極109が設けられている。第一の窒化物半導体層102には、ホウ素が不純物としてドーピングされている。

(もっと読む)

半導体装置

【課題】導体ベースプレート上に実装するSiCやダイヤモンドを基板とする高周波半導体チップの割れを防止する。

【解決手段】導体ベースプレートと、導体ベースプレート上に配置された高周波半導体チップとを備え、高周波半導体チップは、四隅が面取りされている半導体装置。

(もっと読む)

パッケージ

【課題】導体ベースプレートと金属外壁との熱膨張係数が異なることに伴う、銀ロウ付けする際の導体ベースプレートの反りを抑制したパッケージを提供する。

【解決手段】導体ベースプレートと、導体ベースプレート上に配置された半導体装置と、半導体装置を内在し、導体ベースプレート上に配置され、導体ベースプレートと接する面に複数の開放部を有する金属壁と、開放部を充填するブロックとを備えるパッケージ。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度を得ながら、かつ、縦方向耐圧およびゲート電極端における耐圧の両方の耐圧性能を確実に得ることができる、半導体装置およびその製造方法を提供する。

【解決手段】 n型ドリフト層および該n型ドリフト層上に位置するp型層を含むGaN系積層体に、開口部が設けられ、開口部を覆うように位置する、チャネルを含む再成長層と、再成長層に沿って該再成長層上に位置するゲート電極とを備え、開口部はn型ドリフト層に届いており、ゲート電極の端は、平面的に見てp型層から外れた部分がないように位置していることを特徴とする。

(もっと読む)

ブール成長された炭化ケイ素ドリフト層を使用してパワー半導体デバイスを形成する方法、およびそれによって形成されるパワー半導体デバイス

【課題】炭化ケイ素の好ましい電気特性にもかかわらず、その中においてより厚い電圧サポート領域を有する炭化ケイ素パワーデバイスの必要性が引き続き存在している。

【解決手段】高電圧炭化ケイ素パワーデバイスを形成する方法は、法外に高いコストのエピタキシャル成長された炭化ケイ素層の代わりに、高純度炭化ケイ素ウエハ材料から得られる高純度炭化ケイ素ドリフト層を利用している。本方法は、約100μmより厚い厚みを有するドリフト層を使用して10kVを超えるブロッキング電圧をサポートすることができる少数キャリアパワーデバイスと多数キャリアパワーデバイスの両方を形成することを含んでいる。これらのドリフト層は、その中に約2×1015cm−3未満である正味n型ドーパント濃度を有するブール成長炭化ケイ素ドリフト層として形成される。このn型ドーパント濃度は、中性子変換ドーピング(NTD)技法を使用して実現することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】GaN系の材料により形成されるHEMT(高電子移動度トランジスタ)をノーマリーオフ化させる。

【解決手段】基板11上に形成された第1の半導体層12と、前記第1の半導体層上に形成された第2の半導体層13と、所定の領域の前記第2の半導体層の一部または全部を除去することにより形成されているゲートリセス22と、前記ゲートリセス及び第2の半導体層上に形成されている絶縁膜31と、前記ゲートリセス上に絶縁膜を介して形成されているゲート電極32と、前記第1の半導体層または前記第2の半導体層上に形成されているソース電極33及びドレイン電極34と、を有し、前記ゲートリセスが形成されている領域における前記第2の半導体層、または、前記第2の半導体層及び前記第1の半導体層にはフッ素が含まれているフッ素を含む領域24を有する。

(もっと読む)

41 - 60 / 275

[ Back to top ]