Fターム[5F102GR07]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 半導体基体内に付加領域を設けたもの (876) | 不純物領域 (317)

Fターム[5F102GR07]の下位に属するFターム

ウェル領域 (42)

Fターム[5F102GR07]に分類される特許

101 - 120 / 275

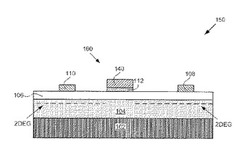

アルミニウムドープゲートを備えるプログラマブルIII−窒化物トランジスタ

【課題】アルミニウムドープゲートを有するプログラマブルIII−窒化物トランジスタを提供する。

【解決手段】第1のIII−窒化物材料104と第2のIII−窒化物材料106との界面に形成される2次元電子ガスを有する導電チャネルを含むIII−窒化物ヘテロ接合デバイスにおいて、ゲート接点140の下に形成されるゲート絶縁層112が導電チャネルの上方に配置され、接点絶縁層112は界面における2次元電子ガスの形成を変更する。接点絶縁層112はAlSiN又はアルミニウムがドープされたSiNとすることができる。接点絶縁層112はIII−窒化物ヘテロ接合デバイス160の閾値電圧をプログラミングしてデバイスをエンハンストモードデバイスにする。

(もっと読む)

金属及びシリコンの交互層を含むコンタクト構造体並びに関連デバイスの形成方法

半導体デバイスを形成する方法であって、この方法は、半導体層を準備するステップと、半導体層上に第1の金属の第1の層を準備するステップとを含む。第1の金属の第1の層上に第2の層を準備することができる。第2の層は、シリコン層及び第2の金属の層を含むことができ、第1の金属及び第2の金属は異なり得る。第1の金属はチタンとすることができ、第2の金属はニッケルとすることができる。関連するデバイス、構造体、及び他の方法もまた説明される。 (もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減と、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】凹部4c内に形成されたi型(イントリンシック半導体)側壁層5を介してp+型ゲート領域6を形成する。このような構成とすれば、n+型層4とp+型ゲート領域6との間にさらにp+型ゲート領域6よりも低濃度のp-型層が必要とされない。このため、n-型チャネル層3に直接接触している高濃度のp+型ゲート領域6によって、n-型チャネル層3内に伸びる空乏層幅を制御できる。したがって、n+型層4とp+型ゲート領域6との間にさらにp-型層が備えられる場合と比較して、ゲート印加電圧が高電圧になることを抑制できる。また、p+型ゲート領域6の側面がi型側壁層5によってn+型層4と分離されるため、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスを低減できる。

(もっと読む)

高電子移動度トランジスタ

【課題】 HEMTにおいて、2次元電子ガス層の電気抵抗の増加が抑制された正孔排出用電極を提供すること。

【解決手段】 HEMT10は、ゲート電極34とドレイン電極32の間のヘテロ接合層27に接触する正孔選択通過膜43と、その正孔選択通過膜43に接触する正孔排出用電極46を備えている。正孔選択通過膜43は、へテロ接合層27に接触する第1部分領域42と正孔排出用電極46に接触する第2部分領域44を有している。第2部分領域42のp型不純物の濃度は、第1部分領域44のp型不純物濃度よりも濃い。

(もっと読む)

ヘテロ接合電界効果型トランジスタおよびその製造方法

【課題】ゲートリーク電流を抑制する、窒化物半導体からなるリセスゲート構造のヘテロ接合FET及びその製造方法を提供することを目的とする。

【解決手段】本発明のヘテロ接合FETは、窒化物半導体からなるヘテロ接合FETであって、バリア層40とバリア層40の上に形成されたキャップ層50を含む半導体層と、半導体層に下部を埋没するようにして半導体層上に設けられたゲート電極100と、ゲート電極100の両側に離間して半導体層上に夫々設けられたソース電極80及びドレイン電極90とを備える。キャップ層50は、少なくとも表面側で、少なくともゲート電極100のドレイン電極90側の側面に接する領域に、アクセプタ準位を形成する不純物がドーピングされるドーピング領域60を備える。

(もっと読む)

半導体装置およびそれを備えた電子回路

【課題】同一のボンディングパッドに対して異なる金属のボンディングワイヤーを用いて信頼性の高い配線を行う。

【解決手段】窒化物半導体ヘテロ接合型電界効果トランジスタにおけるソース電極8,ドレイン電極9,ソースパッド8'およびドレインパッド9'をTi,Al,MoおよびAuを順次積層して形成し、ソースパッド8'およびドレインパッド9'の一部をエッチングによって開口して、Al露出部を形成している。したがって、ソースパッド8'またはドレインパッド9'におけるAu露出部に対しては、Auボンディングワイヤーを用いたワイヤーボンディングを行う一方、上記Al露出部に対しては、Alボンディングワイヤーを用いたワイヤーボンディングを行うことによって、優れた密着性とエレクトロマイグレーション耐性を得ることができる。

(もっと読む)

窒化物半導体装置

【課題】高電圧印加時にフィールドプレート構造端に集中する電界強度を緩和し、高耐圧で信頼性の高い窒化物半導体装置を提供する。

【解決手段】フィールドプレート構造を備えた窒化物半導体装置において、ゲート電極18に、オフ制御の制御電圧を印加するとき、フィールドプレート構造の傾斜面部直下の窒化物半導体層中13にはキャリアが存在しないようにする。

(もっと読む)

金属キャリアを有する半導体デバイスおよび製造方法

【課題】 金属キャリアを有する半導体デバイス及び製造方法を提供する。

【解決手段】 金属キャリア基板を含む半導体デバイス。キャリア基板の上には、Alx1Gay1Inz1N(x1+y1+z1=1、x1≧0、y1≧0、z1≧0)の第1の半導体層が形成される。第1の半導体層の上にはAlx2Gay2Inz2N(x2+y2+z2=1、x2>x1、y2≧0、z2≧0)の第2の半導体層が配され、第2の半導体層の上にはゲート領域が配置される。半導体デバイスはさらに、ソース領域およびドレイン領域を含み、これらの領域のうちの一方が金属キャリア基板と電気的に接続され、第1の半導体層を介して延在する導電性領域を含む。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】高耐圧および高電流のスイッチング動作が可能で、かつ製造が容易なFETを提供する。

【解決手段】半導体薄体の一の主表面に設けられた、第1導電型のソース領域(1)と、第1導電型のチャネル領域(10)と、チャネル領域を限定する第2導電型の限定領域(5)と、他の主表面に設けられた第1導電型のドレイン領域(3)と、厚さ方向に連続する第1導電型のドリフト領域(4)とを備え、ドリフト領域(4)およびチャネル領域(10)の不純物濃度は、ソース領域(1)、ドレイン領域(3)および限定領域(5)の不純物濃度よりも低く、チャネル領域(10)の不純物濃度はドリフト領域(4)の不純物濃度よりも低い。

(もっと読む)

ヘテロ接合電界効果型トランジスタ及びその製造方法

【課題】ゲートリーク電流を抑制する、窒化物半導体からなるリセスゲート構造のヘテロ接合FET及びその製造方法を提供することを目的とする。

【解決手段】本発明のヘテロ接合電界効果トランジスタは、窒化物半導体からなるヘテロ接合電界効果トランジスタであって、バリア層4とバリア層4の上に形成されたキャップ層5を含む半導体層と、半導体層に下部を埋没するようにして半導体層上に設けられたゲート電極9と、ゲート電極9の側面と半導体層の間に設けられた絶縁膜10と、を備え、ゲート電極9は、下面のみが半導体層と接触することを特徴とする。

(もっと読む)

半導体基板及び半導体発光素子

【課題】 GaN基板上に結晶成長する各半導体層の平坦性が、半導体素子の寸法相当において向上した半導体基板を提供し、更には、この半導体基板を基礎として、特性の高性能化された半導体発光素子、半導体素子を提供する。

【解決手段】基板11と、この基板11上に積層された窒化物系III−V族化合物半導体単結晶層12と、基板11と窒化物系III−V族化合物半導体単結晶層12との間に設けられた、不純物元素を5x1017cm-3以上2x1019cm-3以下含有する層10とを備える。

(もっと読む)

電界効果トランジスタ

【課題】オン抵抗の上昇を抑制しつつ閾値電圧を大きくできる電界効果トランジスタを提供する。

【解決手段】キャリア走行層13である第1窒化物半導体層13と、第1窒化物半導体層13の上に設けられた、第1窒化物半導体層よりもバンドギャップエネルギーの大きい第2窒化物半導体層14と、第2窒化物半導体層14の上に順に設けられた、InGaN16層と、p型窒化物半導体層18と、ゲート電極22とを備える電界効果トランジスタであって、InGaN層16は、ゲート電極22直下の表面に第1の凹部19を有する。これにより、オン抵抗を一定に抑えつつ、閾値電圧を大きくすることができ、ノーマリオフ型のトランジスタが実現できる。

(もっと読む)

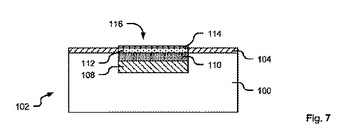

縦型パワートランジスタ装置、半導体チップ、および縦型パワートランジスタ装置の製造方法

縦型トランジスタ装置は、III−V族半導体材料から形成される基板(100)と、少なくとも部分的に基板内に収容される多層スタック(116)とを備える。多層スタックは、基板(100)に隣接して配置される半絶縁層(108)と、第1のIII−V族半導体材料から形成されており、半絶縁層に隣接して配置される第1の層(110)とを備える。多層スタック(116)はまた、第2のIII−V族半導体材料から形成されて、第1の層(110)に隣接する第2の層(112)と、第1の層と第2の層との界面に形成されるヘテロ接合部とを備える。  (もっと読む)

(もっと読む)

接合型電界効果トランジスタおよびその製造方法

本願は、ドレイン(140)と、ゲート(160)と、ソース(130)と、を有し、ドレイン(140)およびソース(130)が、第1の型の半導体領域によって形成される、電界効果トランジスタに関する。一局面では、電界効果トランジスタはまた、ゲート(160)とドレイン(140)の中間のさらなるN+領域(410)等のさらにドープされた領域を含む。さらにドープされた領域は、電界効果トランジスタの中間ドレインとして見なすことができる。いくつかの実装では、さらにドープされた領域は、高濃度にドープすることができる。さらにドープされた領域によって、ドレイン(140)周囲の電界勾配を減少させることができる。  (もっと読む)

(もっと読む)

化合物半導体装置及びその製造方法

【課題】オン抵抗を大幅に低減し、十分な高電圧動作且つ高出力を得ることができる信頼性の高い化合物半導体装置を実現する。

【解決手段】ソース電極12及びドレイン電極13の下方の凹部7,8を充填し、電子供給層4の上方を覆う、Siを含むn−GaN層9が形成されており、n−GaN層9は、ソース電極12の下方及びドレイン電極13下方に含まれるSiの方が、ゲート電極15の近傍に含まれるSiよりも濃度が大きくなるように、Si添加量を漸減させながら成長形成される。

(もっと読む)

電界効果トランジスタ、半導体基板及び電界効果トランジスタの製造方法

【課題】高いチャネル移動度を有する電界効果トランジスタを提供する。

【解決手段】ゲート絶縁層と、前記ゲート絶縁層に接する第1半導体結晶層と、第1半導体結晶層に格子整合または擬格子整合する第2半導体結晶層とを有し、前記ゲート絶縁層、前記第1半導体結晶層および前記第2半導体結晶層が、ゲート絶縁層、第1半導体結晶層、第2半導体結晶層の順に配置されており、前記第1半導体結晶層がInx1Ga1−x1Asy1P1−y1(0<x1≦1、0≦y1≦1)であり、前記第2半導体結晶層がInx2Ga1−x2Asy2P1−y2(0≦x2≦1、0≦y2≦1、y2≠y1)であり、前記第1半導体結晶層の電子親和力Ea1が前記第2半導体結晶層の電子親和力Ea2より小さい電界効果トランジスタを提供する。

(もっと読む)

電力電子素子及びその製造方法並びに電力電子素子を含む集積回路モジュール

【課題】2DEG(2−Dimensional Electron Gas)チャネルを持つ電力電子素子及びその製造方法を提供する。

【解決手段】本発明にかかる電力電子素子は、2DEGチャネルを形成する、順次に形成された下部及び上部物質層と、上部物質層の上面上に接触したゲートを含み、2DEGチャネルのゲート下領域はオフ領域であり、前記オフ領域で2DEGの密度は最小または0である。上部物質層の全体は、連続的で均一な厚さを持つことができる。ゲート下部の上部物質層は、下部及び上部物質層の間の格子定数差を最小化するか、またはなくす不純物を含むことができる。

(もっと読む)

電界効果トランジスタ

【課題】十分に大きな電流密度を得ることができるノーマリオフ型の窒化物半導体からなる電界効果トランジスタ及びその製造方法を提供する。

【解決手段】基板101上にAlNバッファ層102、アンドープGaN層103、アンドープAlGaN層104、p型GaN層105、高濃度p型GaN層106が順に形成され、ゲート電極111が高濃度p型GaN層106とオーミック接合する。アンドープAlGaN層104の上にはソース電極109及びドレイン電極110が設けられる。アンドープAlGaN層104とアンドープGaN層との界面で発生する2次元電子ガスとp型GaN層105とによって生じるpn接合がゲート領域に形成されるのでゲート電圧を大きくすることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波動作や広帯域化が可能な増幅器の実現ができるGaNを使用した、HEMT(高電子移動度トランジスタ)のソース、ドレイン間寄生容量を低減できる半導体装置及びその製造方法を提供する。

【解決手段】電子が走行するGaNバッファ層2と、バッファ層上に形成された、2次元電子ガスを形成するAlGaNバリア層3と、バリア層上のゲート電極8、ソース電極6、ドレイン電極7を有するHEMTにおいて、ソース電極6とドレイン電極7の下部に形成した高濃度不純物領域4と、高濃度不純物領域4の下部に形成され、当該高濃度不純物領域4より不純物濃度が低い低濃度不純物領域5とを備えた。

(もっと読む)

電子デバイス用エピタキシャル基板およびその製造方法

【課題】横方向リーク電流の低減と横方向耐圧特性を両立させ、縦方向耐圧を向上させる電子デバイス用エピタキシャル基板を提供する。

【解決手段】Si基板1上のバッファ3上にIII族窒化物層をエピタキシャル成長させた、チャネル層4aおよび電子供給層4bを有する主積層体4を具え、前記バッファは、Si基板と接する初期成長層5および初期成長層上の超格子多層構造からなる超格子積層体6を有し、初期成長層はAlN材料からなり、前記超格子積層体はBa1Alb1Gac1Ind1N材料からなる第1層6aおよび第1層とはバンドギャップの異なるBa2Alb2Gac2Ind2N材料からなる第2層6bを積層してなり、前記超格子積層体と、前記主積層体を構成するチャネル層のバッファ側の部分は、C濃度が1×1018/cm3以上であり、チャネル層の電子供給層側の部分は、C濃度が4×1016/cm3以下であることを特徴とする。

(もっと読む)

101 - 120 / 275

[ Back to top ]