Fターム[5F102GR07]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 半導体基体内に付加領域を設けたもの (876) | 不純物領域 (317)

Fターム[5F102GR07]の下位に属するFターム

ウェル領域 (42)

Fターム[5F102GR07]に分類される特許

141 - 160 / 275

窒化物半導体装置形成用基板及び窒化物半導体装置

【課題】 バッファ領域の漏れ電流を低減する共に、半導体領域の転位密度を低減した窒化物半導体装置形成用基板を提供し、高周波特性に優れた窒化物半導体装置を提供する。

【解決手段】 多層構造体のバッファ領域の一部にp型不純物をドーピングし、二次元電子ガス層の発生を抑制することで、転位、漏れ電流を低減する。また二次元電子ガス層の発生を抑制することで寄生容量が低減され、高周波特性を大きく改善した窒化物半導体装置を提供することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ノーマリオフ型の接合FETにおいて、耐圧の向上とオン抵抗の低減とを両立することができる技術を提供する。

【解決手段】炭化シリコンを基板材料として使用した接合FETにおいて、ゲート領域GRとチャネル形成領域との間のpn接合近傍に、ゲート領域GRに導入されている不純物とは逆導電型であり、チャネル形成領域に導入されている不純物と同じ導電型の不純物を導入する。これにより、pn接合の不純物プロファイルを急峻にするとともに、チャネル形成領域のうち、ゲート領域GRとpn接合を形成する接合領域の不純物濃度が、チャネル形成領域の中央領域の不純物濃度およびエピタキシャル層EPIの不純物濃度よりも高くする。

(もっと読む)

チャネル領域の下方にデルタドープ層を有するIII−V族デバイス

III−V族材料のデバイスは、チャネル領域の下方にデルタドープ領域を有する。これは、ゲートとチャネル領域との間の距離を短縮することによって、デバイスの性能を向上させ得る。  (もっと読む)

(もっと読む)

ヘテロ接合電界効果トランジスタおよびその製造方法

【課題】ソース電極およびドレイン電極のn+層領域と2DEGチャネルとの接触抵抗を低減したヘテロ接合電界効果トランジスタを提供する。

【解決手段】基板上に設けられた電子走行層と、電子走行層の上に設けられた電子供給層と、ソース電極およびドレイン電極のそれぞれに対応して電子供給層に設けられたトレンチと、を有し、トレンチの底面が電子走行層と電子供給層の界面であるヘテロ接合から所定の距離だけ離れている構成である。

(もっと読む)

化合物半導体基板及び該化合物半導体基板を用いた半導体装置

【課題】寄生容量が低減された化合物半導体基板及び化合物半導体装置を提供する。

【解決手段】Siから構成される基板11と、基板11上に形成され、AlNから構成される第1の半導体層12とGaNから構成され鉄(Fe)がドーピングされた第2の半導体層13とを交互に積層して形成されるバッファ層14(積層構造体)と、バッファ層14上に形成され、GaNから構成される第1の成長層としてのチャネル層15と、チャネル層15上に形成され、AlGaNから構成される第2の成長層としてのバリア層16と、バリア層16上に形成され、所定の開口を有する絶縁膜18と、絶縁膜18の開口を介してバリア層16上に形成されるゲート電極G、ソース電極S及びドレイン電極Dと、を備える。

(もっと読む)

電界効果型トランジスタ

【課題】ドレイン電極からのホールリークが防止された横型のFETを提供することを課題とする。

【解決手段】基板の表面上に形成された第1導電型のチャネル層と、前記チャネル層上に形成されたソース電極、ドレイン電極及びゲート電極とを備え、前記ソース電極及びドレイン電極を前記チャネル層とオーミックコンタクトさせて電界効果型トランジスタを構成し、前記ドレイン電極の下部の前記チャネル層に第1導電型の拡散領域を備え、前記拡散領域が、式(1)Ns≧ε×Vmax/(q×t)(式中、εは前記チャネル層の誘電率[F/m]、Vmaxは前記電界効果型トランジスタの仕様最大電圧[V]、qは電荷量(1.609×10-19)[C]、tは前記基板の表面から前記拡散領域の底面までの距離[m]である)で表されるシート不純物濃度Ns[cm-2]を有していることを特徴とする電界効果型トランジスタにより上記課題を解決する。

(もっと読む)

窒化物半導体素子

【課題】本発明は、低オン抵抗でノーマリーオフ型の窒化物半導体素子を提供する。

【解決手段】本発明の一態様によれば、p型窒化物半導体の第1の半導体層と、第1の半導体層上に設けられたアンドープ窒化物半導体の第2の半導体層と、第2の半導体層上に選択的に設けられたアンドープまたはn型窒化物半導体の第3の半導体層と、第3の半導体層上に設けられた第1の主電極と、第3の半導体層上に設けられた第2の主電極と、第2の半導体層上に設けられた絶縁膜と、絶縁膜上に設けられた制御電極と、を備え、第3の半導体層のバンドギャップは、第2の半導体層のバンドギャップよりも大きく、制御電極は、第1の主電極と第2の主電極との間に位置することを特徴とする窒化物半導体素子が提供される。

(もっと読む)

半導体装置

【課題】優れた特性を有し、IC化に適した起動回路を提供する。

【解決手段】N型エピタキシャル層12に形成され、ドレイン領域121を規定するP型素子分離領域13が形成される。ドレイン領域121内にボディ領域15が形成され、ボディ領域15内にN型ソース領域16が形成される。ドレイン領域121とソース領域16間のチャネル領域上にゲート電極20が配置され、LDMOSが形成される。ドレイン領域121と、ゲートとして機能するP型分離領域13とドレイン領域121に印加される電圧により、P型素子分離領域13が逆バイアスされて空乏層が延びるチャネル領域を介して、JFETのソース引出層23が配置され、JFETが形成される。

(もっと読む)

炭化ケイ素半導体装置および炭化ケイ素半導体装置の製造方法

【課題】チャネルの低い抵抗を維持するとともに、ドリフト層の高い耐圧を維持するSiC半導体装置およびSiC半導体装置の製造方法を提供する。

【解決手段】SiC半導体装置は、SiC基板101、第1半導体層、ベース領域105、第2半導体層、ゲート領域109およびソース領域113を備えている。SiC基板101は、{0001}面に対して30°以上60°以下傾斜した主面101aを有する。第1半導体層は、主面101a上に形成される。ベース領域105は、表面103aの一部に形成される。第2半導体層は、表面103a上に形成される。ゲート領域109は、表面107aの一部に形成され、第2半導体層を挟んでベース領域105と対向する位置に形成される。ソース領域113は、表面107aの一部に形成され、ゲート領域109と隣り合い、かつベース領域105と対向する位置に形成される。

(もっと読む)

接合型電界効果トランジスタの駆動装置および駆動方法

【課題】簡単な構成によって、一時的な過電流による接合型電界効果トランジスタの発熱を抑制するとともに、接合型電界効果トランジスタの過熱状態を検知することができる接合型電界効果トランジスタの駆動装置および駆動方法を提供する。

【解決手段】電流検知部90でモニタする電流が閾値電流を超えた場合、接合型電界効果トランジスタ(JFET)32をターンオンするときのゲート電圧をPN接合のビルトイン電圧より大きくする。これにより、JFET32のオン抵抗を低減させてJFET32の発熱を抑制する。さらに、オン状態のJFET32に流れるゲート電流IGの温度依存性を利用することによって、JFET32の温度の値を簡単に求めることができる。

(もっと読む)

半導体装置

【課題】縦型のGaN系半導体装置の耐圧性能を向上する。

【解決手段】 n−型のGaN層6にp型のGaN層10が積層されており、p型のGaN層10にp型のGaN層10を貫通するアパーチャー28が形成されており、そのアパーチャー28にn型のGaN層26が充填されている。n型のGaN層6の一部に浮遊電流ブロック領域8が形成されている。半導体装置のオフ時に、浮遊電流ブロック領域8からn型のGaN層6に向かって空乏層が広がり、アパーチャー28を充填しているn型のGaN層26の電位が低下し、ゲート絶縁膜20の表面と裏面の間にかかる電位差が減少する。半導体装置の耐圧性能が改善される。浮遊電流ブロック領域8は、p型領域であってもよく、深い準位をもった領域であってもよい。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】応答特性が良く電流コラプスの問題を改善できると同時に、デバイス設計値どおりのゲートリセス部を再現性よく形成しうる窒化物半導体装置を得ること。

【解決手段】基板1上に形成された第1の窒化物半導体からなるチャネル層2と、チャネル層2の上部に形成され、第1の窒化物半導体よりも大きなバンドギャップを有する第2の窒化物半導体からなる第1の電子供給層3aと、第1の電子供給層の上部で離隔した2つの領域として形成され、第1の窒化物半導体と同じか、又はこれよりも大きなバンドギャップを有する第3の窒化物半導体からなる第2の電子供給層3bとを備えている。

第1と第2の電子供給層3a、3bの間には、第2の電子供給層3bよりもドライエッチング速度が小さい材料からなるエッチングストッパ層4が形成されており、この層4の上部で2つの領域に挟まれたゲートリセス部を、ゲート電極5が充填するように形成されている。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】オン抵抗が低く、耐圧性及びチャネル移動度が高い電界効果トランジスタ及び電界効果トランジスタの製造方法を提供すること。

【解決手段】MOS構造を有し、窒化化合物半導体からなる電界効果トランジスタであって、基板上に形成されたi型または所定の導電型を有する半導体層と、エピタキシャル成長によって半導体層とソース電極およびドレイン電極のそれぞれとの間に形成された、所定の導電型とは反対の導電型を有するコンタクト層と、エピタキシャル成長によってドレイン電極側のコンタクト層と半導体層との間にゲート電極と重畳するように形成された、所定の導電型とは反対の導電型を有するとともに該コンタクト層よりもキャリア濃度が低い電界緩和層と、エピタキシャル成長によって半導体層上の電界緩和層に隣接する領域に形成された、i型または所定の導電型を有する媒介層と、媒介層上に形成したゲート絶縁膜と、を備える。

(もっと読む)

トランジスタ

【課題】 ノーマリーオフ型であるとともに、ゲート閾値電圧のばらつきが小さいHEMT型のトランジスタを提供する。

【解決手段】 このトランジスタは、p型領域と、チャネル領域と、バリア領域と、絶縁膜と、ゲート電極を備えている。チャネル領域は、n型またはi型であり、p型領域の表面に接しており、第1チャネル領域と第2チャネル領域を有している。バリア領域は、第1チャネル領域の表面とヘテロ接合している。絶縁膜は、第2チャネル領域の表面、及び、バリア領域の表面に接している。ゲート電極は、絶縁膜を介して第2チャネル領域及びバリア領域に対向している。第1チャネル領域と第2チャネル領域は、電流経路において直列に配置されている。

(もっと読む)

半導体装置およびその製造方法

【課題】耐圧を落とすことなくチャネル抵抗を低減したノーマリオフ型接合FETを提供する。

【解決手段】炭化珪素からなる基板1を用いて形成した接合FETにおいて、チャネル領域(第2エピタキシャル層3)の不純物濃度をドリフト層となる第1エピタキシャル層2の不純物濃度よりも高くする。チャネル領域は、チャネル幅が一定の領域7Aと、その下部でドレイン(基板1)側に行くほどチャネル幅が広くなっていく領域7Bとから形成し、第1エピタキシャル層2とチャネル領域との境界は、ドレイン(基板1)側に行くほどチャネル幅が広くなっていく領域7Bに位置するようにする。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】p型コンタクト抵抗を低減でき、素子のスイッチングスピードを下げないようにすることができる炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】半導体基板6のうち第1〜第3コンタクトホール12〜14から露出した部位に、炭化珪素とAlとNiとが反応してそれぞれ形成された合金層15が設けられている。この合金層15におけるAlとNiとの元素組成比は1:4.6〜1:10.6であり、合金層15の厚さは20nm以上100nm以下になっている。これにより、合金層15と半導体基板6とがオーミック接触となり、低いコンタクト抵抗率を得ることが可能となる。

(もっと読む)

ワイドバンドギャップ半導体装置

【課題】JFETが形成されるセル領域とダイオード形成領域との間の絶縁耐圧を向上でき、耐圧の最適設計が行える構造のSiC半導体装置を提供する。

【解決手段】電界緩和領域R3に備えたp型領域9bとn型領域8bとにより構成されるPN分離部により、セル領域R1とダイオード形成領域R2の間の素子分離を行う。これにより、トレンチ内に酸化膜を配置して素子分離を行う場合と比べて、素子分離用の酸化膜が絶縁破壊されることが無いため、JFETが形成されるセル領域R1とダイオード形成領域R2との間の絶縁耐圧を向上できる。このため、素子分離に酸化膜を用いる場合と比べて耐圧の最適設計を行うことが可能となる。

(もっと読む)

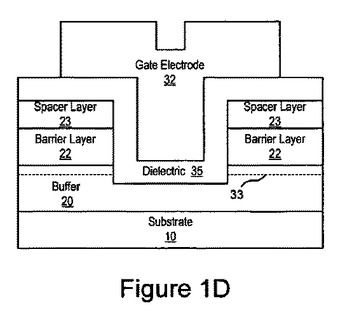

常時オフ半導体デバイスおよびその作製方法

常時オフ半導体デバイスが提供される。III族窒化物バッファ層が提供される。III族窒化物バリア層がIII族窒化物バッファ層上に設けられる。非伝導性スペーサ層がIII族窒化物バリア層上に設けられる。III族窒化物バリア層およびスペーサ層がエッチングされてトレンチを形成する。トレンチはバリア層を貫いて延びてバッファ層の一部を露出させる。誘電体層がスペーサ層上およびトレンチ内に形成され、ゲート電極が誘電体層上に形成される。半導体デバイスの形成に関連する方法も提供される。  (もっと読む)

(もっと読む)

半導体装置

【課題】電極パッド間に形成された抵抗の焼損を抑制するとともに、FETチップの直流動作測定を容易に行うことができる半導体装置を提供すること。

【解決手段】GaAs基板11上に形成された複数のドレイン電極15、及び複数のソース電極14と、これらのドレイン電極15とソース電極14との間にそれぞれ形成された複数のゲート電極13と、これらのゲート電極13に接続された複数のゲートバスライン18と、これらのゲートバスライン18にそれぞれ接続された複数のゲートパッド20と、これらのゲートパッド20と複数のゲートバスライン18との間に形成され、複数のソース電極14を接続するソースパッド16と、このソースパッド16に対向する位置に形成され、複数のドレイン電極15を接続するドレインパッド17と具備するFETチップにおいて、複数のゲートバスライン18及び複数のゲートパッド20は、それぞれGaAs基板11に埋め込み形成された高抵抗層22で接続されている。

(もっと読む)

ヘテロ接合電界効果トランジスタおよびヘテロ接合電界効果トランジスタの製造方法

【課題】リセスゲート部における二次元電子ガス濃度を制御でき、しきい値電圧のバラつきが小さいヘテロ接合電界効果トランジスタおよびその製造方法を提供する。

【解決手段】基板上に、AlxGa1-xN(0≦x<1)からなるチャネル層3と、前記チャネル層3上に設けられ且つリセス領域を有する障壁層10と、前記リセス領域に設けられたゲート電極9と、前記障壁層10上において前記リセス領域を挟んで設けられたソース電極7およびドレイン電極8とを備え、前記障壁層10は、前記チャネル層3側から順にAls1Ga1-s1N(0<s1≦1)からなる第1障壁層4およびAls2Ga1-s2N(0<s2<1)からなる第2障壁層5を有し、第1障壁層4のAl組成s1は、第2障壁層5のAl組成s2および前記チャネル層3のAl組成xの何れよりも大きく、前記リセス領域は、第2障壁層5を貫通して第1障壁層4に到達していることを特徴とする。

(もっと読む)

141 - 160 / 275

[ Back to top ]