Fターム[5F102GR07]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 半導体基体内に付加領域を設けたもの (876) | 不純物領域 (317)

Fターム[5F102GR07]の下位に属するFターム

ウェル領域 (42)

Fターム[5F102GR07]に分類される特許

61 - 80 / 275

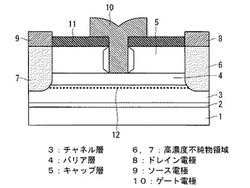

へテロ接合電界効果型トランジスタ及びその製造方法

【課題】本発明は、電流コラプスを抑制し、且つゲートリーク電流を低減するヘテロ接合電界効果型トランジスタとその製造方法の提供を目的とする。

【解決手段】本発明のヘテロ接合電界効果型トランジスタは、バリア層4及びバリア層4上に形成されたキャップ層5を含む窒化物半導体層と、前記窒化物半導体層に下部を埋没するようにして窒化物半導体層上に設けられたゲート電極10と、ゲート電極10の両側に離間して夫々設けられたドレイン電極8及びソース電極9とを備える。ゲート電極10のドレイン電極8側端面とソース電極9側端面のうち少なくともドレイン電極8側端面は、キャップ層5と少なくとも部分的に乖離しており、当該乖離部分が空隙である。

(もっと読む)

III族窒化物半導体装置

【課題】p型III族窒化物半導体62の上面からn型III族窒化物半導体64に到達する溝が形成されている場合、p型III族窒化物半導体の側面62aが露出する。p型III族窒化物半導体の露出面62aはn型化しやすく、露出面に沿ってリーク電流が流れやすい。

【解決手段】p型III族窒化物半導体62中に存在する正孔を露出面62aに誘導する正孔誘導手段を設ける。例えば、露出面62aを被覆する絶縁膜66に負電荷蓄積領域68を設ける。負電荷蓄積領域68が、p型III族窒化物半導体中に存在する正孔を露出面62aに誘導し、露出面がn型化して露出面に沿ってリーク電流が流れることを防止する。

(もっと読む)

半導体発光素子

【課題】GaN基板上に結晶成長する各半導体層の平坦性向上した半導体基板を実現し、この半導体基板を基礎として、特性の高性能化された半導体発光素子を提供する。

【解決手段】p型電極32と、n型電極31と、p型電極32に接続され、複数のp型窒化物系III−V族化合物半導体からなるp型積層構造(16〜20)と、n型電極31に接続され、複数のn型窒化物系III−V族化合物半導体であるn型積層構造(11〜14)と、p型積層構造(16〜20)とn型積層構造(11〜14)との間に形成された窒化物系III−V族化合物半導体からなる活性層15とを備え、n型積層構造(11〜14)がSiを5x1017cm-3以上2x1019cm-3以下の濃度で含有し、厚さが0.3nm以上200nm以下のドープ層10と、ドープ層10よりも活性層15側に設けられた超格子層13とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタをより高速に動作させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の一態様には、基板1と、基板1の上方に形成された電子走行層3及び電子供給層4を備えたトランジスタと、基板1の上方に形成され、トランジスタのゲート11gに接続された窒化物半導体層7及び8と、窒化物半導体層7及び8を移動する電荷を制御する制御手段12、13、11s、及び16と、が設けられている。

(もっと読む)

窒化物半導体装置

【課題】窒化物半導体装置において、高温且つ高電圧下のスイッチング時においても電流コラプスによるオン抵抗の増大が生じないようにする。

【解決手段】基板1上には、バッファ層2、GaNからなるチャネル層3及びアンドープAlGaNからなるバリア層4が順次形成されている。チャネル層3は、該チャネル層3の下部にp型不純物層3aを有し、その上にアンドープ層3bを有している。バリア層4及びチャネル層3の端部が除去されており、露出したバリア層4及びチャネル層3の側面と接するように、それぞれソース電極5及びドレイン電極6が設けられている。バリア層4上におけるソース電極5とドレイン電極6との間の領域にはゲート電極7が設けられている。

(もっと読む)

化合物半導体装置、および化合物半導体装置の製造方法

【課題】GaN層と絶縁層との間の界面準位を低減し、移動度を向上させて優れた電気特性を実現する化合物半導体装置、その製造方法を提供する。

【解決手段】基板11に順次、下地層12、超格子バッファー層13、GaN層14、被覆層15が積層形成されている。被覆層15は、III族元素の窒化物(例えば、AlGaN)とランタノイドの窒化物(例えば、GdN)との混晶としてのAl0.3Ga0.6Gd0.1Nであり、厚さは20nmである。ソース領域17とドレイン領域18の間に位置する絶縁層16は、GaN層14を被覆する被覆層15を酸化して形成された酸窒化物である。

(もっと読む)

半導体素子および半導体素子の作製方法

【課題】ノーマリーオフ動作型の半導体素子を複雑な工程を経ることなく作製する方法を提供する。

【解決手段】半導体素子の作製方法が、下地基板の上に、少なくともGaを含む、Inx1Aly1Gaz1N(x1+y1+z1=1)なる組成の第1のIII族窒化物からなるチャネル層を形成する工程と、チャネル層の上に、少なくともAlを含む、Inx2Aly2Gaz2N(x2+y2+z2=1)なる組成の第2のIII族窒化物からなる障壁層を形成する工程と、障壁層の表面の、ソース電極およびドレイン電極の形成予定個所に対し、ソース電極およびドレイン電極を形成する工程と、障壁層の表面の、ゲート電極の形成予定個所に対し、アルゴンプラズマ処理または酸素プラズマ処理を施す工程と、プラズマ処理工程を経たゲート電極の形成予定個所にゲート電極を形成する工程と、を備えるようにする。

(もっと読む)

半導体装置

【課題】オフ時のリーク電流を低減し、パワースイッチング素子に適用可能なノーマリーオフ型の半導体装置を提供する。

【解決手段】基板101と、基板101の上に形成されたアンドープGaN層103と、アンドープGaN層103の上に形成されたアンドープAlGaN層104と、アンドープGaN層103又はアンドープAlGaN層104の上に形成されたソース電極107及びドレイン電極108と、アンドープAlGaN層104の上に形成され、ソース電極107とドレイン電極108との間に配置されたp型GaN層105と、p型GaN層105の上に形成されたゲート電極106とを備え、アンドープGaN層103は、チャネルを含む活性領域113と、チャネルを含まない不活性領域112とを有し、p型GaN層105は、ソース電極107を囲むように配置されている。

(もっと読む)

半導体素子

【課題】 GaN基板上に結晶成長する各半導体層の平坦性向上した半導体基板を実現し、この半導体基板を基礎として、特性の高性能化された半導体素子を提供する。

【解決手段】n型基板11と、n型基板11上に積層された窒化物系III−V族化合物半導体単結晶からなるn型ドリフト層24と、n型ドリフト層24上に設けられた窒化物系III−V族化合物からなるp型ベース層25と、p型ベース層25上に設けられた窒化物系III−V族化合物からなるn型エミッタ層26と、n型基板11とn型ドリフト層24との間に設けられた、Siを5x1017cm-3以上2x1019cm-3以下含有する層とを備える。

(もっと読む)

半導体装置

【課題】ゲートパッド電極と裏面金属電極間のリーク電流を抑制し、ボンディング強度を向上させ、高性能化・高信頼化を図る。

【解決手段】基板10の第1表面上に配置され、それぞれ複数のフィンガーを有するゲート電極24・ソース電極20およびドレイン電極22およびオーム性電極層18と、ゲート電極・ソース電極およびドレイン電極ごとに複数のフィンガーをそれぞれ束ねて形成したゲート端子電極GE1〜4・ソース端子電極SE1〜4およびドレイン端子電極DEと、オーム性電極層上に配置され、ゲート端子電極と接続するゲートパッド電極30と、オーム性電極層と基板との界面に形成された反応層を覆うように基板内に形成された第1導電型半導体層16と、第1導電型半導体層16を覆うように、基板内に形成され、第1導電型と反対導電型の第2導電型半導体層とを備える半導体装置1。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】容量増加による高周波特性の劣化及び裏面電極に起因する絶縁破壊を抑止し、チップ面積を増加させることなく、インパクトイオン化により生成したホールを容易且つ確実に引き抜いて排出することを可能として、高耐圧性及び高信頼性を実現する化合物半導体装置及びその製造方法を提供する。

【解決手段】絶縁性又は半絶縁性の基板1の表面に電子走行層3、電子供給層4が形成され、電子供給層4内には局所的なp型領域7が形成されており、基板1の裏面にp型領域7の一部を露出させる開口1aが形成され、開口1aを導電材料で埋め込みp型領域7とオーミック接続された裏面電極8を備え、AlGaN/GaN・HEMTが構成される。

(もっと読む)

増幅回路装置

【課題】意図しない低周波信号の入力を防止することにより、規格値を超過するドレイン電流を発生することを回避できる接合形電界効果トランジスタを用いた増幅回路装置を提供する。

【解決手段】J−FET1の封止部材内で、ゲートと直列に容量を付加し、当該容量とJ−FET1のゲート−ソース間に接続される抵抗2とによってハイパスフィルタ5を構成する。ハイパスフィルタ5の遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できる。チップを構成する基板の裏面にイオン注入によりn型不純物層を設け、p+型半導体基板とpn接合を形成して接合容量をハイパスフィルタ5の容量4とする。

(もっと読む)

窒化物系化合物半導体および窒化物系化合物半導体素子

【課題】長期信頼性が高い窒化物系化合物半導体および窒化物系化合物半導体素子を提供すること。

【解決手段】アルミニウム原子、ガリウム原子、インジウム原子およびボロン原子から選択される1以上のIII族原子と、窒素原子とを含む窒化物系化合物半導体であって、添加物としてドープした金属原子とガリウム格子間原子とが複合体を形成している。好ましくは、前記添加物は鉄またはニッケルである。好ましくは、前記添加物のドープ濃度は、前記ガリウム格子間原子の濃度と同程度である。

(もっと読む)

ヘテロ接合電界効果トランジスタの製造方法

【課題】電流コラプスを抑制し、且つゲートリーク電流を低減するヘテロ接合電界効果トランジスタの製造方法の提供を目的とする。

【解決手段】本発明に係るヘテロ接合電界効果トランジスタの製造方法は、(a)チャネル層30、バリア層40、キャップ層50が順に積層された積層体を備える窒化物半導体層を準備する工程と、(b)前記窒化物半導体層上にSiを含まないキャップ膜110を形成する工程と、(c)工程(b)の後、前記窒化物半導体層に選択的に不純物を注入し、熱処理により前記不純物を活性化して不純物領域60を形成する工程と、(d)工程(c)の後、キャップ膜110を除去して不純物領域60上にソース電極80及びドレイン電極90を形成する工程と、(e)前記窒化物半導体層の少なくとも一部を除去した領域にゲート電極100を形成する工程と、を備える。

(もっと読む)

増幅回路装置

【課題】J−FETを増幅回路装置として採用する場合に、意図しない低周波信号の入力を防止し、規格値を超過するドレイン電流が発することを回避する。

【解決手段】J−FET1の封止部材内で、ゲートと直列に容量を付加し、当該容量とJ−FETのゲート−ソース間に接続される抵抗とによってハイパスフィルタ5を構成する。ハイパスフィルタ5の遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できる。n型半導体基板上にバックゲート領域となるp型半導体層を設けてpn接合を形成し、この接合容量をハイパスフィルタ5の容量とする。

(もっと読む)

窒化物系化合物半導体、窒化物系化合物半導体素子、およびその製造方法

【課題】長期信頼性が高い窒化物系化合物半導体、窒化物系化合物半導体素子、およびその製造方法を提供すること。

【解決手段】アルミニウム原子、ガリウム原子、インジウム原子およびボロン原子から選択される、少なくともガリウム原子を含むIII族原子と、窒素原子とを含む窒化物系化合物半導体であって、前記III族原子の格子間原子を拡散させる拡散促進物質を添加物としてドープしたものである。好ましくは、前記拡散促進物質はリン、砒素、またはアンチモンである。

(もっと読む)

増幅回路装置

【課題】意図しない低周波信号の入力を防止し規格値を超過するドレイン電流が発生することを回避できる増幅回路装置を提供する。

【解決手段】J−FET1の封止部材内で、ゲートと直列に容量4を付加し、当該容量4とJ−FET1のゲート−ソース間に接続される抵抗2とによってハイパスフィルタを構成する。ハイパスフィルタの遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できる。チップを構成する基板の裏面に絶縁層を設けてこれを誘電体とし、導電部材と基板とで平行平板型の容量4を接続する。

(もっと読む)

ヘテロ接合電界効果トランジスタ及びその製造方法

【課題】電流コラプスを抑制し、且つゲートリーク電流を低減するヘテロ接合電界効果トランジスタとその製造方法の提供を目的とする。

【解決手段】本発明に係るヘテロ接合電界効果トランジスタは、バリア層40及びバリア層40上に形成されたキャップ層50を含む窒化物半導体層と、前記窒化物半導体層に下部を埋没するようにして前記窒化物半導体層上に設けられたゲート電極90と、前記窒化物半導体層上に形成されたSiを含まない絶縁膜からなる表面保護膜100とを備える。

(もっと読む)

電界効果トランジスタ

【課題】チャネル層をInAsから構成するヘテロ構造の電界効果トランジスタで、高速で安定した動作ができるようにする。

【解決手段】第1障壁層102に形成されてAlGaSbに対して浅いアクセプタとなる不純物が導入された第1不純物導入領域110と、第2障壁層104に形成されてAlGaSbに対して浅いアクセプタとなる不純物が導入された第2不純物導入領域111とを備える。また、第1不純物導入領域110および第2不純物導入領域111は、チャネル層103の電子に不純物散乱を生じさせない範囲でチャネル層103より離間して形成されている。

(もっと読む)

化合物半導体装置

【課題】ゲート電極の端部でのバイアス電界集中が緩和され、且つ動作時のオン抵抗の増大が抑制された化合物半導体装置を提供する。

【解決手段】キャリア供給層22、及びキャリア供給層22との界面近傍において二次元キャリアガス層23が形成されるキャリア走行層21を有する化合物半導体層20と、化合物半導体層20の主面200上に配置されたソース電極3及びドレイン電極4と、ソース電極3とドレイン電極4間で主面200上に配置されたゲート電極5と、ゲート電極5とドレイン電極4間で主面200上方に配置されたフィールドプレート6と、フィールドプレート直下の二次元キャリアガス層が形成される領域内に配置された、上方にフィールドプレート若しくはゲート電極が配置されていない二次元キャリアガス層が形成される領域よりも導電率が低い低導電性領域210とを備える。

(もっと読む)

61 - 80 / 275

[ Back to top ]