Fターム[5F102GR07]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 半導体基体内に付加領域を設けたもの (876) | 不純物領域 (317)

Fターム[5F102GR07]の下位に属するFターム

ウェル領域 (42)

Fターム[5F102GR07]に分類される特許

81 - 100 / 275

半導体装置

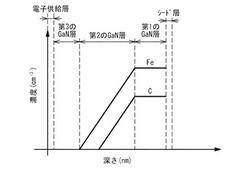

【課題】遷移金属のエネルギー準位を安定にすることが可能な半導体装置を提供することを目的とする。

【解決手段】本発明は、SiC基板10上に設けられ、遷移金属であるFeとFeよりも深い準位を有する不純物であるCとをそれぞれ一定の濃度で含有する第1のGaN層20と、第1のGaN層20上に設けられ、Feの濃度の変化に従いCの濃度が変化する第2のGaN層22と、第2のGaN層22上に設けられ、GaNよりもバンドギャップが大きい電子供給層18と、を有する半導体装置である。

(もっと読む)

電界効果トランジスタ

【課題】III族窒化物半導体からなる電界効果トランジスタにおける高電圧スイッチング時の電流コラプスを効果的に抑制できるようにする。

【解決手段】第1の半導体層103は、少なくともゲート電極106におけるドレイン電極107側の端部の下側の領域において、炭素濃度が1×1017cm−3未満である低炭素濃度領域を有し、基板101の上面から第1の半導体層103及び第2の半導体層104を含むドレイン電極までの半導体層の厚さをd1(μm)とし、低炭素濃度領域の厚さをd2(μm)とし、動作耐圧をVm(V)としたとき、Vm/(110・d1)≦d2<Vm/(110・d1)+0.5の関係を満たし、且つ、緩和状態におけるオン抵抗をRon0とし、動作電圧Vmにおけるオフ状態からオン状態に遷移した100μs後のオン抵抗をRonとしたとき、電流コラプス値の指標とするRonとRon0との比の値が、Ron/Ron0≦3である。

(もっと読む)

半導体装置

【課題】ピンチオフ特性の改善が可能な半導体装置を提供すること。

【解決手段】本発明は、SiC基板10上に設けられた第1のGaN層18と、第1のGaN層18上に設けられた第2のGaN層20(電子走行層)と、第2のGaN層20上に設けられ、GaNよりもバンドギャップが大きいAlGaN電子供給層16と、を有し、第1のGaN層18のアクセプタ濃度は第2のGaN層20のアクセプタ濃度よりも高い半導体装置である。

(もっと読む)

電界効果トランジスタ

【課題】歩留りの低下を抑制する。

【解決手段】開口部121.1の形成により、第1の半導体層110の上面のうち、上方に第2の半導体層120が形成されていない部分の少なくとも一部には、絶縁体130.1が形成される。開口部121.1には、絶縁体130.1を覆うようにソース電極S10が形成される。ソース電極S10は、第1の半導体層110と前記第2の半導体層120との界面と接するように形成される。

(もっと読む)

半導体トランジスタおよびその製造方法

【課題】FETの閾値電圧のばらつきのない半導体トランジスタおよびその製造方法を提供する。

【解決手段】半導体トランジスタ100は、基板1と、基板1の上方に形成された第1化合物半導体層103と、第1化合物半導体層103上に形成され、第1化合物半導体層103よりもバンドギャップの大きい第2化合物半導体層104と、第2化合物半導体層104内の少なくとも一部に、酸素がドープされた酸素ドープ領域105と、第2化合物半導体層104上に形成された第3化合物半導体層106と、第1化合物半導体層103に電気的に接続されたソース電極107およびドレイン電極109と、酸素ドープ領域105の上方に、酸素ドープ領域105に接するように形成されたゲート電極108とを有する。

(もっと読む)

半導体装置

【課題】円弧状の部分を有する電極と先端部分を有する電極での円弧状の部分と先端部分との間で流れる電流密度を均一化するために、電極の先端部分における電流集中を緩和させ、電流集中に起因する半導体装置の破壊を防止できる半導体装置を提供する。

【解決手段】半導体装置は、基板と、基板上に形成され、かつヘテロ接合に基づくキャリア走行層を有する化合物半導体層と、化合物半導体層上に形成される第1の主電極14と、化合物半導体層上において平面的に見て第1の主電極14を包囲するように形成され、かつ直線領域と円弧領域とを有する第2の主電極15と、化合物半導体層上において第1の主電極及び第2の主電極に対向するように形成された制御電極16と、を備え、第1の主電極及び第2の主電極の間に電流が流れる半導体装置であって、第1の主電極と第2の主電極の円弧領域との間に電流制限部19を設けた。

(もっと読む)

電界効果型トランジスタ

【課題】正孔の蓄積によるキンク現象の発生および耐圧の低下を、効果的に抑制できるようにする。

【解決手段】半絶縁性のInPからなる基板101と、基板101の上に形成されて、炭素(C)がp形の不純物として導入されたGaAsSbからなる正孔走行層102と、正孔走行層102の上に形成されたInGaAsからなるチャネル層103と、チャネル層103の上に形成された電子供給層104と、電子供給層104の上に形成された障壁層105とを備える。

(もっと読む)

半導体基板、半導体基板の製造方法、電子デバイス、および電子デバイスの製造方法

【課題】半導体基板におけるリーク電流を低減する。

【解決手段】ベース基板110と、ベース基板上110に形成され、第1の伝導型の多数キャリアを含む第1チャネル層208を有する第1半導体部200と、第1半導体部200の上方に形成され、第1半導体部200の不純物準位よりも深い準位の不純物準位を形成する不純物を有する分離層300と、分離層300の上方に形成され、第1チャネル層が含む第1の伝導型の多数キャリアと反対の伝導型の多数キャリアを含む第2チャネル層408を有する第2半導体部400とを備える半導体基板。

(もっと読む)

III族窒化物半導体電子デバイス、III族窒化物半導体電子デバイスを作製する方法

【課題】Id―max特性低下を低減可能なIII族窒化物半導体電子デバイスが提供される。

【解決手段】III族窒化物半導体電子デバイス11では、チャネル層21はAlGaNからなると共に、バリア層23はチャネル層21より大きなバンドギャップのAlGaNからなる。チャネル層21が、GaNではなく、AlGaNからなるので、III族窒化物半導体電子デバイス11においてId―max特性低下を低減可能である。また、第1及び第2の電極17、19は、それぞれ、チャネル層21の第1及び第2の部分21a、21b上に設けられる。チャネル層21において第1の部分21aの不純物濃度が第2の部分21bの不純物濃度と同じであるから、チャネル層21における第1の部分にイオン注入が行われていない。半導体積層15に部分的にイオン注入を行っていない。このイオン注入の使用回避により、Id―max特性低下を更に低減可能である。

(もっと読む)

接合型電界効果トランジスタ、その製造方法及びアナログ回路

【課題】外部ノイズの影響を低減できるJFETを提供する。

【解決手段】本発明に係るJFET50は、p型半導体基板1と、p型半導体基板1の表面に形成されているn型チャネル領域3と、n型チャネル領域3内に形成されており、n型チャネル領域3よりも不純物濃度の高いn型埋め込み領域4と、n型チャネル領域3の表面に形成されているp型ゲート領域6と、n型チャネル領域3の表面に、p型ゲート領域6を挟むように形成されているn型ドレイン/ソース領域7及びn型ドレイン/ソース領域8とを備え、n型埋め込み領域4は、n型ドレイン/ソース領域7及びn型ドレイン/ソース領域8の一方の下方に形成されており、他方の下方に形成されていない。

(もっと読む)

HFET

【課題】耐圧が高いHFET(Heterojunction−FET)を提供する。

【解決手段】ヘテロ接合16aに生じる2次元電子ガスをチャネルとするHFET10であって、第1半導体領域16と、第1半導体領域16上で第1半導体領域16とヘテロ接合している第2半導体領域18と、第2半導体領域18上に形成されたソース電極20、ドレイン電極22及びゲート電極24と、第1半導体領域16と接しており、ソース電極20と導通しているp型の第3半導体領域14を有している。ゲート電極24とドレイン電極22の間の第2半導体領域18の上面のうちの、ゲート電極24に隣接する範囲の上面は、第1表面準位密度を有する第1領域40であり、第1領域40に隣接する範囲の上面は、第1表面準位密度より低い第2表面準位密度を有する第2領域42である。第3半導体領域14は、第2領域42の下側で第1半導体領域16に接している。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧向上や短チャンネル効果の抑制を可能とする半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、半導体基板であるSiC基板1上に形成された、バッファ層2と、バッファ層2上に形成された、バッファ層2よりもバンドギャップが小さいチャネル層3と、チャネル層3上に形成された、チャネル層3よりもバンドギャップが大きいバリア層4と、バリア層4上に互いに離間して形成された、ソース、ドレイン電極7、8と、ソース、ドレイン電極7、8下から、バリア層4を通ってチャネル層3中にそれぞれ達する、不純物領域5とを備え、不純物領域5の下端は、バッファ層2に達しない。

(もっと読む)

半導体装置

【課題】III-V族窒化物半導体に設けるオーミック電極のコンタクト抵抗を低減しながらデバイスの特性を向上できるようにする。

【解決手段】半導体装置(HFET)は、SiC基板11上にバッファ層12を介在させて形成された第1の窒化物半導体層13と、該第1の窒化物半導体層13の上に形成され、該第1の窒化物半導体層13の上部に2次元電子ガス層を生成する第2の窒化物半導体層14と、該第2の窒化物半導体層14の上に選択的に形成されたオーム性を持つ電極16、17とを有している。第2の窒化物半導体層14は、底面又は壁面が基板面に対して傾斜した傾斜部を持つ断面凹状のコンタクト部14aを有し、オーム性を持つ電極16、17はコンタクト部14aに形成されている。

(もっと読む)

III族窒化物半導体からなる半導体装置およびその製造方法、電力変換装置

【課題】主面をm面とするIII 族窒化物半導体で構成されたHFETにおいて、正のしきい値電圧を高めること。

【解決手段】HFET100は、凹凸加工されたa面サファイア基板101上に、m面を主面とするGaNからなるバッファ層102、ノンドープのGaNからなるチャネル層103、ノンドープのAlGaNからなる障壁層104、酸素ドープのn−AlGaNからなるキャリア供給層105を有している。キャリア供給層105は2つの領域に分離して形成されている。キャリア供給層105は、障壁層104上に選択的に再成長させて形成した層である。ゲート電極109にバイアスを印加しない状態では、ゲート電極109直下に2DEGが形成されないため、正のしきい値電圧を高めることができる。

(もっと読む)

半導体素子用エピタキシャル基板および半導体素子

【課題】InAlN/GaNヘテロ構造を有し、かつオーミックコンタクト特性の優れた半導体素子用のエピタキシャル基板を提供する。

【解決手段】半導体素子用エピタキシャル基板10Aが、下地基板1と、GaNからなるチャネル層3と、AlNからなるスペーサ層4と、III族元素としてInとAlとGaとを含む障壁層5と、を備え、障壁層が、InxAl1-xN(0<x<1)からなるマトリックス層にGa原子がドープされ、障壁層のGa原子の濃度が1.2×1020cm-3以下であるようにする。

(もっと読む)

窒化物電子デバイス、窒化物電子デバイスを作製する方法

【課題】チャネル層のキャリア濃度が増大することを避けてリークを低減できる構造を有する、窒化物電子デバイスを提供する。

【解決手段】半導体積層15の斜面15a及び主面15cは、それぞれ、第1及び第2の基準面R1、R2に対して延在する。半導体積層15の主面15cは六方晶系III族窒化物のc軸方向を示す基準軸Cxに対して5度以上40度以下の範囲内の角度で傾斜すると共に、第1の基準面R1の法線と基準軸Cxとの成す角度は第2の基準面R2の法線と基準軸Cxとの成す角度より小さいので、チャネル層19の酸素濃度を1×1017cm−3未満にすることができる。これ故に、チャネル層19において、酸素添加によりキャリア濃度が増加することを避けることができ、チャネル層を介したトランジスタのリーク電流を低減できる。

(もっと読む)

半導体装置およびその製造方法

【課題】 優れた縦方向耐圧を得た上で、安定して低いオン抵抗を確保することができる、半導体装置およびその製造方法を提供する。

【解決手段】n型ドリフト層4、p型層6、およびn型表層8、を含むGaN系積層体、に形成され、開口部28に露出するGaN系積層体を覆うチャネルを含む再成長層27が形成され、チャネルが電子走行層の電子供給層との界面に形成される二次元電子ガスであって、p型層6の厚みが、電子走行層22の厚みをdとして、d〜10dの範囲にあり、かつ、(p型層/n型表層)界面から該n型表層内へと、該p型層におけるp型不純物濃度から濃度が減少するp型不純物傾斜層7が設けられていることを特徴とする。

(もっと読む)

半導体装置

【課題】 立ち上がり電圧低減と高耐圧実現の両立を可能とする構造を提案する。

【解決手段】 SiC縦型ダイオードにおいて、カソード電極21と、n++カソード層10と、n++カソード層上のn−ドリフト層11と、一対のp+領域12と、n−ドリフト層11とp+領域12の間に形成され、且つ一対のp+領域12に挟まれたn+チャネル領域16と、n++アノード領域14と、n++アノード領域14とp+領域12に形成されたアノード電極22を備える。

(もっと読む)

III族窒化物半導体素子、III族窒化物半導体素子の製造方法、および電子装置

【課題】 アクセス抵抗およびオン抵抗が低いIII族窒化物半導体素子、III族窒化物半導体素子の製造方法、および電子装置を提供する。

【解決手段】

障壁層902は、チャネル層901上方にヘテロ接合され、

チャネル層901の上部の一部およびその上方の障壁層902が除去されて凹部が形成され、

チャネル層901および障壁層902の一部にn型導電層領域904が形成され、

n型導電層領域904は、前記凹部の表面を含み、

n型導電層領域904の深さTimpが、n型導電層領域904表面の各部から前記表面と垂直方向の測定値で15nm以上であり、

オーミック電極906および907は、前記凹部の表面を介して前記n型導電層領域にオーミック接触していることを特徴とする、III族窒化物半導体素子。

(もっと読む)

電界効果トランジスタ及びその評価方法

【課題】連続動作の際に生じるオン抵抗の増大を抑制した電界効果トランジスタを実現できるようにする。

【解決手段】電界効果トランジスタは、窒化物半導体からなり、τc/τe>exp{−46.5+45.7exp(logx/21.6)+0.2exp(logx/0.27)}の関係を満たす。但し、xはR∞/R0−1であり、R∞はオフ状態において所定の時間保持した後、オン状態へとスイッチした直後のオン抵抗であり、R0はオフ状態の保持時間が所定の時間以内の場合にオフ状態からオン状態へとスイッチした直後のオン抵抗であり、τcはコラプスを引き起こす電子がトラップされる捕獲時定数であり、τeはコラプスを引き起こすトラップされた電子の放出の時定数である。

(もっと読む)

81 - 100 / 275

[ Back to top ]