Fターム[5F102GS03]の内容

接合型電界効果トランジスタ (42,929) | ゲート電極構造 (2,097) | 断面形状 (702)

Fターム[5F102GS03]の下位に属するFターム

上部が幅広(T字状) (372)

下部が幅広 (4)

左右非対称 (75)

Fターム[5F102GS03]に分類される特許

81 - 100 / 251

電界効果トランジスタ、電界効果トランジスタの製造方法および電子装置

【課題】ゲートリーク電流の増加が抑制された信頼性の高い電界効果トランジスタを提供する。

【解決手段】 ゲート電極は、第1金属層16および第2金属層17を含み、

第2金属層17は、第1金属層16よりも導電率が高く、

第1金属層16の上方に、第2金属層17が積層され、

ソース電極18およびドレイン電極19は、半導体層12〜14上にオーム性接触し、

ゲート電極は、ソース電極18およびドレイン電極19の間に配置され、かつ、第1金属層16により半導体層上にショットキー性接触し、

半導体層上におけるソース電極18およびゲート電極の間、ならびに、ゲート電極およびドレイン電極19の間は、絶縁膜15Aにより覆われ、

かつ、

第2金属層17下面の全体が第1金属層16上面の上方に重なっているか、または、第1金属層16の厚みが絶縁膜15Aの厚み以上であることを特徴とする電界効果トランジスタ。

(もっと読む)

III族窒化物半導体からなる半導体装置およびその製造方法、電力変換装置

【課題】主面をm面とするIII 族窒化物半導体で構成されたHFETにおいて、正のしきい値電圧を高めること。

【解決手段】HFET100は、凹凸加工されたa面サファイア基板101上に、m面を主面とするGaNからなるバッファ層102、ノンドープのGaNからなるチャネル層103、ノンドープのAlGaNからなる障壁層104、酸素ドープのn−AlGaNからなるキャリア供給層105を有している。キャリア供給層105は2つの領域に分離して形成されている。キャリア供給層105は、障壁層104上に選択的に再成長させて形成した層である。ゲート電極109にバイアスを印加しない状態では、ゲート電極109直下に2DEGが形成されないため、正のしきい値電圧を高めることができる。

(もっと読む)

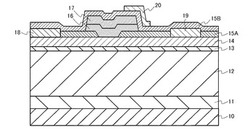

電界効果トランジスタ、電界効果トランジスタの製造方法、および電子装置

【課題】 ミリ波以上の周波数において、安定して、高い利得および動作周波数が得られる電界効果トランジスタを提供する。

【解決手段】 基板11上の動作層13の上に、ソース電極14、ドレイン電極15、ゲート電極18、絶縁膜17が形成され、

ゲート電極18は、ソース電極14とドレイン電極15の間に配置され、

絶縁膜17は、ゲート電極18とドレイン電極15の間に配置され、

フィールドプレート電極19は、絶縁膜17上に形成され、かつ、ソース電極14と電気的に接続され、

ゲート電極18上部は、ソース電極14側およびドレイン電極15側に突出し、

フィールドプレート電極19下端は、ゲート電極18下端よりも下方に配置され、

フィールドプレート電極19上端は、ゲート電極19上部においてドレイン電極15側に最も突出した部分よりも下方に配置されている電界効果トランジスタ。

(もっと読む)

半導体装置及び半導体装置の動作方法

【課題】トランジスタの閾値電圧を高くする。

【解決手段】フローティング電極110は半導体層102上に形成されており、絶縁層はフローティング電極110上に形成されている。バイアス電極134は、絶縁層を介してフローティング電極110の一部に対向することにより、フローティング電極110と容量結合し、かつフローティング電極110が半導体層102にチャネル領域を形成しない大きさの電圧が印加される。制御電極132は、絶縁層を介してフローティング電極110の他の部分に対向することにより、フローティング電極110と容量結合し、かつトランジスタのオン/オフを制御するための制御電圧が入力される。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明の半導体装置は、nチャネルの高電子移動度トランジスタ(HEMT)とpチャネル電界効果トランジスタとを単一の基板上に形成した。

【解決手段】nチャネル電界効果トランジスタは、第1チャネル層7と、この第1チャネル層7にヘテロ接合し、n型の電荷を供給するn型第1障壁層6と、n型第1障壁層6に対してpn接合型の電位障壁を有するp型ゲート領域10とを備え、pチャネル電界効果トランジスタは、p型の第2チャネル層13と、pn接合型の電位障壁を有するn型ゲート領域18とを備える。各トランジスタはpn接合型のゲート領域を有するのでターンオン電圧を高くすることが可能となり、ゲート逆方向リーク電流を減少させたエンハンスメントモードでの動作を実現した。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】化合物半導体装置のソース電極、ドレイン電極及びゲート電極を形成するいずれの領域においても、残渣のない良好な半導体/金属界面が得られるようにする。

【解決手段】化合物半導体装置の製造方法を、基板1上に化合物半導体積層構造4を形成する工程と、化合物半導体積層構造上に金属膜5A〜5Cを形成する工程と、金属膜上にソース電極7及びドレイン電極8を形成する工程と、金属膜の一部を酸化又は窒化して、金属酸化物膜又は金属窒化物膜5CXを形成する工程と、金属酸化物膜又は金属窒化物膜上にゲート電極9を形成する工程とを含むものとする。

(もっと読む)

高周波半導体装置

【課題】小型かつ高性能な半導体装置を提供すること。

【解決手段】第1のGaAs層11、およびこのGaAs層11に対して水平方向が長手方向となるように形成された四角柱状の第2のGaAs層12と、第1、第2のGaAs層11、12の表面に形成されたAlGaAs層13と、第1のGaAs層11の裏面に形成されたドレインパッド14と、第2のGaAs層12上のAlGaAs層13の表面に形成された帯状のソースパッド16と、第1のGaAs層11上のAlGaAs層13上のうち、第2のGaAs層12の両側に形成された帯状のゲートパッド15と、を具備し、第1のGaAs層11の厚さは、第2のGaAs層12のうち、両側にゲートパッド15が形成された領域(ゲート領域18)を除く部分の厚さよりも厚く形成される。

(もっと読む)

窒化物電子デバイスを作製する方法

【課題】ゲートリーク電流を低減できる、窒化物電子デバイスを作製する方法を提供する。

【解決手段】時刻t0で基板生産物を成長炉に配置した後に、摂氏950度まで基板温度を上昇する。基板温度が十分に安定した時刻t3でトリメチルガリウム及びアンモニアを成長炉に供給して、i−GaN膜を成長する。時刻t5で基板温度が摂氏1080度に到達する。基板温度が十分に安定した時刻t6でトリメチルガリウム、トリメチルアルミニウム及びアンモニアを成長炉に供給して、i−AlGaN膜を成長する。時刻t7でトリメチルガリウム及びトリメチルアルミニウムの供給を停止して成膜を停止した後に、速やかに、成長炉へアンモニア及び水素の供給を停止すると共に窒素の供給を開始して、成長炉のチャンバ中においてアンモニア及び水素の雰囲気を窒素の雰囲気に変更する。窒素の雰囲気が形成された後に、時刻t8で基板温度の降下を開始する。

(もっと読む)

電界効果トランジスタ

【課題】電流コラプスが抑制された窒化物半導体を用いた電界効果トランジスタを容易に実現できるようにする。

【解決手段】電界効果トランジスタは、基板100の上に形成され、第1の窒化物半導体層122及び第2の窒化物半導体層123を有する半導体層積層体102を備えている。半導体層積層体102の上には、互いに間隔をおいてソース電極131及びドレイン電極132が形成されている。ソース電極131とドレイン電極132との間には、ソース電極131及びドレイン電極132と間隔をおいてゲート電極133が形成されている。ドレイン電極132の近傍には正孔注入部141が形成されている。正孔注入部141は、p型の第3の窒化物半導体層142及び第3の窒化物半導体層142の上に形成された正孔注入電極143を有している。ドレイン電極132と正孔注入電極142とは、電位が実質的に等しい。

(もっと読む)

半導体装置

【課題】半絶縁性基板に形成されたゲートパッドにマイナスの電圧が印加され、半絶縁性基板の裏面に形成された裏面電極にプラスの電圧が印加されても、リーク電流を抑制できる半導体装置を提供する。

【解決手段】裏面電極10が形成された半絶縁性基板11の表面上に並列に形成された、複数のゲート電極15がゲート電極接続部21に接続されるとともに、このゲート電極接続部21が複数に分割された半導体装置であって、ゲート電極接続部21間の半絶縁性基板11の表面に形成されたn型の抵抗層22と、このn型の抵抗層22の周囲を覆うように、p型不純物層23と、このp型不純物層23の周囲を覆うように、所望の濃度で形成されたn型不純物層24と、を具備し、ゲートパッド29は、ゲート電極接続部21と、このゲート電極接続部21に隣接するn型の抵抗層22上の引き出し電極25とを接続するように形成される。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減と、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】凹部4c内に形成されたi型(イントリンシック半導体)側壁層5を介してp+型ゲート領域6を形成する。このような構成とすれば、n+型層4とp+型ゲート領域6との間にさらにp+型ゲート領域6よりも低濃度のp-型層が必要とされない。このため、n-型チャネル層3に直接接触している高濃度のp+型ゲート領域6によって、n-型チャネル層3内に伸びる空乏層幅を制御できる。したがって、n+型層4とp+型ゲート領域6との間にさらにp-型層が備えられる場合と比較して、ゲート印加電圧が高電圧になることを抑制できる。また、p+型ゲート領域6の側面がi型側壁層5によってn+型層4と分離されるため、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスを低減できる。

(もっと読む)

化合物半導体装置

【課題】電流コラプスを抑制しつつ所望の特性が得られる化合物半導体装置を提供する。

【解決手段】化合物半導体装置は、GaNからなる電子走行層120と、AlGaNからなる電子供給層130と、電子供給層上に設けられたソース電極150、ゲート電極160およびドレイン電極170と、少なくともソース電極とゲート電極との間およびゲート電極とドレイン電極との間に設けられたGaNからなるキャップ層140と、ゲート電極とドレイン電極との間のキャップ層に設けられたリセス部と、リセス部とドレイン電極との間のキャップ層に設けられリセス部よりも大きな厚みを有する層厚部と、を備える。

(もっと読む)

半導体装置

【課題】オン抵抗の増加を抑制すると共にリーク電流を低減させることができる半導体装置を提供すること。

【解決手段】本発明の一態様に係る半導体装置は、ノンドープInGaAs層8と、ノンドープInGaAs層8上に形成された、第1リセス部を備えるSiドープGaAs層1と、ノンドープInGaAs層8とSiドープGaAs層1との間に形成され、第1リセス部内に設けられた第2リセス部を備える、ノンドープオーダ系InGaP層4とその上に形成されるノンドープGaAs層3からなる2層構造半導体層と、第2リセス部内において、ノンドープInGaAs層8上に設けられたCドープGaAs層13と、CドープGaAs層13と、ノンドープGaAs層3及びノンドープオーダ系InGaP層4の界面との間に設けられると共に、ノンドープオーダ系InGaP層4とCドープGaAs層13との間の一部には設けられていない側壁絶縁膜17とを備える。

(もっと読む)

電界効果トランジスタ

【課題】高電圧を印加しても壊れにくい電界効果トランジスタを提供すること。

【解決手段】この電界効果トランジスタは、略同一の第1、第2トランジスタ部11,12を備える。第1のトランジスタ部11は、ヘテロ接合を含むIII族窒化物半導体層構造、III族窒化物半導体層構造上に間隔をおいて配置されたソース電極5およびドレイン電極7、フィールドプレート91を有するゲート電極6、ドレイン電極7を被覆するように配置された絶縁体層8を有する。フィールドプレート91は、ドレイン電極7を覆うようにひさし状に延在する。第2のトランジスタ部12は、第1のトランジスタ部11と略面対称に配置されている。第1のトランジスタ部11のIII族窒化物半導体層構造、絶縁体層8およびドレイン電極7は、第2のトランジスタ部12において対応する構造または層と一体化されている。

(もっと読む)

窒化物半導体装置

【課題】高電圧印加時にフィールドプレート構造端に集中する電界強度を緩和し、高耐圧で信頼性の高い窒化物半導体装置を提供する。

【解決手段】フィールドプレート構造を備えた窒化物半導体装置において、ゲート電極18に、オフ制御の制御電圧を印加するとき、フィールドプレート構造の傾斜面部直下の窒化物半導体層中13にはキャリアが存在しないようにする。

(もっと読む)

半導体装置およびその製造方法

【課題】DモードとEモードの素子を組み合わせた半導体装置およびその製造方法を提供する。

【解決手段】DモードとEモードのJFETにおけるチャネル領域を設定する場所にそれぞれ凹部2aと凸部2bを備えることで、同一基板上に厚みが異なるn型チャネル層3を形成する。そして、このような厚みが異なるn型チャネル層3によってDモードとEモードで作動するJFETを同一基板上に備えることができるため、SiCでもDモードとEモードのJFETを組み合わせたSiC半導体装置を実現することが可能となる。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減を図ると共に、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】p+型ゲート領域2をSiC基板1の内部に埋め込んだ構造とする。これにより、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減を図ることが可能となる。また、p+型ゲート領域2がn-型チャネル層3に直接接触させられる構造であるため、p+型ゲート領域2から広がる空乏層によって容易にn-型チャネル層3をピンチオフさせることができ、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制できる。

(もっと読む)

半導体装置およびその製造方法

【課題】 サージ電圧等に対するバイパス用の保護部を備え、耐圧性能および低いオン抵抗(低いオン電圧)を実現し、かつ、構造が簡単な、大電流用の、半導体装置およびその製造方法を提供する。

【解決手段】 支持基体上にオーミック接触するGaN層を有するn+型GaN基板1と、第1領域R1上におけるn−型GaNドリフト層2を有するFETと、第2領域R2においてn−型GaNドリフト層2にショットキー接触するアノード電極を有するSBDとを備え、FETとSBDとは並列配置されており、n+型GaN基板1の裏面に、FETのドレイン電極DおよびSBDのカソード電極Cを備えることを特徴とする。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制する。

【解決手段】トレンチ6の先端部に形成されたn-型チャネル層7がトレンチ6の長辺に位置する部分よりも膜厚が厚くなるため、そのトレンチ6の先端部においてJFET構造が構成されないようにする。例えば、トレンチ6の先端部の周辺を含めてn+型SiC基板1の外縁部においてn+型ソース領域4が除去されると共に、トレンチ6の先端部においてn-型チャネル層7および第2ゲート領域8が除去された凹形状とする。これにより、トレンチ6の先端部のJFET構造の閾値がトレンチ6の長辺に位置する部分のJFET構造の閾値からずれることによる影響を受けることがない。したがって、ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制できる構造のSiC半導体装置とすることが可能となる。

(もっと読む)

窒化物半導体素子および窒化物半導体素子の製造方法

【課題】オーミック電極とオーミックリセス部とのコンタクト抵抗を低減した窒化物半導体素子および窒化物半導体素子の製造方法を提供する。

【解決手段】窒化物半導体素子400は、基板401上に形成された第1の窒化物半導体層402と、第1の窒化物半導体層402上に形成され、第1の窒化物半導体層402と比べてバンドギャップが大きい第2の窒化物半導体層403と、少なくとも第2の窒化物半導体層403に形成されたオーミックリセス部405と、オーミックリセス部405に接触して設けられたオーミック電極407とを備え、オーミックリセス部405は、オーミック電極407と接触する面の少なくとも一部に凹凸構造を有する。

(もっと読む)

81 - 100 / 251

[ Back to top ]