Fターム[5F102GS03]の内容

接合型電界効果トランジスタ (42,929) | ゲート電極構造 (2,097) | 断面形状 (702)

Fターム[5F102GS03]の下位に属するFターム

上部が幅広(T字状) (372)

下部が幅広 (4)

左右非対称 (75)

Fターム[5F102GS03]に分類される特許

141 - 160 / 251

窒化物半導体装置

【課題】高耐圧でスイッチングスピードに優れ高い高周波特性を有するノーマリオフ型のHEMTを提供すること。

【解決手段】第1のバンドギャップを有する第1の窒化物半導体層と前記第1のバンドギャップよりも大きい第2のバンドギャップを有する第2の窒化物半導体層とを備える主半導体領域と、前記主半導体領域上に形成されるソース電極5と、前記主半導体領域上において前記ソース電極と離間して形成されるドレイン電極6と、前記第1の窒化物半導体層上において前記ソース電極と前記ドレイン電極との間に形成される第3の窒化物半導体層と、前記第3の窒化物半導体層上に形成され且つp型の導電性を有する第4の窒化物半導体層と、前記第4の窒化物半導体層上に形成されるゲート電極7と、を備え、前記第3の窒化物半導体層が前記第1のバンドギャップよりも小さい第3のバンドギャップを有することを特徴とする窒化物半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜におけるリーク電流を抑制し、安定なFET特性を得ること。

【解決手段】本半導体装置の製造方法は、基板上10にGaN系半導体層15を形成する工程と、GaN系半導体層上15に、TMAと、O2またはO3とを用い、酸化アルミニウムからなるゲート絶縁膜18をALD法により形成する工程と、ゲート絶縁膜18の上にゲート電極24を形成する工程と、を含む。本半導体装置の製造方法によれば、ゲート絶縁膜中のリーク電流を抑制し、安定なFET特性を得ることができる。

(もっと読む)

化合物半導体電界効果トランジスタ及びその製造方法

【課題】化合物半導体電界効果トランジスタの高集積化及び高電力化を図る。

【解決手段】角柱状又は角錐台状の、オン状態のときに軸方向に電流が流れる半導体部43と、半導体部の周囲に、第1絶縁層50、制御電極層60及び第2絶縁層72が、半導体部の軸方向に沿って順に積層された周辺部とを備える。半導体部が、角柱状又は角錐台状の電子走行部44と、電子走行部の側面44c上に形成された電子供給部46とを備えて構成される。

(もっと読む)

窒化物半導体装置

【課題】高耐圧でスイッチングスピードに優れ高い高周波特性を有するノーマリオフ型のHEMTを提供すること。

【解決手段】第1のバンドギャップを有する第1の窒化物半導体層2と前記第1のバンドギャップよりも大きい第2のバンドギャップを有し前記第1の窒化物半導体層上とヘテロ接合される第2の窒化物半導体層3とを備える主半導体領域と、前記主半導体領域上に形成されるソース電極5と、前記主半導体領域上において前記ソース電極5と離間して形成されるドレイン電極6と、前記第1の窒化物半導体層上において前記ソース電極5と前記ドレイン電極6との間に形成される第3の窒化物半導体層10と、前記第3の窒化物半導体層10上に形成されるゲート電極7とを備え、前記第3の窒化物半導体層10が前記第1のバンドギャップよりも小さい第3のバンドギャップを有することを特徴とする窒化物半導体装置。

(もっと読む)

半導体装置

【課題】ノーマリオフ特性が実現され、飽和電流値低下が生じず、ゲート電圧に対するドレイン・ソース間電流特性が良好なHEMTを実現する半導体装置を提供する。

【解決手段】第1半導体層131と、第1半導体層131の主面135上に積層され、第1半導体層131の主面135側に2DEG層137を生じさせる第2半導体層133と、第1半導体層131及び第2半導体層133と比して電子親和力χが大きい半導体材料からなり、2DEG層137と電気的に接続された第3半導体層139と、第2半導体層133及び第3半導体層139上に設けられた絶縁膜157と、第3半導体層139にオーミック接続される第1電極151と、第2半導体層133及び第3半導体層139上に絶縁膜157を介して設けられた第2電極153と、第1電極151との間に第2電極153を介在させ、2DEG層137と電気的に接続された第3電極155とを備える。

(もっと読む)

トランジスタ及びその駆動方法、双方向スイッチ及びその駆動方法

【課題】高電圧下でも使用でき、動作の制御性を向上させた半導体装置を提供する。

【解決手段】半導体装置は、基板101と、基板101の上方に設けられた半導体からなる発光部150と、基板101の上方に設けられ、発光部150から放射される光を受け、半導体からなる電気伝導層と、電気伝導層に接続された第1の電極110及び第2の電極111とを備えている。発光部150から放射された光を電気伝導層108が受光することにより、電気伝導層108を構成する第1の窒化物半導体層108と第2の窒化物半導体層109の界面を介して第1の電極と第2の電極との間を流れる電流が、オンまたはオフの状態をとる。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】本発明は、RFデバイスの低抵抗化による高効率化と信頼性の向上を図ることが可能な化合物半導体装置とその製造方法を提供する。

【解決手段】化合物半導体基板に形成されたメサ22と、メサ22の壁面に形成された曲率表面を有する側壁16と、メサ22上に形成されるゲート電極と、ゲート電極と一体化され、側壁16の表面に形成されるゲートメタル18と、を備える。

(もっと読む)

半導体装置

【課題】電極の断線が生じても動作可能であり、かつ大電力で動作することが可能な、小型の半導体装置を提供する。

【解決手段】セル160は、六角形の素子形成領域を画定する開口部を形成するように形成されたソース電極182と、素子形成領域に、ソース電極182と一定距離を隔てて帯状に形成されたドレイン電極180と、ソース電極182とドレイン電極180との双方から所定の距離を隔てて形成されたゲート電極184とを含む。ゲート電極184の各辺の中央部分からソース電極182に重畳するようにゲート引出電極186を形成し、ゲート引出電極186とソース電極182との間には絶縁膜を形成する。

(もっと読む)

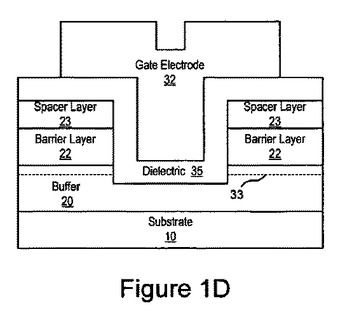

常時オフ半導体デバイスおよびその作製方法

常時オフ半導体デバイスが提供される。III族窒化物バッファ層が提供される。III族窒化物バリア層がIII族窒化物バッファ層上に設けられる。非伝導性スペーサ層がIII族窒化物バリア層上に設けられる。III族窒化物バリア層およびスペーサ層がエッチングされてトレンチを形成する。トレンチはバリア層を貫いて延びてバッファ層の一部を露出させる。誘電体層がスペーサ層上およびトレンチ内に形成され、ゲート電極が誘電体層上に形成される。半導体デバイスの形成に関連する方法も提供される。  (もっと読む)

(もっと読む)

ヘテロ接合電界効果トランジスタ

【課題】ゲート電極破壊が起こらず、高電圧で安定して動作し、かつリーク電流を低減することができるヘテロ接合電界効果トランジスタを提供すること。

【解決手段】基板1の表面上にチャネル層2および障壁層3がこの順で積層された半導体層Sと、半導体層S上のトランジスタ領域11に形成されたトランジスタ部11Aおよびホール抜き領域12に形成されたホール抜き部12Aと、トランジスタ領域11とホール抜き領域12との間の半導体層Sの一部を選択除去して設けられた絶縁部10とを備え、ホール抜き部12Aにおけるホール抜き電極8と第2ドレイン電極9の間でアバランシェ降伏が生じるように、ホール抜き電極8と第2ドレイン電極9の間の耐圧が、トランジスタ部11Aのゲート電極と第1ドレイン電極との間の耐圧よりも小さく設定されたことを特徴とするヘテロ接合電界効果トランジスタ。

(もっと読む)

HEMT装置及びその製造方法

HEMT装置及びHEMT装置の製造方法であって、HEMT装置は、基板(12)上のバッファ層(14)と、バッファ層(14)上の半導体層と、半導体層上の絶縁層(16,17)と、半導体層に接触するソース電極(22)及びドレイン電極(23)と、ソース電極(22)とドレイン電極(23)との間のゲート電極(24,104,114)と、を備え、ゲート電極(24,104,114)の下の半導体層に配置されたチャネルをピンチオフ状態にしている。 (もっと読む)

半導体装置の製造方法

【課題】 結晶成長させたp型窒化物半導体領域をエッチングすることなく、n型半導体層とp型半導体層が隣接する構造を有する半導体装置の製造方法を提供する。

【解決手段】 本半導体装置の製造方法は、n型半導体層22の表面の一部をエッチングして溝17を形成する溝形成工程と、溝17の内外に亘るn型半導体層22の表面上にp型窒化物半導層16を結晶成長させるp型窒化物半導体層形成工程と、溝形成工程でエッチングされなかった範囲のn型半導体層22の上部に位置するp型窒化物半導体層16の少なくとも一部にn型不純物を注入し、p型窒化物半導体層16の表面からn型半導体層22に達するn型領域10を形成するn型領域工程を備えている。

(もっと読む)

促進された導電性を有する非パンチスルー半導体チャネルを備えた半導体素子及び製法

半導体素子が記載されており、当該素子における電流の流れは変換接合(例えば、p−n接合又は金属−半導体接合)の間に閉じ込められる。当該素子は、非パンチスルー挙動と、促進された導電可能性とをもたらす。当該素子は、接合型電界効果トランジスタ(JFET)、スタティック誘導トランジスタ(SIT)、接合型電界効果サイリスタ、又はJFET電流リミッタであり得る。当該素子は、炭化ケイ素(SiC)などの広いバンドギャップ半導体により製造され得る。いくつかの実施形態によれば、当該素子は、通常OFFのSiC垂直接合型電界効果トランジスタであり得る。当該素子の製法、及び当該素子を備えた回路も記載されている。 (もっと読む)

半導体装置

【課題】電界集中を緩和し耐圧を向上しつつ、電流コラプスを低減しかつリーク電流を減少することができる半導体装置を提供する。

【解決手段】半導体装置1において、窒化物系半導体2上に互いに離間して配設された制御電極5及び第2の主電極4と、窒化物系半導体2上の制御電極5と第2の主電極4との間に配設された第1の絶縁体6と、制御電極5に一端が電気的に接続され、他端が第1の絶縁体6上において制御電極5と第2の主電極4との間に配設された第1のフィールドプレート5FPと、第1の絶縁体6上において一端が第1のフィールドプレート5FPに接続され、他端が第2の主電極4に向かって延伸され、第1のフィールドプレート5FPに比べて高いシート抵抗を有する抵抗性フィールドプレート7とを備える。

(もっと読む)

電界効果トランジスタ

【課題】高移動度と高耐圧とを両立したノーマリオフ型の電界効果トランジスタを提供すること。

【解決手段】III族窒化物半導体からなる電界効果トランジスタであって、基板上に形成されたGaNからなる電子走行層と、前記電子走行層上に形成され、該電子走行層とはバンドギャップエネルギーが異なるAlxGa1−xN(0.01≦x≦0.4)からなり、該電子走行層に到る深さまで形成されたリセス部によって分離した電子供給層と、前記分離した各電子供給層上に前記リセス部を挟んで形成されたソース電極およびドレイン電極と、前記各電子供給層上にわたって前記リセス部内における前記電子走行層の表面を覆うように形成されたゲート絶縁膜と、前記リセス部において前記ゲート絶縁膜上に形成されたゲート電極と、を備え、前記電子供給層の層厚は、5.5nm以上40nm以下である。

(もっと読む)

電界効果トランジスタの製造方法

【課題】デバイスの性能や信頼性を低下させることなく、注入した不純物を活性化することができるIII族半導体材料電界効果トランジスタの製造方法を提供すること。

【解決手段】本発明にかかる電界効果トランジスタの製造方法は、基板やサンプルステージ等を加熱しこれらの熱伝導を用いて半導体層を昇温することによって不純物を活性化させるのではなく、キャリア移動層を形成するGaN層103のバンドギャップエネルギーよりも高いエネルギーを有する波長の紫外線レーザ光Lを照射することによって電界効果トランジスタの構成層に含まれる不純物を活性化させるため、デバイスの性能や信頼性を低下させることなく、注入した不純物を活性化することができる。

(もっと読む)

スイッチング回路

【課題】、接合型電界効果トランジスタ(JFET)の高温動作時のオン抵抗を低減して、高温時の動作特性を改善すること。

【解決手段】出力切替回路34は、温度検出装置33によって検出された温度が所定の閾値温度以上であるとき、第2の駆動回路32に出力切替指示を与える。これにより、第2の駆動回路は、MOSFET35を駆動して、JFET10に立ち上がり電圧(順方向降下電圧)VF以上のゲート電圧VGSが印加され、JFETはバイポーラ動作される。これにより、高温時のJFET10のオン抵抗の増加を抑制できる。

(もっと読む)

半導体装置、及び、半導体装置の製造方法

【課題】高周波信号のスイッチング素子として使用しても、高調波成分が生じ難く、相互変調歪の発生を抑制可能な半導体装置及び同半導体装置の製造方法を提供する。

【解決手段】

半絶縁性基板上に、化合物半導体からなりN型の不純物がドープされたドープ層を有する第1バッファ層を形成し、この第1バッファ層上に、ノンドープの化合物半導体からなる第2バッファ層を形成し、この第2バッファ層上に、トランジスタとして動作する能動層を形成して半導体装置を製造した。また、第1バッファ層を形成する際に、有機金属化合物にN型の不純物を添加した材料を用いてドープ層をエピタキシャル法により形成した。

(もっと読む)

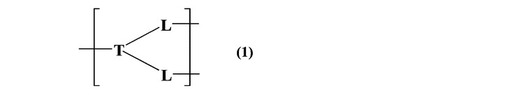

分岐型化合物、これを用いた有機薄膜及び有機薄膜素子

【課題】電荷輸送性に優れる両極性の有機半導体として利用可能な分岐型化合物の提供。

【解決手段】コア部と、該コア部に結合した少なくとも1つの側鎖部と、末端と、から構成される分岐型化合物であって、上記側鎖部の少なくとも1つは、下記一般式(1)で表される繰返し単位が1又は2以上繰り返しており(但し、コア部と結合する前記繰返し単位においては、Tがコア部に結合しており、2以上繰り返す前記繰返し単位においては、LがTに結合している。)、Lは、共役形成単位が複数連結して構成され、上記共役形成単位として少なくとも一つのチエニレン単位を含み、Lの末端(Tと結合していない側のLの末端)に存在する基は、少なくとも2つがアクセプター性の基である、分岐型化合物。

(式中、Lは置換基を有していてもよい2価の有機基を示し、Tは置換基を有していてもよい3価の有機基を示す。)

(もっと読む)

炭化珪素半導体装置の製造方法および炭化珪素半導体装置

【課題】信頼性を向上できる炭化珪素半導体装置の製造方法および炭化珪素半導体装置を提供する。

【解決手段】炭化珪素半導体装置の製造方法は、以下の工程を備えている。まず、主面110aを含む炭化珪素半導体層110が準備される。そして、炭化珪素半導体層110の主面110aにシリコンをドーピングして、炭化珪素半導体層に110おいてシリコンがドーピングされていない領域よりもシリコン濃度の高い高濃度領域115が形成される。そして、高濃度領域115と接する位置に、シリコンと化合物を生成する材料を含む金属層143、144が形成される。そして、金属層143、144を熱処理して、化合物を含む電極が形成される。

(もっと読む)

141 - 160 / 251

[ Back to top ]