Fターム[5F102GS03]の内容

接合型電界効果トランジスタ (42,929) | ゲート電極構造 (2,097) | 断面形状 (702)

Fターム[5F102GS03]の下位に属するFターム

上部が幅広(T字状) (372)

下部が幅広 (4)

左右非対称 (75)

Fターム[5F102GS03]に分類される特許

61 - 80 / 251

半導体装置及びその製造方法

【課題】III-V族窒化物半導体を有する半導体装置において、熱による出力低下を低減する。

【解決手段】半導体装置は、基板101上に設けられ、III-V族窒化物半導体からなるバッファ層102と、バッファ層102上に設けられ、III-V族窒化物半導体からなる第1の半導体層103と、第1の半導体層103上に設けられ、III-V族窒化物半導体からなる第2の半導体層104と、基板101の裏面上に設けられ、接地に接続された裏面電極111と、第2の半導体層104上に互いに離間して設けられたソース電極132及びドレイン電極134と、第2の半導体層104上に設けられたゲート電極136とと、第2の半導体層104、第1の半導体層103、及びバッファ層102を貫通し、少なくとも基板101に達し、ソース電極132と裏面電極111とを電気的に接続させるプラグ109とを備えている。

(もっと読む)

化合物半導体装置

【課題】ゲート電極の端部でのバイアス電界集中が緩和され、且つ動作時のオン抵抗の増大が抑制された化合物半導体装置を提供する。

【解決手段】キャリア供給層22、及びキャリア供給層22との界面近傍において二次元キャリアガス層23が形成されるキャリア走行層21を有する化合物半導体層20と、化合物半導体層20の主面200上に配置されたソース電極3及びドレイン電極4と、ソース電極3とドレイン電極4間で主面200上に配置されたゲート電極5と、ゲート電極5とドレイン電極4間で主面200上方に配置されたフィールドプレート6と、フィールドプレート直下の二次元キャリアガス層が形成される領域内に配置された、上方にフィールドプレート若しくはゲート電極が配置されていない二次元キャリアガス層が形成される領域よりも導電率が低い低導電性領域210とを備える。

(もっと読む)

半導体装置の製造方法

【課題】ドレイン電流コラプスを抑制すること。

【解決手段】窒化物半導体層19上に、ソース電極20、ゲート電極24およびドレイン電極22をそれぞれ形成する工程と、前記窒化物半導体層上に窒化シリコン膜26を形成する工程と、前記ゲート電極と前記ドレイン電極との間の前記窒化シリコン膜の上面をフッ酸を含む溶液を用い処理する工程と、を含む半導体装置の製造方法。

(もっと読む)

電界効果トランジスタ

【課題】III族窒化物半導体からなる電界効果トランジスタにおける高電圧スイッチング時の電流コラプスを効果的に抑制できるようにする。

【解決手段】第1の半導体層103は、少なくともゲート電極106におけるドレイン電極107側の端部の下側の領域において、炭素濃度が1×1017cm−3未満である低炭素濃度領域を有し、基板101の上面から第1の半導体層103及び第2の半導体層104を含むドレイン電極までの半導体層の厚さをd1(μm)とし、低炭素濃度領域の厚さをd2(μm)とし、動作耐圧をVm(V)としたとき、Vm/(110・d1)≦d2<Vm/(110・d1)+0.5の関係を満たし、且つ、緩和状態におけるオン抵抗をRon0とし、動作電圧Vmにおけるオフ状態からオン状態に遷移した100μs後のオン抵抗をRonとしたとき、電流コラプス値の指標とするRonとRon0との比の値が、Ron/Ron0≦3である。

(もっと読む)

半導体装置およびその製造方法

【課題】ドレイン電流コラプスを抑制すること。

【解決手段】窒化物半導体層19上に形成されたソース電極20、ゲート電極24およびドレイン電極22と、前記窒化物半導体層上に接して形成された窒化シリコン膜26と、前記ゲート電極と前記ドレイン電極との間の前記窒化シリコン膜の上面に接して設けられた有機絶縁膜32と、を含む半導体装置。

(もっと読む)

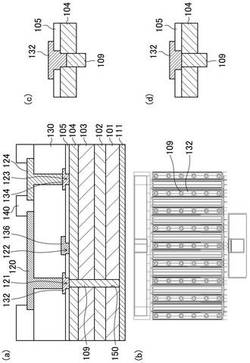

半導体装置

【課題】出力を大きくすることが可能な半導体装置を提供すること。

【解決手段】半導体基板10上に設けられ、ソースパッド12aと、ソースパッド12aと接続された一端から他端に向けて長さが小さくなる階段状の側部12cを有するソースフィンガー12bと、を含むソース電極12と、ドレインパッド14aと、ドレインパッド14aと接続された一端から他端に向けて長さが小さくなり、側部12cと対向する側部14cを有するドレインフィンガー14bと、を含むドレイン電極14と、ソースフィンガー12bの段差12dと、ドレインフィンガー14bの段差14dとの間に屈曲部16cを有し、ソースフィンガー12a及びドレインフィンガー14aに沿って屈曲するゲート電極16と、を具備し、側部12cの形状と側部14cの形状とは、ソースフィンガー12bの他端とドレインフィンガー14bの他端とを結ぶ線分9の中点に対して対称である半導体装置。

(もっと読む)

半導体装置

【課題】高温・高電圧で動作させた場合でも故障の発生を抑制することが可能な半導体装置を提供すること。

【解決手段】本発明は、GaNキャップ層38上のソースフィンガー12と、ソースフィンガーと交互に配置されたドレインフィンガー14と、ソースフィンガーとドレインフィンガーとの間のゲートフィンガー16と、ゲートフィンガーの上面と側面を覆う第1絶縁膜44と、ゲートフィンガーとドレインフィンガーとの間の第1絶縁膜上に設けられたフィールドプレート26と、活性領域18の外側で第1絶縁膜上にフィンガー方向と交差方向に設けられソースフィンガーとその両側のフィールドプレートとを接続するフィールドプレート配線28と、を備え、フィールドプレートと第1絶縁膜の第1段差部46とは100nm以上離れ、フィールドプレート配線と第1絶縁膜の第2段差部48とは100nm以上離れている半導体装置である。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート−ソース間の容量低減及びソース抵抗を低減させ、且つ耐圧向上、高出力化及び高周波化を、容易且つ確実に可能とする量産化に優れた信頼性の高い化合物半導体装置を実現する。

【解決手段】ゲート電極19を形成する際に、4層の電子線レジスト11〜14を用いてゲート開口17を形成し、ゲート開口17内に、キャップ層5の表面との接触面を含む幹状の下方部分19aと下方部分19aから傘状に拡がる上方部分19bとが一体形成されてなり、下方部分19aの接触面がドレイン電極7に比べてソース電極6に偏倚した位置に設けられており、上方部分19bの傘状の下端面のうちソース電極6側の部位がドレイン電極7側の部位よりもキャップ層5の表面からの高さが高いゲート電極19を形成する。

(もっと読む)

電界効果トランジスタ

【課題】歩留りの低下を抑制する。

【解決手段】開口部121.1の形成により、第1の半導体層110の上面のうち、上方に第2の半導体層120が形成されていない部分の少なくとも一部には、絶縁体130.1が形成される。開口部121.1には、絶縁体130.1を覆うようにソース電極S10が形成される。ソース電極S10は、第1の半導体層110と前記第2の半導体層120との界面と接するように形成される。

(もっと読む)

窒化物半導体装置

【課題】活性層の上に電極パッドを形成する場合に生じる問題を解決し、オン抵抗の上昇を抑えた窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、活性領域102Aを有する窒化物半導体層積層体102と、活性領域の上に互いに間隔をおいて形成されたフィンガー状の第1の電極131及び第2の電極132とを備えている。第1の電極の上に接して第1の電極配線151が形成され、第2の電極の上に第2の電極配線152が接して形成されている。第1の電極配線及び第2の電極配線を覆うように第2の絶縁膜が形成され、第2の絶縁膜の上に第1の金属層161が形成されている。第1の金属層は、第2の絶縁膜を介して活性領域の上に形成され、第1の電極配線と接続されている。

(もっと読む)

接合型電界効果トランジスタ

【課題】 従来のJ−FETでは、動作領域内のゲート領域(トップゲート領域)は、動作領域外周に設けられた深いゲート領域を介してのみ、半導体基板(バックゲート領域)と接続していた。このため動作領域の中央と外周ではゲート抵抗にばらつきが生じ、ゲート抵抗の増加によるノイズ電圧の増加や、不均一動作によるゲインの低下が問題であった。

【解決手段】 格子状のゲート領域(トップゲート領域)を有するJ−FETにおいて、行列状にソース領域と交互に配置されていたドレイン領域の一部を深いゲート領域に置き換え、動作領域内にも深いゲート領域を設ける。ドレイン領域を一部省くことで生じるドレイン電流の流れない無効領域をできる限り減らすため、ソース領域が配置されるセルについてドレイン電流が流れない方向のゲート領域を短くする。

(もっと読む)

半導体装置

【課題】2DEGをチャンネルとして用いる半導体装置において、不純物イオンの侵入による悪影響を排除する。

【解決手段】第1の半導体層である電子走行層11上に、第2の半導体層である電子供給層12が形成されている。これらの界面(ヘテロ接合界面)における電子走行層11側に、2次元電子ガス(2DEG)層13が形成される。ソース電極14からドレイン電極15の間の2DEG層13が形成された領域がこの半導体装置10におけるチャンネル領域となる。このチャンネル領域上の絶縁層17上において、第1のフィールドプレート18が形成されている。すなわち、第1のフィールドプレート18は、2つの主電極のうちの一方から他方に達するチャンネル領域上を覆うように形成されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極の電位の位相差を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板と、基板上方に形成された電子走行層と、電子走行層上方に形成された電子供給層と、電子供給層上方に形成された複数のゲート電極5gと、複数のゲート電極5gが接続されたゲートパッド8gと、が設けられている。ゲート電極5gのゲート幅がゲートパッド8gから離間するほど小さくなっている。

(もっと読む)

電界効果トランジスタ

【課題】オン抵抗が低く耐圧および信頼性が高い電界効果トランジスタを提供する。

【解決手段】基板1上に形成されたキャリア走行層3と、前記キャリア走行層上に形成され前記キャリア走行層よりもバンドギャップエネルギーが高いキャリア供給層4a、4bと、前記キャリア供給層から前記キャリア走行層の表面または内部に到る深さまで形成されたリセス部5と、前記キャリア供給層上に形成されたドレイン電極11と、前記リセス部に形成され、前記ドレイン電極側のキャリア供給層と重畳するように延設したゲート電極7と、前記リセス部の底面と前記ゲート電極との間に形成された第1絶縁膜6と、前記ゲート電極と前記ドレイン電極側のキャリア供給層との間に形成され前記第1絶縁膜よりも誘電率が高い第2絶縁膜8aとを備える。

(もっと読む)

電界効果トランジスタ

【課題】電界効果トランジスタにおいて、フィールドプレート終端での高電界の集中を緩和し、もって高耐圧半導体装置として利用可能とする。

【解決手段】本電界効果トランジスタ30は、GaN系エピタキシャル基板32の電子走行層上に、ゲート電極38を挟んで配置されたソース電極34及びドレイン電極36を備え、ゲート電極38の上部に、ドレイン電極36側及びソース電極34側に庇状に突き出したフィールドプレート40が形成され、基板32の表面層とフィールドプレート40との間に誘電体膜46が形成され、誘電体膜46は、フィールドプレート40のドレイン電極36側及びソース電極34側の終端面と面一状態となるように切れ込み、ドレイン電極36側の下端からドレイン電極36に接続するようにドレイン電極36に向かって延びており、且つ、ソース電極34側の下端からソース電極34に接続するようにソース電極34に向かって延びている。

(もっと読む)

電界効果トランジスタ

【課題】電流コラプスが小さく且つ良好な高周波特性を有する電界効果トランジスタを実現できるようにする。

【解決手段】電界効果トランジスタは、基板101の上に形成された窒化物半導体積層体102と、ソース電極105、ドレイン電極106及びゲート電極107と、窒化物半導体積層体102の上に形成された絶縁膜110と、絶縁膜110の上に接して形成され、端部がゲート電極107とドレイン電極106との間に位置するフィールドプレート115とを備えている。絶縁膜110は、第1の膜111と、第1の膜111よりも絶縁耐圧が低い第2の膜112とを含み、ゲート電極117とドレイン電極116との間に形成された薄膜部110aを有している。フィールドプレート115は、薄膜部110aを覆い且つ開口部においてソース電極と接続されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極とソース電極との間のゲート寄生容量成分Cgsを低減することができる半導体装置を提供する。

【解決手段】半導体基板11上に形成された動作層12と、この動作層12の表面上に、互いに離間して形成されたドレイン電極13およびソース電極14と、動作層12の表面上において、ドレイン電極13とソース電極14との間に形成されたゲート電極15と、動作層12の表面上において、ドレイン電極13とソース電極14との間に、ゲート電極15を覆うように形成された表面保護膜19と、表面保護膜19の表面上であって、少なくともゲート電極15のドレイン側端部上を含む位置に形成されたソースフィールドプレート電極20と、ソースフィールドプレート電極20に接続されるとともに、ソース電極14に電気的に接続され、これらの電極20、14のよりも狭い幅で表面保護膜19上に形成された複数の配線21を具備する。

(もっと読む)

窒化物系半導体装置

【課題】MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させた、窒化物系半導体装置を提供することを目的とする。

【解決手段】ドレイン電極26とゲート電極28との間に設けられたSBD金属電極30がAlGaN層20とショットキー接合されている。また、SBD金属電極30とソース電極24とが接続されており、電気的に短絡している。これにより、ゲート電極28にオフ信号が入ると、MOSFET部32がオフ状態となり、MOSFET部32のドレイン側の電圧がドレイン電極26の電圧値と近くなる。ドレイン電極26の電圧が上昇すると、SBD金属電極30の電圧値が、MOSFET部32のドレイン側の電圧値よりも低くなるため、SBD金属電極30によってMOSFET部32のドレイン側とドレイン電極26とが電気的に切断される。

(もっと読む)

III族窒化物系高電子移動度トランジスタを含む低雑音増幅器

【課題】高い入力電力耐性と、低い雑音指数の両者を達成する低雑音増幅器を提供すること。

【解決手段】低雑音増幅器は、第一のIII族窒化物系トランジスタと、第一のIII族窒化物系トランジスタに結合された第二のIII族窒化物系トランジスタとを含んでいる。第一のIII族窒化物系トランジスタは、入力信号に対する第一増幅段を提供するように構成され、第二のIII族窒化物系トランジスタは、入力信号に対する第二増幅段を提供するように構成される。

(もっと読む)

窒化物半導体素子

【課題】ノーマリオフ特性を有する低オン抵抗で高耐圧の窒化物半導体素子を提供する。

【解決手段】基板上に設けられた第1導電型の窒化物半導体からなる第1半導体層5と、前記第1半導体層の上に設けられ、前記第1半導体層のシートキャリア濃度と同量のシートキャリア濃度を有する第2導電型の窒化物半導体からなる第2半導体層6と、を備える。前記第2半導体層の上には、前記第2半導体層よりも禁制帯幅が広い窒化物半導体からなる第3半導体層7が設けられる。前記第2半導体層に電気的に接続された第1主電極10と、前記第1主電極と離間して設けられ、前記第2半導体層に電気的に接続された第2主電極20と、をさらに備え、前記第1主電極と前記第2主電極との間において、前記第3半導体層および前記第2半導体層を貫通して前記第1半導体層に達する第1のトレンチの内部に絶縁膜33を介して設けられた制御電極30を備える。

(もっと読む)

61 - 80 / 251

[ Back to top ]