Fターム[5F103PP02]の内容

半導体装置を構成する物質の物理的析出 (6,900) | 前処理・後処理 (421) | 清浄化処理を行うもの (58) | サーマルクリーニングによるもの (30)

Fターム[5F103PP02]に分類される特許

1 - 20 / 30

三次元微細加工基板

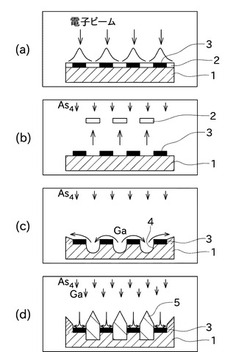

【課題】高密度かつ複雑な三次元微細構造の加工を可能にする。

【解決手段】基板上の三次元微細構造は、以下の方法で作製される。第1工程では、真空中でIII−V族化合物半導体基板1の表面に電子ビームを照射することにより、当該基板1の表面の自然酸化膜2をIII族酸化物3に置換させ、改質マスク部3を周期的に形成する。第2工程では、真空中で前記基板1を昇温させることにより、前記改質マスク部3以外の部分の前記自然酸化膜2を脱離させて基板表面を露出させる。第3工程では、真空にV族原料を供給した環境下で前記基板1を所定温度で加熱することで、前記基板表面の露出部分からIII族原子を優先的に剥離させて前記改質マスク部3上をホッピングさせ、当該露出部分に窪み4を形成する。第4工程では、固体成長原料を用いた分子線エピタキシャル成長法を行うことで、前記窪み4の部分にIII−V族化合物半導体結晶5を選択成長させる。

(もっと読む)

多層膜構造体及びその形成方法

【課題】新規な多層膜構造体及びその形成方法を提供すること。

【解決手段】半導体素子用の多層膜構造体の形成方法であって、シリコンを含む基板上に、ゲルマニウム錫混晶からなる半導体層を形成する半導体層形成工程と、前記半導体層上に表面保護層を形成する表面保護層形成工程と、前記半導体層に熱処理を施すことにより、前記ゲルマニウム錫混晶と前記シリコンを含む基板との固相反応を進め、シリコンゲルマニウム錫混晶からなる半導体歪印加層を形成する半導体歪印加層形成工程と、前記表面保護層を除去する除去工程と、前記半導体歪印加層の上方に、前記除去工程後に、歪半導体層を積層する積層工程とを含むことを特徴とする多層膜構造体の形成方法。

(もっと読む)

窒化物半導体用基板および窒化物半導体用基板の製造方法

【課題】大型化が比較的容易で、比較的安価な窒化物半導体用基板を提供する。

【解決手段】基材120と、該基材120の上部に設置されたバッファ層160と、該バッファ層160の上部に設置された窒化物半導体層180とを有する窒化物半導体用基板100であって、前記基材120は、石英で構成され、前記バッファ層160は、ガリウム(Ga)および/またはアルミニウム(Al)の窒化物を含み、前記窒化物半導体層180は、ガリウム(Ga)および/またはアルミニウム(Al)を含む窒化物半導体で構成され、前記基材120と前記バッファ層160の間には、応力緩和層125が設置され、該応力緩和層125は、前記基材120に近い側のアモルファス層130および前記基材120に遠い側の結晶化層150を有し、または前記基材120に遠い側に結晶成分を含むアモルファス層を有し、前記応力緩和層125は、窒化珪素または酸窒化珪素を含む。

(もっと読む)

酸化亜鉛系基板の処理方法及び成長層付き基板

【目的】

原子レベルで平坦な表面を有し、シリカやシリケート等の表面付着のない基板処理方法を提供する。

【解決手段】

EDTAキレート化合物とEDAとの混合溶液を用いて化合物単結晶基板の加工変質層をエッチングして除去する第1のエッチング工程と、第1のエッチング工程後、バッファードフッ酸(BHF)によりエッチングを行う第2のエッチング工程と、を有する。

(もっと読む)

記憶素子、記憶装置、信号処理回路、記憶素子の駆動方法

【課題】電源電圧の供給が停止した後もデータ保持可能な記憶素子を提供する。消費電力の低減可能な信号処理回路を提供する。

【解決手段】クロック信号に同期してデータを保持する記憶素子において、酸化物半導体層にチャネルが形成されるトランジスタ及び容量素子を用いることより、電源電圧の供給が停止した間もデータ保持ができる。ここで、電源電圧の供給を停止する前に、クロック信号のレベルを一定に保った状態で当該トランジスタをオフ状態とすることにより、データを正確に容量素子に保持させることができる。また、このような記憶素子を、CPU、メモリ、及び周辺制御装置のそれぞれに用いることによって、CPUを用いたシステム全体で、電源電圧の供給停止を可能とし、当該システム全体の消費電力を削減することができる。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】電界効果型トランジスタに関する新規な製造方法を提供する。

【解決手段】基板上に、非晶質酸化物層を形成する前に、基板表面にオゾン雰囲気中で紫外線を照射したり、基板表面にプラズマを照射したり、あるいは基板表面を過酸化水素を含有する薬液により洗浄する。または、非晶質酸化物を含み構成される活性層を形成する工程をオゾンガス、窒素酸化物ガス等の少なくともいずれかを含む雰囲気中で行う。または、基板上に、非晶質酸化物層を形成する後に、非晶質酸化物層の成膜温度よりも高い温度で熱処理する工程を含む。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層と該酸化物半導体層と接する絶縁膜との界面状態が良好なトランジスタ及びその作製方法を提供することを課題の一つとする。

【解決手段】酸化物半導体層と該酸化物半導体層と接する絶縁膜(ゲート絶縁層)との界面状態を良好とするために、酸化物半導体層の界面近傍に窒素を添加する。具体的には酸化物半導体層に窒素の濃度勾配を作り、窒素を多く含む領域をゲート絶縁層との界面に設ける。この窒素の添加によって、酸化物半導体層の界面近傍に結晶性の高い領域を形成でき、安定した界面状態を得ることができる。

(もっと読む)

III族窒化物半導体光素子、III族窒化物半導体光素子を形成する方法、III族窒化物半導体膜を成長する方法及びエピタキシャル基板

【課題】p型III族窒化物半導体の電気特性を向上できるIII族窒化物半導体光素子を提供する。

【解決手段】窒化ガリウム系半導体領域15及び窒化ガリウム系半導体領域19は、基板13の主面13a上に設けられる。窒化ガリウム系半導体領域19は、p型ドーパントとしてマグネシウムを含むIII族窒化物半導体膜21を有しており、III族窒化物半導体膜21は、III族構成元素としてアルミニウムを含む。III族窒化物半導体膜21の酸素濃度は、1.0×1017cm−3以上の範囲にあり、III族窒化物半導体膜21の酸素濃度は、1.5×1018cm−3以下の範囲にある。また、III族窒化物半導体膜21の水素濃度は1.0×1017cm−3以上の範囲にあり、III族窒化物半導体膜21の水素濃度は1.5×1018cm−3以下の範囲にある。

(もっと読む)

電子装置とその作製方法およびスパッタリングターゲット

【課題】絶縁性酸化物の量産性を高めこと、また、そのような絶縁性酸化物を用いた半導体装置に安定した電気的特性を付与すること、信頼性の高い半導体装置を作製する。

【解決手段】亜鉛のように400〜700℃で加熱した際にガリウムよりも揮発しやすい材料を酸化ガリウムに添加したターゲットを用いて、DCスパッタリング、パルスDCスパッタリング等の大きな基板に適用できる量産性の高いスパッタリング方法で成膜し、これを400〜700℃で加熱することにより、添加された材料を膜の表面近傍に偏析させる。膜のその他の部分は添加された材料の濃度が低下し、十分な絶縁性を呈するため、半導体装置のゲート絶縁物等に利用できる。

(もっと読む)

ZnO系半導体装置及びその製造方法

【課題】ZnO系半導体の新規なn型ドーピング技術に係るZnO系半導体装置及びその製造方法を提供する。

【解決手段】ZnO系半導体装置の製造方法は、基板を準備する工程と、基板上方に、Zn、O、及びNを供給するとともに、必要に応じて、ZnOに添加することによりバンドギャップを変化させる元素を供給し、Nをドープすることにより、Nをドープしない場合に比べてn型キャリア濃度が増したn型伝導性を示すZnO系半導体層を形成する工程とを有する。

(もっと読む)

透明な薄膜を堆積し、パターン構造を直接堆積する方法及び装置

【課題】透明な薄膜を堆積し、パターン構造を直接堆積する方法を提供する。

【解決手段】透明な薄膜を堆積し、パターン構造を直接堆積する方法であって、パルスレーザ源を提供し、前記パルスレーザ源が出射するレーザ1を透明な基板3を介してターゲット5上に集光させて、前記レーザのエネルギーを使用して前記ターゲットの部分を融除又は蒸発させ、前記基板を前記ターゲットに対して並進運動させる、前記融除又は蒸発された前記ターゲットの材料が前記基板上に堆積し、前記基板上にパターン構造を形成できるようにする。

(もっと読む)

シリコン基板上にSi3N4へテロエピタキシャルバッファ層を有する窒化シリコン基板の作製方法および装置

【課題】シリコン基板の全表面にわたって均一な厚みを有しかつ品質の安定したSi3N4へテロエピタキシャルバッファ層を容易にかつ安価に作製する作成方法及び装置を提供する。

【解決手段】シリコン基板を表面再構成可能に清浄化処理し、次いで、前記清浄化処理したシリコン基板上に、誘導結合プラズマ方式のRF(高周波)高輝度(HB)放電により生成した解離窒素原子フラックスおよび励起窒素分子フラックスを照射して表面界面反応によりSi3N4単結晶膜をエピタキシャル成長させること。

(もっと読む)

ZnO系半導体素子の製造方法及びZnO系半導体素子

【課題】例えば500℃程度以下の低温成長でも、ZnO層の表面平坦性の低下が抑制されたZnO系半導体素子の製造方法を提供する。

【解決手段】ZnO系半導体素子の製造方法は、基板を準備する工程と、無電極放電管にOとNを含むガスを導入し、放電して第1のビーム3aを発生させる工程と、基板11の上方に、少なくともZnを供給するとともに、無電極放電管から第1のビーム3aを供給して、n型ZnO系半導体層を成長させる工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】

成長中断による、Alを含むIII-V族化合物半導体層への酸素の取り込みを抑制した半導体装置を提供すること。

【解決手段】

Alを構成元素として含む第1のIII-V族化合物半導体によって半導体基板上に形成された第1の半導体層と、厚さが2原子層以上8原子層以下のAlを構成元素として含まない第2のIII-V族化合物半導体で形成され、且つ前記第1の半導体層の上面又は前記第1の半導体層の内部に配置された表面保護層とを有する半導体積層構造と、第3のIII-V族化合物半導体で形成され、且つ前記半導体積層構造の上面に形成された第2の半導体層を具備すること。

(もっと読む)

薄膜形成装置および薄膜形成方法

【課題】不純物のドープ量を容易に制御して添加できるプラズマ援用反応性薄膜形成装置を提供する。

【解決手段】プラズマ発生用コイル4を、薄膜にドープする元素からなる物質、またはその元素を含む物質で一部または全体が構成されるか被覆されたものとする。そのプラズマ発生用コイル4によってチャンバ10内にプラズマを発生させ、蒸発源のルツボ6によって蒸発される原料の元素と気体導入口7から導入される気体の元素とがプラズマ雰囲気中で活性化し、前記プラズマ発生用コイル4の表面からスパッタリングされて飛び出す上記物質(例えばCu)の元素とともに基板2の表面において反応し、該物質の元素をドープした薄膜を成膜する。

(もっと読む)

半導体基板

【課題】従来に比べ極めて薄いバッファ層を用いて、工業的に安定でかつ低コストで、基板と格子定数の異なる良質の薄膜を形成した半導体基板を提供すること。

【解決手段】基板1は、格子定数xを有するものである。第1の半導体層2は、基板1上に形成され、格子定数yを有し、少なくともSbを含んでいる。第2の半導体層3は、第1の半導体層2上に形成され、格子定数yからzまで格子定数を段階的又は連続的に変化させものである。第3の半導体層4は、第2の半導体層3上に形成され、格子定数zを有するものある。これらの格子定数の関係は、x<z<yの関係を有している。基板1上に格子定数の異なる薄膜を形成する際に、まずSbを含む半導体を形成し、その上層に格子定数を変化させるためのバッファ層を形成することで、従来に比べ薄いバッファ層で結晶欠陥のない薄膜形成が可能となる。

(もっと読む)

窒化ガリウム系半導体デバイスのための基板

【課題】窒化ガリウム系半導体デバイスのための基板を提供する。

【解決手段】基板11aは、ナノコラム領域13と、窒化ガリウム半導体膜15と、支持基体17とを備える。ナノコラム領域13は、窒化ガリウムからなる複数のナノコラム19を有する。窒化ガリウム半導体膜15は、複数のナノコラム19の一端19aの各々に接続されている。窒化ガリウム半導体膜15の導電型は、ナノコラム領域13の窒化ガリウムの導電型と同じである。また、窒化ガリウム半導体膜15は主面15aを有する。主面15a上には、窒化ガリウム系半導体デバイスを形成するための半導体膜が堆積される。支持基体17は、複数のナノコラム19の他端19bを支持しており、また窒化ガリウムとは異なる材料からなる支持体21を含む。

(もっと読む)

窒化物系III−V族化合物半導体装置の製造方法

【課題】バッファ層上の窒化物系III−V族化合物半導体の転位密度が小さくて優れた電気的特性を有する窒化物系III−V族化合物半導体装置の製造方法を提供する。

【解決手段】SiC基板71上にAlNのバッファ層72を形成した後、AlNのバッファ層72上にGaN層を成長させる。続いて、AlNのバッファ層72と上記GaN層の界面近傍に、Gaイオンを打ち込んで、AlNのバッファ層72と上記GaN層の界面付近にアモルファスの層74を形成する。その後、基板温度を800℃まで上げてアモルファスの層74の上の上記GaN層を再結晶化して、転位が少ないGaN層75層を形成する。

(もっと読む)

III族窒化物薄膜の形成方法

【課題】 サファイアC面基板上に成長するGaN系III族窒化物薄膜の極性を(0001)に制御することにより、従来よりも光学的、電気的特性に優れた薄膜を提供すること。

【解決手段】 サファイアC面基板上に、窒素源として窒素プラズマを、またIII族源としてGaを主成分とする金属を用いて分子線エピタキシーによりGaN系III族窒化物薄膜をエピタキシャル成長させるに際し、金属Gaとして、その強度(フラックス)が1×1013コ/cm2s〜1×1015コ/cm2sであるものを用い、該GaN系III族窒化物薄膜の成長初期に金属Inを、照射する金属Gaの強度より1〜2桁低い強度で、照射することにより、成長する膜の極性を(0001)に制御する。

(もっと読む)

III族窒化物半導体の製造方法、III族窒化物半導体発光素子の製造方法、及びIII族窒化物半導体発光素子、並びにランプ

【課題】良好な結晶性を有するIII族窒化物半導体の結晶を、スパッタ法を用いて高い成膜速度で効率良く形成することが可能なIII族窒化物半導体の製造方法、及びIII族窒化物半導体発光素子の製造方法を提供する。

【解決手段】チャンバ内に基板及びGa元素を含有するターゲットを配置し、少なくとも、基板上にドナー不純物が添加された単結晶のIII族窒化物半導体を反応性スパッタ法によって形成するIII族窒化物半導体の製造方法であり、基板の温度を温度T1としてIII族窒化物半導体を成膜する第1スパッタ工程と、基板の温度を温度T1よりも低い温度T2に降温してIII族窒化物半導体の成膜を続ける第2スパッタ工程とが備えられた方法である。

(もっと読む)

1 - 20 / 30

[ Back to top ]