Fターム[5F110BB08]の内容

Fターム[5F110BB08]に分類される特許

141 - 160 / 412

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタ160と、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成される。

(もっと読む)

半導体装置

【課題】LSIやCPUやメモリに用いるトランジスタのリーク電流及び寄生容量を低減することを課題の一とする。

【解決手段】半導体基板上において、酸化物半導体中で電子供与体(ドナー)となる不純物を除去することで、真性又は実質的に真性な半導体であって、シリコン半導体よりもエネルギーギャップが大きい酸化物半導体でチャネル領域が形成されるトランジスタを用い、LSIやCPUやメモリなどの半導体集積回路を作製する。半導体基板上に形成され、水素濃度が十分に低減されて高純度化された酸化物半導体層を用いるトランジスタは、リーク電流による消費電力の少ない半導体装置を実現できる。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】複数の記憶素子が直列に接続され、複数の記憶素子の一は、第1〜第3のゲート電極、第1〜第3のソース電極、および第1〜第3のドレイン電極を有する第1〜第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含んで構成され、第1のゲート電極と、第2のソース電極または第2のドレイン電極の一方とは、電気的に接続され、第1の配線と、第1のソース電極と、第3のソース電極とは、電気的に接続され、第2の配線と、第1のドレイン電極と、第3のドレイン電極とは、電気的に接続され、第3の配線と、第2のソース電極または第2のドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のゲート電極とは、電気的に接続され、第5の配線と、第3のゲート電極とは電気的に接続された半導体装置。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】RTSノイズを低減することが可能な絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】チャネル領域として機能するp型の半導体層11と、チャネル領域を少なくとも囲み、活性領域21Bを定義する素子分離絶縁膜21と、活性領域21Bの一方に設けられたn型の第1主電極領域12と、活性領域21Bの他方に設けられたn型の第2主電極領域13と、活性領域21B上に設けられたゲート絶縁膜22と、ゲート絶縁膜22上において、第1主電極領域12と第2主電極領域13との間のチャネル領域を流れるキャリアの流路に直交する方向に伸延するゲート電極24とを備え、チャネル領域への前記キャリアの注入口が素子分離絶縁膜21から離間して設けられている。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】半導体材料を含む基板に設けられたチャネル形成領域と、チャネル形成領域を挟むように設けられた不純物領域と、チャネル形成領域上の第1のゲート絶縁層と、第1のゲート絶縁層上の第1のゲート電極と、不純物領域と電気的に接続する第1のソース電極および第1のドレイン電極と、を有する第1のトランジスタと、半導体材料を含む基板上の第2のゲート電極と、第2のゲート電極上の第2のゲート絶縁層と、第2のゲート絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続する第2のソース電極および第2のドレイン電極と、を有する第2のトランジスタと、を有する半導体装置である。

(もっと読む)

半導体記憶装置およびその制御方法

【課題】SOI構造の半導体記憶装置に電気的に書換え可能な不揮発性メモリを形成する手段を提供する。

【解決手段】第1の拡散層16、第2の拡散層17、前記第1および第2の拡散層間に配置された第3の拡散層、および第4の拡散層21と、前記第1および第2の拡散層とそれぞれ一部がオーバーラップし、前記第3の拡散層上から前記第4の拡散層にかけて延在するフローティングゲート電極13と、前記第1の拡散層および前記第3の拡散層に、共通の第1の電位を与える第1の制御線31と、前記第2の拡散層に、第2の電位を与える第2の制御線37と、前記第4の拡散層に、第3の電位を与える第3の制御線33と、を備え、前記フローティングゲート電極が前記第4の拡散層とオーバーラップした面積が、前記第2の拡散層とオーバーラップした面積よりも大きく、前記第1および第3の拡散層とオーバーラップした合計の面積よりも小さい。

(もっと読む)

酸化物半導体を用いた薄膜トランジスタおよびその製造方法

【課題】オフ特性およびキャリア移動度に優れた、高品質の、酸化物半導体を用いた薄膜トランジスタおよびその製造方法を提供する。

【解決手段】本発明の薄膜トランジスタは、ソース電極と、ドレイン電極と、ゲート電極と、ゲート絶縁膜と、酸化物半導体からなる活性層とを備えてなる。そして、活性層とソース電極の間および活性層とドレイン電極の間には、炭素製のバッファ層が設けられてなる。

(もっと読む)

無線通信機能を有する半導体装置

【課題】無線通信機能を有する半導体装置の低消費電力化、通信距離の拡大を図る。

【解決手段】メモリ部と、論理部と、メモリ部及び論理部間を電気的に接続する複数の信号線と、を備え、半導体装置及び通信装置間の転送レートをα[bps]、論理部で生成される第1のクロック周波数をKα[Hz](Kは1以上の整数)、複数の信号線のうち読み出し用信号線をn本(nは2以上の整数)、論理部で生成される第2のクロック周波数をLα/n[Hz](Lは、L/n<Kを満たす任意の整数)とした場合、メモリ部に格納されたデータを論理部へ読み出す場合は、第2のクロック周波数Lα/n[Hz]を用いて、n本の読み出し用信号線を介して行う。

(もっと読む)

トランジスタ,面状素子およびこれらの製造方法

【課題】トランジスタを比較的低温で製造する。

【解決手段】下部ゲート絶縁膜44をコントロールゲート42を構成する金属(アルミニウム)の酸化物により形成された下部酸化物層44aと自己組織化単分子膜により形成された下部SAM層44bとにより構成し、上部ゲート絶縁膜48をフローティングゲート46を構成する金属(アルミニウム)の酸化物により形成された上部酸化物層48aと自己組織化単分子膜により形成された上部SAM層48bとにより構成した。これにより、メモリセル40を比較的低温で製造することができる。

(もっと読む)

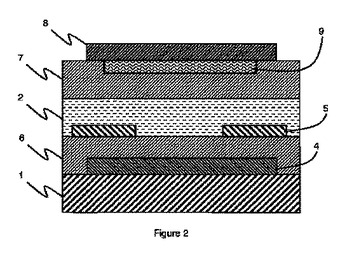

有機デュアルゲートメモリおよびその製造方法

有機メモリデバイスは、第1のゲート電極(4)と、第1のゲート誘電体(6)と、有機半導体材料(2)と、第2のゲート誘電体(7)と、第2のゲート電極(8)とを備えるデュアルゲートトランジスタである。ソース・ドレイン電極(5)が、有機半導体材料(2)中に配置されるとともに、電極間表面を規定する。捕捉領域(9)が、有機半導体材料(2)とゲート電極(4,8)のうちの一方との間に配置されるとともに、ゲート電極(4,8)のうちの一方または有機半導体材料(2)と電気的に接触する。捕捉領域(9)は少なくとも電極間表面と対向する。  (もっと読む)

(もっと読む)

表示装置、および電子機器

【課題】画素にメモリを有する画素を備えた表示装置を提供する。

【解決手段】画素に、少なくとも、表示素子、容量素子、インバータおよびスイッチを設ける。容量素子に保持された信号と、インバータから出力される信号とを用いて、スイッチを制御することにより、表示素子に電圧が供給されるようにする。インバータおよびスイッチを同じ極性を持つトランジスタで構成することができる。また、画素を構成する半導体層を透光性を有する材料で形成してもよい。また、ゲート電極、ドレイン電極および容量電極を透光性を有する導電層を用いて形成してもよい。このように透光性材料で画素を形成することで、メモリが配置された画素を有していながら、その表示装置を透過型にすることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】FINFETにおいて、寄生抵抗の改善を図ることができる技術を提供する。

【解決手段】本発明におけるFINFETでは、サイドウォールSWを積層膜から形成している。具体的に、サイドウォールSWは、酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から構成されている。一方、フィンFIN1の側壁には、サイドウォールSWが形成されていない。このように本発明では、ゲート電極G1の側壁にサイドウォールSWを形成し、かつ、フィンFIN1の側壁にサイドウォールSWを形成しない。

(もっと読む)

不揮発性メモリセル及びその製造方法

【課題】同一の基板上に形成されたメモリトランジスタ及び駆動トランジスタを備える透明不揮発性メモリセル及びその製造方法を提供する。

【解決手段】本発明による不揮発性メモリセルは、基板上に形成された半導体膜、バッファー膜、有機強誘電体膜及びゲート電極を含むメモリトランジスタと;前記基板上に形成された前記半導体膜、前記バッファー膜、ゲート絶縁膜及び前記ゲート電極を含む駆動トランジスタと;を備える。本発明によれば、同一の基板上に形成されたメモリトランジスタ及び駆動トランジスタを備え、可視光領域で透明な不揮発性メモリセルを提供することができる。

(もっと読む)

記憶装置及びデータ書き込み方法

【課題】メモリを他の機能回路と同一の基板上に作製した時にも、メモリのための仕様の限定を生じず、生産性を向上し、使用者にとって使いやすく、安価な記憶装置を提供する。

【解決手段】絶縁表面上に、第1乃至第5の領域を有する半導体膜と、絶縁膜と、第1の電極と、第2の電極とを含むメモリセルを有し、第2の領域は第1の領域と第3の領域の間に設けられ、第4の領域は第3の領域と第5の領域の間に設けられ、第1の電極は絶縁膜を介して第2の領域と重なって設けられ、第2の電極は絶縁膜を介して第4の領域と重なって設けられ、メモリセルは、書き込み処理時に第1の領域及び第5の領域のうち少なくとも一方の領域と、第1の電極及び第2の電極との間に電圧を印加して第2の領域及び第4の領域のうち少なくとも一方の領域の半導体膜を絶縁状態に変化させる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の仕事関数で本質的にしきい値電圧が決定されるFINFETにおいて、ゲート電極の材料を変えることなく、FINFETのしきい値電圧を調整することができる技術を提供する。

【解決手段】基板層1Sと、基板層1S上に形成された埋め込み絶縁層BOXと、埋め込み絶縁層BOX上に形成されたシリコン層からなるSOI基板上にFINFETが形成されている。このとき、基板層1S内に埋め込み絶縁層BOXと接触する第1半導体領域FSR1が形成されている。そして、SOI基板のシリコン層を加工してフィンFIN1が形成されている。このとき、フィンFIN1のフィン幅に対するフィン高さの比が1以上2以下になるように形成されており、かつ、第1半導体領域FSR1に電圧を印加することができるようになっている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中に含まれる不純物の拡散を防止することができ、さらに、ゲート絶縁膜の信頼性及びホットキャリア耐性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】N型シリコン基板1上にゲート酸化膜36およびP+型ゲート電極35を形成する。P+型ゲート電極35の両側にソース/ドレイン領域6を形成する。ゲート酸化膜36およびP+型ゲート電極35中には窒素がドープされ、窒素ドーピング領域30が形成される。

(もっと読む)

SOI基板の作製方法

【課題】単結晶シリコン基板よりも大面積な基板に、均一な質を有する複数の単結晶半導体層を貼り付けたSOI基板の作製方法を提供することを課題とする。

【解決手段】熱処理において、ベース基板支持及び単結晶半導体基板保持のトレイとして、凹部の底が深く、ベース基板に貼り付けられた単結晶半導体基板と接触しないトレイを用いて、単結晶半導体基板の熱分布の均一化を図る。また、該トレイの各々の凹部の間にベース基板支持部を設けることによって、該トレイとベース基板との接触面積を低減する。以上より、単結晶半導体基板から単結晶半導体層を分離する熱処理の際、単結晶半導体基板及びベース基板の熱分布が均一になるようにする。

(もっと読む)

薄膜トランジスタ及び半導体メモリセル

【課題】バックゲート電極へのリーク電流を抑えた薄膜トランジスタ(MFSFET)を提供することにある。

【解決手段】基板11上に形成されたゲート電極12と、ゲート電極12上に形成された強誘電体膜からなるゲート絶縁膜13と、ゲート絶縁膜13上に形成されたオーミック電極からなるソース・ドレイン電極15s、15dと、ソース・ドレイン電極15s、15d間のゲート絶縁膜13上に形成された半導体膜14とを備え、ゲート絶縁膜13と半導体膜14との界面をチャネルとする。

(もっと読む)

パターン形成方法、薄膜トランジスタ及びその作製方法

【課題】フォトリソグラフィ法に用いるフォトマスクの枚数を少なくする。

【解決手段】第1の膜を形成し、該第1の膜上にフォトリソグラフィ法により第1のレジストマスクを形成し、第1のレジストマスクを用いて所定のパターンを有する第1の層を形成し、第1のレジストマスクを除去し、第2の膜を形成し、該第2の膜上にフォトリソグラフィ法により第1のレジストマスクと同一のフォトマスクにより第2のレジストマスクを形成し、該第2のレジストマスクを縮小して第3のレジストマスクを形成し、第3のレジストマスクを用いて所定のパターンを有する第2の層を形成する。

(もっと読む)

半導体メモリセルおよびその製造方法

【課題】スイッチング特性に優れ、セルサイズの小さい半導体メモリセルを提供することにある。

【解決手段】ゲート絶縁膜が強誘電体膜4で構成されたMFSFET21からなるメモリ素子と、ゲート絶縁膜が常誘電体膜9で構成されたMISFET22からなる選択スイッチング素子とを備えた半導体メモリセル20であって、MFSFETの第1のゲート電極3は、基板1上の結晶性絶縁膜2表面に形成された結晶性導電膜3からなり、強誘電体膜4は、第1のゲート電極3を覆って結晶性絶縁膜2上に形成され、常誘電体膜9は、半導体膜5を介して強誘電体膜4上に形成され、MISFET22の第2のゲート電極10は、常誘電体膜9上に形成されている。

(もっと読む)

141 - 160 / 412

[ Back to top ]