Fターム[5F110BB20]の内容

Fターム[5F110BB20]に分類される特許

141 - 160 / 665

フレキシブルデバイス用基板、フレキシブルデバイス用薄膜トランジスタ基板およびフレキシブルデバイス

【課題】本発明は、金属層とポリイミド層とが積層された可撓性を有する基板上にTFTを作製した際に、金属箔表面の凹凸によるTFTの電気的性能の劣化を抑制することができ、TFTの剥離やクラックを抑制することができるフレキシブルデバイス用基板を提供することを主目的とする。

【解決手段】本発明は、金属箔と、上記金属箔上に形成され、ポリイミドを含む平坦化層と、上記平坦化層上に形成され、無機化合物を含む密着層とを有することを特徴とするフレキシブルデバイス用基板を提供することにより、上記目的を達成する。

(もっと読む)

半導体装置

【課題】半導体装置の歩留まりを向上させること若しくは製造コストを低減すること又は集積回路の面積を低減する半導体装置を提供する。

【解決手段】半導体装置が有するメモリ素子10のメモリ層12及び抵抗素子20の抵抗層22が同一材料によって構成される。そのため、メモリ層12と、抵抗層22とを同一工程によって形成することで、半導体装置の作製工程数を低減することができる。結果として、半導体装置の歩留まりを向上させること又は製造コストを低減することができる。また、半導体装置は、抵抗値の高い抵抗成分を備えた抵抗素子20を有する。そのため、半導体装置が有する集積回路の面積を低減することができる。

(もっと読む)

薄膜集積回路装置及びその製造方法

【課題】商品の意匠性を低下させないICタグ等を形成することができる薄膜集積回路装置を提供する。

【解決手段】透明基板1上に少なくともTFT素子Aと容量素子B及び/又は抵抗素子Cとを有し、TFT素子Aを構成するゲート電極2A、ゲート絶縁膜3A、半導体膜4、ソース電極6S及びドレイン電極6Dがいずれも透明膜であり、容量素子Cを構成する誘電体膜3Bが前記ゲート絶縁膜3Aと同一材料であり、その誘電体膜3Bを積層方向Zに挟む一方の第1電極2Bが前記ゲート電極2Aと同一材料で、他方の第2電極6Bが前記ソース電極6S及びドレイン電極6Dと同一材料であり、抵抗素子Cを構成する抵抗体膜4Cが前記半導体膜4と同一材料であり、その抵抗体膜4Cを面内方向Xに挟む第3電極6Eと第4電極6Fが前記ソース電極6S及びドレイン電極6Fと同一材料であるようにした薄膜集積回路装置10Aを提供する。

(もっと読む)

半導体装置の作製方法

【課題】半導体膜への不純物の拡散を抑えつつ、歩留まりの低下を抑えることができるSOI基板の作製方法を提供することを、目的の一とする。

【解決手段】半導体基板の表面を熱酸化させることで、酸化膜が形成された半導体基板を形成する。そして、窒素原子を有するガス雰囲気下においてプラズマを発生させることにより、上記酸化膜の一部をプラズマ窒化させ、酸化膜上に窒素原子を含む絶縁膜が形成された半導体基板を得る。そして、窒素原子を含む絶縁膜とガラス基板を接合させた後、半導体基板を分離することで、ガラス基板上に窒素原子を含む絶縁膜、酸化膜、薄膜の半導体膜が順に積層されたSOI基板を形成する。

(もっと読む)

薄膜トランジスタ及びその製造方法並びに画像表示装置

【課題】製造コストを低減することができ、かつ、歩留まりの高い薄膜トランジスタを提供することにある。

【解決手段】本発明の実施の形態1に係る薄膜トランジスタの製造方法は、絶縁基板10の上に少なくともゲート電極11、ゲート絶縁層12、半導体層13、ソース電極14、ドレイン電極15及び保護層16を具備する薄膜トランジスタの製造方法であって、保護層16が真空紫外光CVD法により形成されるものであり、ゲート絶縁層12の上の全面に保護層16となる膜を成膜する工程と、保護層と16なる膜をパターニングなしにエッチングしソース電極14とドレイン電極15の表面を露出させ保護層16のパターンを形成する工程と、を具備する。

(もっと読む)

SOI基板の作製方法及び半導体装置の作製方法

【課題】平坦性を確保しつつ、結晶性の高い半導体膜を有する、SOI基板の作製方法を提供することを、目的の一とする。

【解決手段】分離により絶縁膜上に単結晶の半導体膜を形成した後、該半導体膜の表面に存在する自然酸化膜を除去し、半導体膜に対して第1のレーザ光の照射を行う。第1のレーザ光の照射は、希ガス雰囲気下、窒素雰囲気下または減圧雰囲気下にて、半導体膜の任意の一点におけるレーザ光のショット数を7以上、より好ましくは10以上100以下とする。そして、第1のレーザ光の照射を行った後、半導体膜に対して第2のレーザ光の照射を行う。第2のレーザ光の照射は、希ガス雰囲気下、窒素雰囲気下または減圧雰囲気下にて、半導体膜の任意の一点におけるレーザ光のショット数を0より大きく2以下とする。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法、表示装置、および電子機器

【課題】有機半導体層とソース電極/ドレイン電極との間のコンタクト抵抗を図りながらも微細化プロセスの適用が可能でかつ良好な特性を有する薄膜トランジスタを提供する。

【解決手段】トップコンタクト・ボトムゲート構造の薄膜トランジスタにおいて、有機半導体層17とソース電極21s/ドレイン電極21dとの間に、有機半導体材料と共にアクセプタ性材料またはドナー性材料を含有するコンタクト層19を設けた。有機半導体層17の導電型がp型である場合には、コンタクト層19にはアクセプタ性材料が含有されている。コンタクト層19は、有機半導体層17と同一のパターン形状を有している。

(もっと読む)

半導体装置およびプラズマディスプレイデバイス

【課題】寄生抵抗が小さく、かつ電流駆動能力が大きい高耐圧ハイブリッドトランジスタのような半導体装置の構造を提供する。

【解決手段】第1導電型の半導体層22に第1導電型のベース領域9を備える。ベース領域9には第2導電型のエミッタ領域10が設けられる。半導体層22にはベース領域9に隣接して半導体層22の表面から半導体層22の厚さより小さい所定深さにわたって第2導電型の不純物層23が設けられる。不純物層23にはベース領域9から離間して第1導電型のコレクタ領域11および第2導電型のドレイン領域14が設けられる。半導体層22の表面上には、エミッタ領域10の端部上、ベース領域9上および不純物層23上の一部にわたってゲート絶縁膜12を介してゲート電極13が設けられる。エミッタ領域10とベース領域9とに共通接続された第1電極15と、コレクタ領域11とドレイン領域14とに共通接続された第2電極16とを備える。

(もっと読む)

有機トランジスタ

【課題】

高い移動度、大きな電流オン/オフ比を有し、保存安定性に優れた有機トランジスタを提供する。

【解決手段】

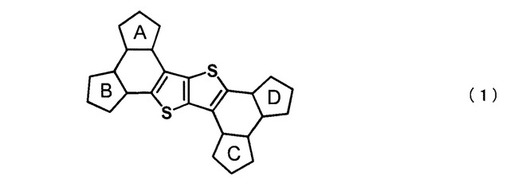

有機半導体層を有する有機トランジスタにおいて、該有機半導体層に一般式(1)で表される少なくとも1種の化合物を含有してなる有機トランジスタ。

(式中、環A〜環Dは、それぞれ独立に、置換または未置換のチオフェン環を表す。)

(もっと読む)

トランジスタ、その製造方法及び回路基板

【課題】溝を有さないゲート絶縁膜から形成されたトランジスタと比べて電界効果移動度が良好なトランジスタ、その製造方法及び回路基板を提供する。

【解決手段】トランジスタ1は、基板10と、基板10の表面に形成されたゲート電極12と、基板10上にゲート電極12を覆うように形成され、表面に複数の溝140を有するゲート絶縁膜14と、ゲート絶縁膜14の各溝140の底部142に接するように形成されたソース電極16及びドレイン電極18と、ソース電極16及びドレイン電極18に接触するとともにゲート絶縁膜14の底部142を含む表面に形成された半導体膜としての有機半導体膜20とを備えて概略構成されている。

(もっと読む)

フルオレンおよびアリール基を含むモノマー、オリゴマーおよびポリマー

【課題】合成するのが容易であり、高い電荷移動度を有し、半導体デバイス用の薄い、大面積のフィルムを形成するために容易に加工可能である、半導体または電荷輸送材料として用いるための新規な材料を提供する。

【解決手段】本発明は、少なくとも1つの9−H,H−フルオレン基および少なくとも1つのアリーレン基を含むモノマー、オリゴマーまたはポリマーに関する。本発明はさらに、これらの製造方法、電界効果トランジスタ、エレクトロルミネセント、光起電およびセンサーデバイスを含む光学、電気光学または電子デバイスにおける半導体または電荷輸送材料としてのこれらの使用に関する。本発明はさらに、新規な材料を含む電界効果トランジスタおよび半導電性部品に関する。

(もっと読む)

記憶装置及びデータ書き込み方法

【課題】メモリを他の機能回路と同一の基板上に作製した時にも、メモリのための仕様の限定を生じず、生産性を向上し、使用者にとって使いやすく、安価な記憶装置を提供する。

【解決手段】絶縁表面上に、第1乃至第5の領域を有する半導体膜と、絶縁膜と、第1の電極と、第2の電極とを含むメモリセルを有し、第2の領域は第1の領域と第3の領域の間に設けられ、第4の領域は第3の領域と第5の領域の間に設けられ、第1の電極は絶縁膜を介して第2の領域と重なって設けられ、第2の電極は絶縁膜を介して第4の領域と重なって設けられ、メモリセルは、書き込み処理時に第1の領域及び第5の領域のうち少なくとも一方の領域と、第1の電極及び第2の電極との間に電圧を印加して第2の領域及び第4の領域のうち少なくとも一方の領域の半導体膜を絶縁状態に変化させる。

(もっと読む)

有機半導体材料およびこれを用いた有機薄膜トランジスタ

【課題】汎用溶媒に対する溶解性が非常に高く、湿式成膜が可能な低コストプロセスに適応可能であり、さらに、容易に均質性の高い薄膜を得ることが可能な有機エレクトロニクス用材料として有用なオリゴチオフェン類からなる有機半導体材料およびこれを用いた有機薄膜トランジスタを提供する。

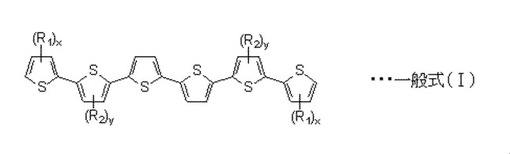

【解決手段】下記一般式(I)で表わされることを特徴とする有機半導体材料。

(式中、R1およびR2は、互いに異なるアルキル基を表わし、xおよびyは、それぞれ独立に1または2の整数を表わす。)

(もっと読む)

アンタントレン系化合物及び半導体装置

【課題】半導体層を構成する有機半導体材料として、安定性が良好であるアンタントレン系化合物を提供。

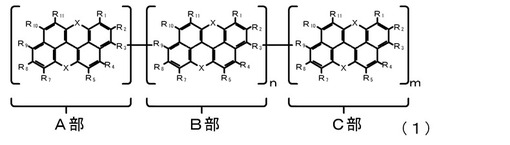

【解決手段】大気中での安定性が良好である構造式(1)で表されるオリゴ・ジカルコゲノ・アンタントレン系化合物。

ここで、Xは第16族元素を示し、nは0乃至20の整数を表し、mは1乃至9の整数を表し、置換基R1,R2,R3,R4,R5,R7,R8,R9,R10及びR11は、それぞれ、独立に、水素原子、アルキル基、アリール基、アリールアルキル基等から成る群から選択された1種類の置換基。

(もっと読む)

SOI基板の作製方法

【課題】単結晶シリコン基板よりも大面積な基板に、均一な質を有する複数の単結晶半導体層を貼り付けたSOI基板の作製方法を提供することを課題とする。

【解決手段】熱処理において、ベース基板支持及び単結晶半導体基板保持のトレイとして、凹部の底が深く、ベース基板に貼り付けられた単結晶半導体基板と接触しないトレイを用いて、単結晶半導体基板の熱分布の均一化を図る。また、該トレイの各々の凹部の間にベース基板支持部を設けることによって、該トレイとベース基板との接触面積を低減する。以上より、単結晶半導体基板から単結晶半導体層を分離する熱処理の際、単結晶半導体基板及びベース基板の熱分布が均一になるようにする。

(もっと読む)

半導体装置及び電子機器

【課題】回路面積が小さい、またはトランジスタの劣化を防止するよう形成された、有機トランジスタと無機トランジスタとを備えた半導体装置を提供する。

【解決手段】本発明の一形態の半導体装置としてのCMOS回路は、(a)基板100と、(b)有機半導体層106aを含むp型有機トランジスタPTと、(c)p型有機トランジスタPTの上層に設けられた無機半導体層126aを含むn型無機トランジスタNTと、を備える。さらに、n型無機トランジスタNTのチャネル領域126は、p型有機トランジスタPTのチャネル領域106と、平面視において少なくとも部分的に重なっている。

(もっと読む)

半導体装置及び高周波スイッチ回路

【課題】高周波入力に対して低歪みの半導体装置及び高周波スイッチ回路を提供する。

【解決手段】本発明の半導体装置は、絶縁層12上に第2導電型の第3の半導体領域15に接して設けられた第2導電型の第4の半導体領域16と、第3の半導体領域15及び第4の半導体領域16上に設けられた絶縁膜17と、絶縁膜17上に設けられたゲート電極18と、第4の半導体領域16と電気的に接続され直流電圧が印加されるボディ電極23と、を備え、ゲート電極18に閾値電圧以上の電圧が印加されたオン状態で、第4の半導体領域16が空乏化して、ボディ電極23と第3の半導体領域15との間の直流の通過を遮断する。

(もっと読む)

ポリシルセスキオキサン薄膜への有機半導体膜の製膜方法

【課題】有機半導体の特性低下を招くことなく、ポリシルセスキオキサン薄膜に有機半導体膜を均一に製膜する方法を提供する。

【解決手段】フェニル基修飾コロイダルシリカを含有する有機半導体溶液をポリシルセスキオキサン薄膜上に塗布し、塗膜を乾燥させることを特徴とする、ポリシルセスキオキサン薄膜への有機半導体膜の製膜方法。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供する。

【解決手段】基板301上にゲート電極303を形成し、ゲート電極303を覆ってゲート絶縁膜304を形成し、ゲート絶縁膜304上に酸化物半導体膜305を形成し、酸化物半導体膜305上に第1の導電膜306及び第2の導電膜307を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも加熱処理LRTAにより結晶化した領域308を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】低い電源電圧を昇圧させる回路に用いられるスイッチング素子となるトランジスタは、停止時には高い閾値電圧の特性によりリーク電流を防止して変換効率を高め、駆動時には低い閾値電圧の特性により高い電圧に昇圧できることが望まれている。

【解決手段】半導体装置であるトランジスタは、埋め込み酸化膜を用いたSOIトランジスタ構造を持ち、トランジスタのソース・ドレイン領域の外周部の基板部分を埋め込み酸化膜よりも厚い絶縁体層で囲み、且つゲートに入力される信号がバックゲートバイアスで印加される構成により、駆動時には低い閾値により高い昇圧を実現し、停止時には高い閾値によりリーク電流を防止する。

(もっと読む)

141 - 160 / 665

[ Back to top ]